- •Вказівки до виконання лабораторних робіт 3 і 4

- •1 Лист 6 . Обчислювальна система з буферною пам'яттю даних.

- •1.1. Опис системи.

- •1.2. Робота обчислювальної системи з буферною пам'яттю даних.

- •1.3. Алгоритми обслуговування буферної пам'яті даних.

- •2 Лист 6 . Обчислювальна система з асоціативною пам'яттю.

- •2.1. Опис системи.

- •2.2. Робота обчислювальної системи з асоціативною пам'яттю.

- •3. Формати слів даних

- •4. Опис команди і набір команд.

- •1. Арифметичні команди, призначені безпосередньо для обчислення.

- •2. Команди управління, призначені для організації циклів і галужень.

- •5. Графічне представлення команд

- •6. Асемблер обчислювальної системи

- •6.1 Команди і їх опис

- •6.2 Формальний опис мови програмування:

- •6.3 Приклад програми на асемблері циклів і умовних переходів з прикладу

- •7. Приклад програмування послідовно-паралельних алгоритмів

- •Приклад

- •8. Приклад програмування циклів і умовних переходів

- •Приклад

- •9. Лабораторний практикум

- •9 Лист 6 .1 Завдання на лабораторну роботу №3.

- •9 Лист 6 .2 Завдання на лабораторну роботу №4.

- •Кількість ітерацій

- •Пристрій виводу

Вказівки до виконання лабораторних робіт 3 і 4

Зміст:

1. Обчислювальна система з буферною пам'яттю даних. 2

1.1. Опис системи. 2

1.2. Робота обчислювальної системи з буферною пам'яттю даних. 3

1.3. Алгоритми обслуговування буферної пам'яті даних. 4

2. Обчислювальна система з асоціативною пам'яттю. 5

2.1. Опис системи. 5

2.2. Робота обчислювальної системи з асоціативною пам'яттю. 5

3. Формати слів даних 7

4. Опис команди і набір команд. 7

5. Графічне представлення команд 8

6. Асемблер обчислювальної системи 10

6.1 Команди і їх опис 10

6.2 Формальний опис мови програмування: 10

6.3 Приклад програми на асемблері циклів і умовних переходів з прикладу 11

7. Приклад програмування послідовно-паралельних алгоритмів 12

8. Приклад програмування циклів і умовних переходів 13

9. Лабораторний практикум 16

9.1 Завдання на лабораторну роботу №3. 16

9.2 Завдання на лабораторну роботу №4. 18

1 Лист 6 . Обчислювальна система з буферною пам'яттю даних.

1.1. Опис системи.

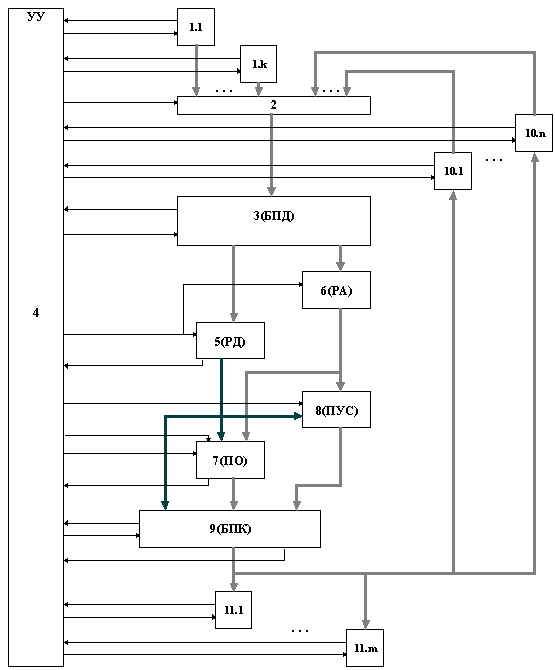

Обчислювальна система містить пристрої 1.1,...,1.k введення даних, інформаційні входи яких через відповідні входи комутатора 2 підключено до блоку 3 буферну пам'ять даних, кожен пристрій 1.1,...,1.k введення сполучений з блоком 4 управління входом і виходом, а комутатор 2 — керуючими входами. (рис. 1)

рис1. Обчислювальна система з буферною пам'яттю даних.

Керуючі входи блоку 3 буферної пам'яті даних, які забезпечують занесення інформації і просування черги, підключено до входів блоку 4 управління, відповідні входи яких сполучені з виходами сигналу блока 3 буферної пам'яті даних, що характеризує ступінь його заповнення (“буфер зайнятий”, ”буфер порожній”). З інформаційним входом регістра 5 даних і регістра 6 адреси підключені відповідно перша і друга групи інформаційних виходів блоку 3 буферної пам'яті даних. Керуючі входи занесення інформації регістра 6 адреси і регістра 5 даних сполучено з виходами блоку 4 управління, а вихід одного розряду регістра 5 даних (ознака типу інформації) підключений до відповідного входу блоку 4 управління. Інформаційні виходи регістра 6 адреси пов'язані з адресними входами блока 7 пам'яті операндів, і блоку 8 пам'яті керуючих слів. Інформаційні виходи регістра 5 даних до входів даних блоку 7 пам'яті операндів, блоку 8 пам'яті керуючих слів і першій групі інформаційних входів 9 буферній пам'яті команд. Друга і третя групи інформаційних входів 9 буферній пам'яті команд сполучені відповідно з виходами даних блоку 7 пам'яті операндів і блоку 8 пам'яті керуючих слів. Входи управління записом і читанням блока 7 пам'яті операндів і блока 8 пам'яті керуючих слів підключені відповідні виходи блоку 4 управління. Один вихід блоку 4 управління підключений до входу одного розряду даних блока 7 пам'яті операндів, вихід однойменного розряду даних якого сполучений з одним входам блоку 4 управління. До відповідних входів блоку 4 управління підведено виходи сигналів блоку буферної пам'яті команд 9, вказуючих на ступінь його заповнення, а також виходи групи розрядів, що характеризують тип команди і номер пристрою висновку. Керуючі входи запису і просування по черзі (читання) блоку 9 буферній пам'яті команд пов'язано з відповідними входами блоку 4 управління. Інформаційні виходи блоку 9 буферній пам'яті команд підключені до інформаційних входів обчислювальних блоків 10.1..., 10.n і інформаційним входам пристроїв виведення даних 11.1,...,11.m, керуючі входи і керуючі виходи яких підключені до відповідних входів і виходів блоку 4 управління. Інформаційні виходи кожного обчислювального блоку 10.1..., 10.n сполучені відповідні групи інформаційних входів комутатора 2.