- •Многоуровневая организация цифровой вычислительной системы

- •Состояние и перспективы развития элементной базы современных вычислительных систем

- •Логические элементы

- •Функциональные узлы комбинационного типа

- •Дешифратор (Decoder, dc)

- •Мультиплексор (mux)

- •Демультиплексор

- •Компаратор (cmp)

- •Многоразрядный комбинационный сумматор

- •Многоразрядные сумматоры

- •Арифметико-логическое устройство (алу, Arithmetic-Logic Unit, alu)

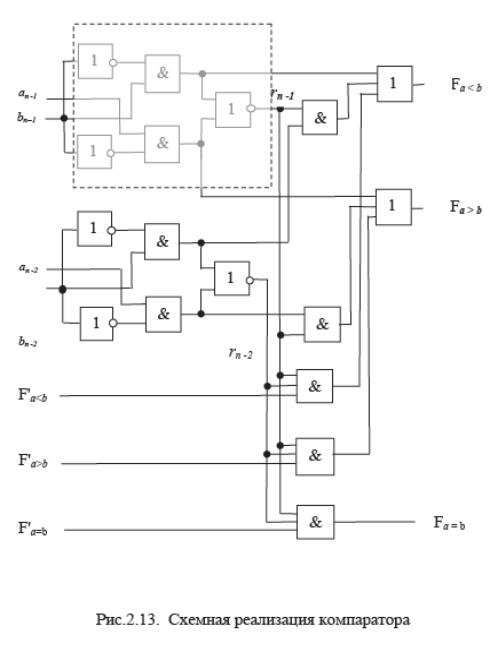

Компаратор (cmp)

Это устройство, выполняющее функции сравнения двух слов. Для слов a = an an-1 ….. a0 и b = bn bn-1 ….. b0 компаратор определяет три типа отношений:

отношение равенства Fa = b

отношение «больше» Fa > b

отношение «меньше» Fa < b

Схемная реализация компаратора в соответствии с приведенными выше формулами представлена на рис.2.13.

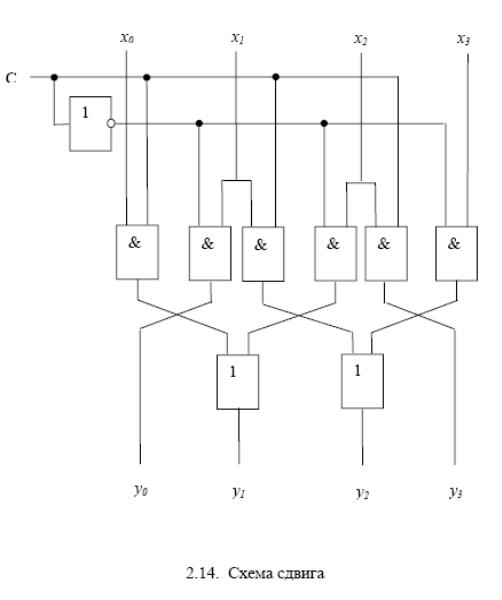

Схема сдвига

Cдвигает код на один разряд влево или вправо в зависимости от заданного сигнала управления С=0 или С=1, соответственно. Пример реализации схемы для случая четырех входных битов приведен на рис.2.14.

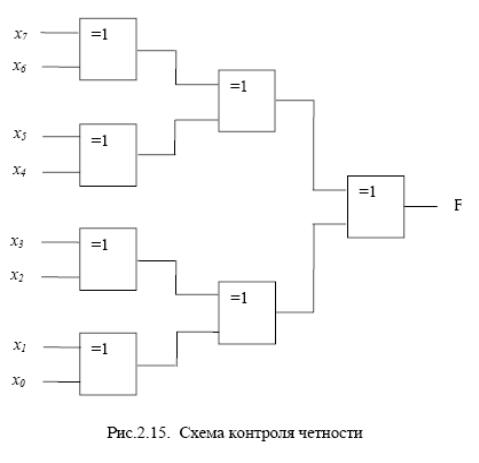

Схема контроля четности

Выполняет функцию проверки поступающего на ее n входов двоичного кода xn-1 xn-2 … x0 на присутствие в нем четного (нечетного) числа единиц. Схема реализует сумматор по модулю 2 битов входного кода, формируя на выходе «1», если число единиц во входном коде нечетное, и «0», если число единиц четное.

Реализация восьмивходовой схемы контроля четности на базе XOR-элементов представлена на рис.2.15. XOR-элемент, обозначаемый символом «=1», в свою очередь может быть построен по схеме, обведенной пунктиром на рис.2.13 (с исключением инверсии на выходе).

Сумматор осуществляет арифметическое сложение двух целых чисел. Накапливающий сумматор поданное на его вход число суммирует к хранящемуся в его памяти предыдущему результату. Комбинационный сумматор не имеет памяти и формирует на выходе результат сложения поданных на его вход двух чисел.

Многоразрядный комбинационный сумматор

Складывается из одноразрядных сумматоров. Одноразрядный комбинационный сумматор имеет три входа ai , bi (соответствующие разряды складываемых чисел), pi-1 (сигнал переноса из соседнего младшего разряда) и два выхода si (соответствующий разряд суммы), pi (сигнал переноса в соседний старший разряд).

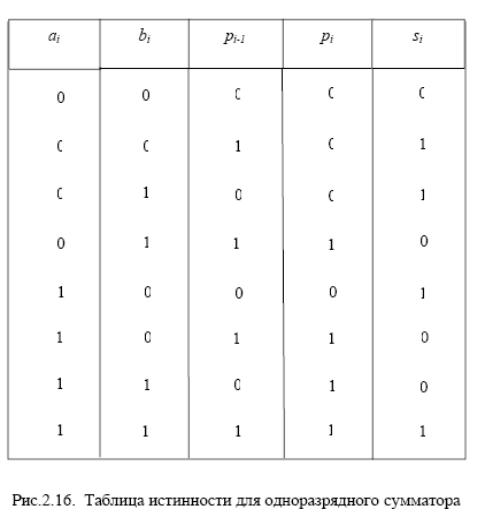

Соотношение значений входных и выходных сигналов описываются таблицей истинности, представленной на рис.2.16.

По таблице истинности легко построить логические функции для выходов сумматора:

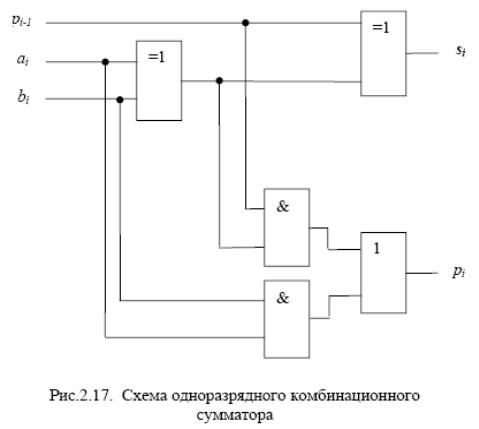

Схемная реализация полученных логических функций представлена на рис.2.17. Условное обозначение одноразрядного комбинационного сумматора изображено на рис.2.18.

Многоразрядные сумматоры

Многоразрядные сумматоры, формируемые из одноразрядных, по принципу организации переноса подразделяются на сумматоры с последовательным (сквозным), параллельным и комбинированным переносом.

Сумматор с последовательным переносом строится путем последовательного соединения по цепям переноса необходимого числа одноразрядных сумматоров (рис.2.19).

У сумматора с последовательным переносом время суммирования определяется временем распространения сигнала переноса через всю схему. Поэтому с увеличением разрядности сумматора его быстродействие снижается.

Максимально увеличить быстродействие позволяет сумматор с параллельным переносом (рис.2.20). Составляющие его одноразрядные сумматоры работают одновременно, получая входные сигналы переноса от специальной схемы, называемой схемой ускоренного переноса. Эта схема формирует сигналы переноса во все разряды одновременно.

Схемы управления переносом для сумматоров с числом разрядов более четырех оказываются очень громоздкими. Для достижения приемлемого компромисса между быстродействием и аппаратной сложностью применяются схемы комбинированного переноса. Это так называемые сумматоры групповой структуры. В них схема общей разрядности n делится на k групп разрядности m (n = k m). Внутри групп и между группами могут использоваться различные виды переносов.