- •1Выбор и обоснование структурной схемы коммутатора

- •2Выбор серии имс

- •3Разработка электрической принципиальной схемы коммутатора

- •3.1Порядок разработки электрической схемы

- •3.2Разработка схемы электрической принципиальной коммутатора входов

- •3.3Разработка схемы электрической принципиальной коммутатора выходов

- •3.4Разработка схемы электрической принципиальной устройства управления

- •4Расчет тактового генератора

- •5Моделирование электронного коммутатора

3Разработка электрической принципиальной схемы коммутатора

3.1Порядок разработки электрической схемы

Разработку схемы электрической принципиальной, проведем в следующей последовательности:

1) разработка схемы электрической принципиальной коммутатора входов;

2) разработка схемы электрической принципиальной коммутатора выходов

3) разработка схемы электрической принципиальной устройства управления.

3.2Разработка схемы электрической принципиальной коммутатора входов

Для построения коммутатора входов используем мультиплексор, который позволяет осуществить коммутацию одного из входов с выходом, Коммутируемый вход определяется кодом, поданным па адресные входы мультиплексора.

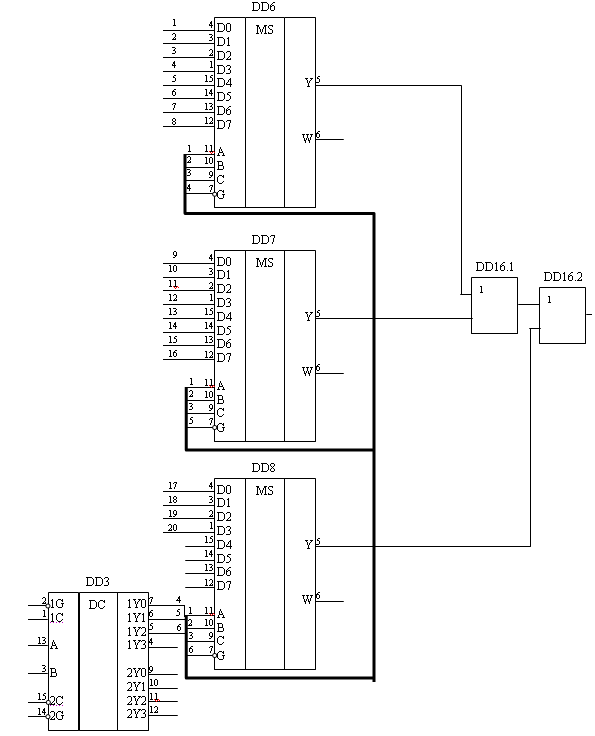

В соответствии с данными справочника по цифровым ИМС [5, 11] выбираем мультиплексор так, чтобы обеспечить, необходимое число входов при наименьшем числе ИМС. Выбранные мультиплексоры объединяются в единый коммутатор входов, используя стробирующие входы. Для реализации мультиплексора применим ИМС мультиплексор 8 в 1 с 3 состояниями, прямым и инверсным выходами К555КП15. Для коммутации 20 входов потребуется 3 мультиплексора (так как один мультиплексор содержит 8 входов). Схема мультиплексора представлена на рисунке (Рис. 3 .2).

Рис. 3.2 Схема мультиплексора

3.3Разработка схемы электрической принципиальной коммутатора выходов

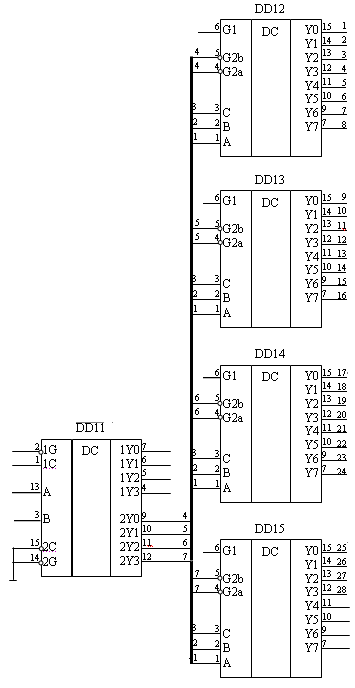

Для построения коммутатора выходов используем демультиплексор, который позволяет соединить вход с одним из выходов, адрес которого задан кодовой комбинацией на адресных входах демульгиплексора. В качестве демультнплексора используем дешифратор со стробирующим входом 3 в 8 со стробом и логикой К555ИД7. Выбираем по справочнику [5, 11] депшфраторы-демультиплексоры так, чтобы их количество позволяло реализовать заданное количество выходов . Так как ИМС К555ИД7 содержит 8 выходов, то для реализации 28 выходов необходимо 4 микросхемы.

Используя выбранные дешифраторы, проектируем демультиплексор на 28 выводов но принципу каскадного дешифратора (Рис. 3 .3).

3.4Разработка схемы электрической принципиальной устройства управления

Устройство управления должно обеспечить заданный алгоритм (порядок) коммутации входов с выходами.

Порядок разработки устройства управления рекомендуется вести в следующей последовательности:

разработка схемы управления, реализующей алгоритм –коммутации ходов;

разработка схемы управления, реализующей алгоритм коммутации выходов;

обеспечение совместной работы разработанных устройств управления в соответствии с общим алгоритмом коммутации.

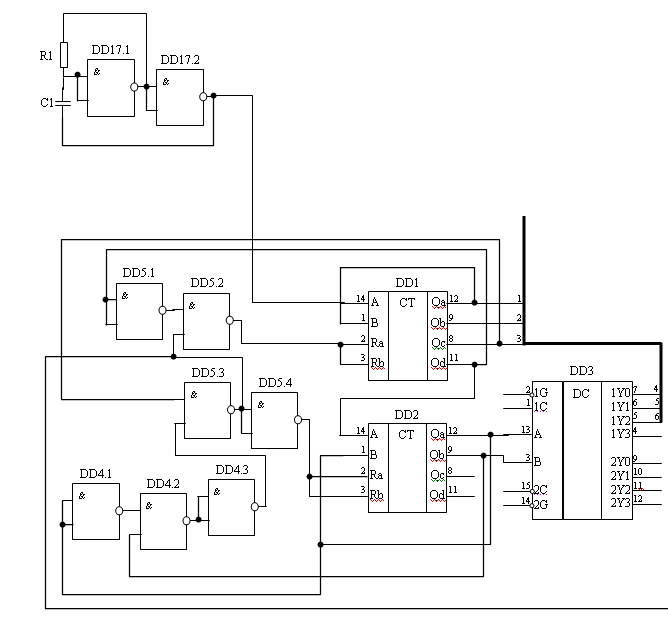

Чтобы обеспечить заданную последовательность коммутации входов, необходимо подавать на адресные входы мультиплексора последовательность кодовых комбинации в соответствии и работой суммирующего счетчика с коэффициентом пересчета равным 20. Для этой цели выбираем два 4-разрядных двоичных счетчика К555ИЕ5 (Рис. 3 .4).

Схема работает следующим образом. Импульсы синхронизации поступают с генератора DD17 поступают на вход А счетчика DD1, на выходе которого генерируется номер входа коммутатора. Счетчик DD1 работает совместно со счетчиком DD2, на выходе которого генерируется номер микросхемы мультиплексора.

Рис. 3.3. Схема демультиплексора (каскадного дешифратора)

Таким образом, счетчик DD1 имеет коэффициент пересчета равным 8 (по количеству входов в каждой микросхеме), а счетчик DD2 имеет коэффициент пересчета 3 (по количеству микросхем мультиплексоров).

Рис. 3.4. Схема управления коммутатором входов

Схема сброса счетчиков DD1 и DD2, реализована на логических элементах DD4 и DD5. Счетчик DD1 сбрасывается в том случае, когда выход Qd=1 или одновременно со счетчиком DD2. Счетчик DD2 сбрасывается в том случае, когда выход Qc=1 счетчика DD1 и Qa=0 и Qb=1 счетчика DD2. Сигналы с выходов счетчика DD1 поступают на адресные входы мультиплексоров, а сигналы с выходов DD2 поступают в дешифратор DD3, на выходе которого формируется сигнал выбора микросхемы мультиплексора.

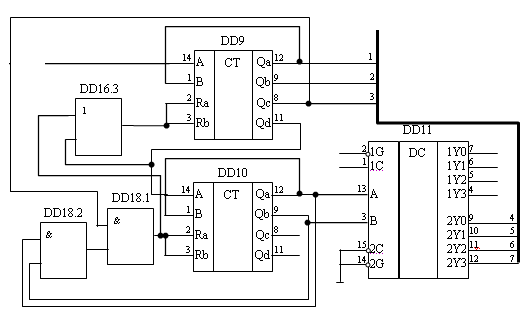

Для построения устройства управления, реализующего алгоритм коммутации выходов также используем два 4-разрядных двоичных счетчика К555ИЕ5 (Рис. 3 .5).

Рис. 3.5. Схема управления коммутатором выходов

Сигнал от схемы сброса счетчиков DD1 и DD2, поступает на вход счетчика DD9. Схема счетчика выходов реализована аналогично схеме входов. На выходе счетчика DD9 формируется адрес выхода, а на выходе счетчика DD10 формируется номер микросхемы демультиплесора на котором находится выход. Адрес микросхемы демультиплексора поступает на вход дешифратора DD11.

Коэффициент пересчета счетчика DD9 равен 8 (по количеству выходов микросхемы демультиплексора), коэффициент пересчета DD10 равен 4 (по количеству микросхем демультиплексоров).

Схема сброса реализована на логических элементах DD16.3 и DD18. Счетчик DD9 сбрасывается в том случае если на выходе Qd=1 или если необходимо сбросить DD10. Счетчик DD10 сбрасывется в том случае, если выход Qc=1 счетчика DD9 и выходы Qa=1 и Qb=1 счетчика DD10.

Алгоритм работы схемы можно пояснить таблицей (Таблица 3 .3).

Таблица 3.3

Вход |

Выход |

||||

Номер входа |

Номер микросхемы |

Номер входа микросхемы |

Номер выхода |

Номер микросхемы |

Номер выхода микросхемы |

1 |

DD6 |

D0 |

28 |

DD12 |

Y0 |

2 |

DD6 |

D1 |

28 |

DD12 |

Y0 |

3 |

DD6 |

D2 |

28 |

DD12 |

Y0 |

… |

… |

… |

… |

… |

… |

20 |

DD8 |

D3 |

28 |

DD12 |

Y0 |

1 |

DD6 |

D0 |

27 |

DD12 |

Y1 |

2 |

DD6 |

D1 |

27 |

DD12 |

Y1 |

3 |

DD6 |

D2 |

27 |

DD12 |

Y1 |

… |

… |

… |

… |

… |

… |

20 |

DD8 |

D3 |

27 |

DD12 |

Y1 |

… |

… |

… |

… |

… |

… |

1 |

DD6 |

D0 |

1 |

DD15 |

Y3 |

2 |

DD6 |

D1 |

1 |

DD15 |

Y3 |

3 |

DD6 |

D2 |

1 |

DD15 |

Y3 |

… |

… |

… |

… |

… |

… |

20 |

DD8 |

D3 |

1 |

DD15 |

Y3 |