3. ЦИФРОВЫЕ СХЕМЫ С ПАМЯТЬЮ

3.1. Общие сведения об элементарных автоматах с памятью

Для представления и обработки информации в цифровых системах возникает потребность в устройстве, которое может хранить логическое состояние (0 или 1) неопределенно долго. Такие устройства образуют элементарную разновидность памяти, а поскольку их выход может находиться в одном из двух устойчивых состояний, их называют бистабильными схемами или триггерами.

Интегральные триггеры обычно реализуются на логических элементах И-НЕ, ИЛИ-НЕ. Таблицы истинности для логических элементов И-НЕ и ИЛИ-НЕ приведены соответственно на рис. 3.1 a,б.

-

X1

X2

F (X1,X2)

X1

X2

F (X1,X2)

0

0

1

1

0

1

0

1

1

1

1

0

0

0

1

1

0

1

0

1

1

0

0

0

a) б)

Рисунок 3.1 - Логические элементы И-НЕ, ИЛИ-НЕ и их таблицы истинности

Легко убедиться, что каждый из этих элементов характеризуется некоторым логическим уровнем (лог.0 или 1), действие которого на одном из входов полностью определяет логический уровень на выходе. При этом логический уровень на выходе элемента не изменяется, какие бы комбинации логических уровней не подавались на другие входы этого элемента. Такими логическими уровнями для элементов И-НЕ являются уровень лог.0, а для ИЛИ-НЕ уровень лог.1. Действительно, если на один из входов элемента И-НЕ подан лог.0, то на выходе этого элемента возникает лог.1 независимо от того, каковы логические уровни на других входах; лог.1, поданная на один из входов элемента ИЛИ-НЕ, установит на выходе уровень лог.0, который не будет зависеть от логических уровней, действующих на других входах элемента.

Такие логические уровни, которые действуют на одном из входов элемента, однозначно задают логический уровень на его выходе независимо от уровней на других входах, будем называть активными логическими уровнями. Таким образом, активный логический уровень для элементов И-НЕ - уровень лог.0, а для элементов ИЛИ-НЕ - уровень лог.1.

Так как при подаче активного логического уровня на один из входов элемента он и определяет уровень на выходе элемента (выходной уровень элемента при этом не зависит от уровней на других входах), можно говорить, что, при этом происходит логическое отключение остальных входов элемента. Уровни, обратные активным, будем называть пассивными логическими уровнями. Пассивными уровнями для элементов И-НЕ служат уровень лог.1, а для ИЛИ-НЕ - уровень лог.0. При действиях на одном из входов пассивного логического уровня уровень на выходе элемента определяется логическими уровнями на других его входах.

Пользуясь понятиями активного и пассивного логических уровней, проведем анализ функционирования триггеров, построенных на элементах И-НЕ и ИЛИ-НЕ.

Слово

«триггер» по-английски означает спусковое

устройство, курок. Триггером называется

устройство с двумя возможными устойчивыми

состояниями, в которое он может

устанавливаться управляющими входными

сигналами. Существует большое количество

разновидностей триггеров, которые

различаются по виду входных и выходных

сигналов, а также по способу управления

состоянием записи информации в триггер.

Наибольшее распространение в цифровой

электронике получили статические

триггеры, которые имеют два состояния,

представленные потенциальными сигналами:

одно из них обозначается как состояние

лог.0, другое - лог.1. Воздействуя на входы

триггера, его устанавливают в нужное

состояние. Триггер имеет два выхода:

прямой Q и инвертный

![]() и различные типы входов. Например, вход

R - вход установки триггера в состояние

0, и вход S - установки в состояние 1.

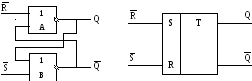

Логические структуры триггера и условное

обозначение согласно ГОСТу на элементах

ИЛИ-НЕ представлена на рис.3.2a,б. Схема

триггера состоит из двух логических -

элементов ИЛИ-НЕ, связанных таким

образом,

что выход каждого элемента подключен

к одному из входов другого. Такое

соединение элементов в устройстве

обеспечивает два устойчивых состояния,

в чем легко убедиться.

и различные типы входов. Например, вход

R - вход установки триггера в состояние

0, и вход S - установки в состояние 1.

Логические структуры триггера и условное

обозначение согласно ГОСТу на элементах

ИЛИ-НЕ представлена на рис.3.2a,б. Схема

триггера состоит из двух логических -

элементов ИЛИ-НЕ, связанных таким

образом,

что выход каждого элемента подключен

к одному из входов другого. Такое

соединение элементов в устройстве

обеспечивает два устойчивых состояния,

в чем легко убедиться.

а) б)

Рисунок 3.2 - Логическая структура триггера на элементах ИЛИ-НЕ

и его условное графическое обозначение

Пусть

на входах R и S действуют постоянные для

элементов ИЛИ-НЕ уровни лог.0, которые

не влияют на состояние триггера. В

состоянии 0 триггера на выходе элемента

А Q = 0. Этот уровень подается на вход

элемента В, при этом на обоих входах

элемента В действует уровень лог.0 и на

выходе элемента

![]() = 1. С выходом элемента В уровень лог.1

поступает на вход элемента А, что и

обеспечивает на его выходе уровень 0.

Это одно из устойчивых состояний

триггера. В состоянии 1 триггера на

выходе элемента А Q = 1, что обуславливает

на выходе элемента В

= 1. С выходом элемента В уровень лог.1

поступает на вход элемента А, что и

обеспечивает на его выходе уровень 0.

Это одно из устойчивых состояний

триггера. В состоянии 1 триггера на

выходе элемента А Q = 1, что обуславливает

на выходе элемента В![]() = 0, при этом на обоих выходах элемента

А действуют уровни 0, что и обеспечивает

на выходе этого элемента уровень лог.1.

Анализ работы триггера показал, что в

каждом из состояний триггера элементы

А и В оказываются в противоположных

состояниях.

= 0, при этом на обоих выходах элемента

А действуют уровни 0, что и обеспечивает

на выходе этого элемента уровень лог.1.

Анализ работы триггера показал, что в

каждом из состояний триггера элементы

А и В оказываются в противоположных

состояниях.

Переключение

триггера из одного устойчивого состояния

в другое происходит при подаче активных

сигналов на его входы. Под действием

уровня R = 1 элемент А установится в

состояние, при котором на его выходе Q

=

![]() ,

следовательно, на инверсном выходе

,

следовательно, на инверсном выходе![]() = 1, и, таким образом, триггер устанавливается

в состояние 0. Если триггер и прежде, до

подачи сигнала R = 1, находился в состоянии

0, то его состояние не изменится, если

же триггер находился в состоянии 1, то

при подаче сигнала R = 1 произойдет

переключение элемента А, и на его выходе

установится уровень

Q = 0, далее этот

уровень действует на входе элемента В,

переключает его и на выходе элемента В

установится уровень Q = 1, после чего

триггер оказывается установленным.

Таким образом, при переключении триггера

из одного состояния в другое его элементы

последовательно

переключаются и время переключения

равно удвоенному среднему времени

задержки распространения сигнала в

логическом элементе ИЛИ-НЕ

= 1, и, таким образом, триггер устанавливается

в состояние 0. Если триггер и прежде, до

подачи сигнала R = 1, находился в состоянии

0, то его состояние не изменится, если

же триггер находился в состоянии 1, то

при подаче сигнала R = 1 произойдет

переключение элемента А, и на его выходе

установится уровень

Q = 0, далее этот

уровень действует на входе элемента В,

переключает его и на выходе элемента В

установится уровень Q = 1, после чего

триггер оказывается установленным.

Таким образом, при переключении триггера

из одного состояния в другое его элементы

последовательно

переключаются и время переключения

равно удвоенному среднему времени

задержки распространения сигнала в

логическом элементе ИЛИ-НЕ

tпер = 2tзад.р.ср.

Очевидно, чем меньше tзад.р.ср., тем больше число переключений триггера можно произвести в единицу времени, т.е. будет выше допустимая частота переключений или, иначе говоря, быстродействие триггера. Процесс установки триггера в состояние 1 при подаче на вход S уровня лог.1 аналогичен описанному.

Одновременная подача активных уровней 1 на оба входа R и S не допускается, так как при этом на обоих выходах установится уровень 0, а после снятия его со входов активных уровней состояние триггера окажется неопределенным: в силу случайных причин триггер можно установить в состояние 0 либо 1. По каждому из входов триггер переключается сигналами 1 ( рис.3.3 ).

Рисунок 3.3 - Временные диаграммы триггера, реализованного

на элементах ИЛИ-НЕ

Логическая структура триггера и условное обозначение согласно ГОСТу на элементах И-НЕ приведены на рис.3.4.

a) б)

Рисунок 3.4 - Логическая структура и условное графическое

обозначение триггера на элементах И-НЕ

Отличие от логической структуры триггера на рис.3.4, реализованного на элементах ИЛИ-НЕ, состоит лишь в том, что здесь использованы логические элементы И-НЕ.

При

этом активным логическим уровнем на

входах является уровень лог.0, пассивным

- лог.1. Для того чтобы активными были

как и в предыдущем триггере, входные

сигналы S = 1 и в R = 1, будем считать, что

на входы подаются инверсии

![]() и

и

![]() .

Тогда при S = 1 (или R = 1)

.

Тогда при S = 1 (или R = 1)

![]() = 0 (или

= 0 (или

![]() = 0) и на выходе триггера будет действовать

активный уровень лог.0.

= 0) и на выходе триггера будет действовать

активный уровень лог.0.

Рассмотрим

устойчивые состояния триггера. Пусть

на входах действуют пассивные уровни

S = 0 и R = 0 (![]() = 1 и

= 1 и

![]() = 1). В состоянии 0 триггера Q = 0, этот

уровень передается на вход элемента В

и вызывает на его выходе уровень Q = 1,

уровень 1 с выхода элемента В подается

на вход элемента А, и так как на обоих

входах элемента А уровень 1, то на выходе

этого элемента Q = 0. Аналогично определяется

устойчивое второе состояние триггера.

= 1). В состоянии 0 триггера Q = 0, этот

уровень передается на вход элемента В

и вызывает на его выходе уровень Q = 1,

уровень 1 с выхода элемента В подается

на вход элемента А, и так как на обоих

входах элемента А уровень 1, то на выходе

этого элемента Q = 0. Аналогично определяется

устойчивое второе состояние триггера.

При

подаче активного уровня

![]() = 0 (S = 1) на выходе элемента А устанавливается

уровень Q = 1, на выходе элемента В - уровень

= 0 (S = 1) на выходе элемента А устанавливается

уровень Q = 1, на выходе элемента В - уровень

![]() = 0 и триггер оказывается установленным

в состояние 1. При подаче активного

уровня

= 0 и триггер оказывается установленным

в состояние 1. При подаче активного

уровня

![]() = 0 (R = 1) триггер устанавливается в

состояние 0. Как и для триггера с прямыми

входами одновременная подача активных

уровней на оба входа не допускается. По

каждому из входов триггер переключается

сигналами 0 (рис.3.5).

= 0 (R = 1) триггер устанавливается в

состояние 0. Как и для триггера с прямыми

входами одновременная подача активных

уровней на оба входа не допускается. По

каждому из входов триггер переключается

сигналами 0 (рис.3.5).

Рисунок 3.5 - Временные диаграммы триггера, реализованного на элементах И-НЕ

Итак, триггер представляет собой элементарный цифровой автомат с памятью.

3.2. Основные типы триггеров

Триггер представляет собой устройство, логическую структуру которого в общем виде можно представить как систему, состоящую из собственно триггера и устройства управления. При этом собственно триггер играет роль ячейки памяти, а устройство управления преобразует входную информацию в комбинацию сигналов, под воздействием которых собственно триггер принимает одно из двух устойчивых состояний. Обобщенная структурная схема триггера показана на рис.3.6.

Ячейка памяти хранит информацию о результатах предыдущего воздействия на триггер. Определенная роль в формировании свойств триггерного устройства принадлежит управляющему устройству.

Рисунок 3.6 - Обобщенная структурная схема триггера

Схема управления реализует правила реагирования триггера на различные входные сигналы и их комбинации и формирует сигналы, которые обеспечивают хранение информации в ячейке памяти, подтверждение состояния либо переключение ячейки памяти в другое состояние. В двоичном триггере для схемы запоминающего элемента достаточно выработать сигналы установки в единичное состояние (установка «1») и в нулевое состояние (установка «0»), отсутствие сигналов установки соответствует режиму хранения информации, а их одновременное действие приводит к неопределенному результату, поэтому такое управление обычно не используется.

По реакции триггера на входные управляющие воздействия различают следующие виды входов:

S - вход для установки триггера в состояние «1»;

R - вход для установки триггера в состояние «0»;

D - вход для установки триггера в состояние «1» при D=1

или

«0» при D = 0 с задержкой переключения

выходов Q,

![]() по отношению ко входу D;

по отношению ко входу D;

T - вход переключателя триггера в противоположное состояние аналогично счету по модулю 2, поэтому вход T называют счетным;

JK - входы для установки и сброса триггера в состояние соответственно «1» и «0» аналогично входам S и R. Отличие состоит в том, что о дновременное возбуждение входов S и R обуславливает неопределенность перехода триггера в одно из двух возможных состояний, а одновременное возбуждение входов J и K вызывает однозначно смену состояния триггера аналогично входу Т. Действие этих входов определяется синхронизирующими сигналами;

С - вход синхронизации для точного задания моментов переключения состояний триггера;

V - вход для разрешения или запрета реагирования триггера на соответствующие управляющие входы. Обычно триггеры содержат часть из перечисленных типов входов, причем некоторые из них являются кратными. Наименование триггера определяется типом его входов. Например:

RS - триггеры с раздельными входами установки в состояние «0» и «1». RS - триггеры бывают асинхронными и синхронными, если кроме S и R имеют вход С;

D - триггеры с записью информации по одному входу D в моменты времени, определяемые синхроимпульсами С;

Т - триггеры со счетным входом;

JK - триггеры, универсальные триггеры, в которых входы J и K в отдельности реализуют раздельное управление и совместно счетный режим.

Универсальные триггеры с управляемым приемом информации по одному входу - DV - триггер. Здесь V - управляющий вход для разрешения приема либо информационных, либо тактовых сигналов. Комбинированные триггеры ( например RST, JKRS, DRS - триггеры и т.д ).

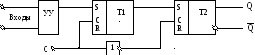

Триггер может иметь несколько одноименных входов, используемых совместно при выполнении установки. В этом случае несколько одноименных входов связаны в группы операций И или ИЛИ. Кроме названных типов существует много разновидностей триггеров с комбинированным управлением названными типами входов с синхронизацией или без нее. Триггеры, синхронизируемые уровнем синхроимпульса, могут в течение действия синхроимпульса многократно переключаться управляющими сигналами. Во многих случаях это свойство является недостатком, так как может оказаться причиной нарушения в работе. От этого недостатка свободны триггеры с дополнительным управлением. Триггеры, синхронизируемые фронтами, изменяют состояние лишь в момент переключения уровней синхроимпульса из «0» в «1» (положительный уровень) или из «1» в «0» (отрицательный уровень). При любых постоянных уровнях синхроимпульса триггер сохраняет свое состояние при всевозможных изменениях управляющих сигналов. Следовательно, синхронизируемый фронтом триггер за время действия синхроимпульса любой длительности может переключаться только один раз. Эти триггеры широко применяются на практике. Иногда используются триггеры с двойной памятью. При этом ячейки памяти состоят из двух последовательно включенных триггеров и запись информации в них происходит последовательно в различные моменты времени. Такая структура триггеров (рис. 3.7) имеет несколько названий: «ведущий - ведомый», «главный - вспомогательный», MS - структура или двухступенчатый триггер.

Рисунок 3.7 - Схема двухступенчатого триггера

Первая ступень (триггер Т1 - «ведущий») служит для предварительной установки нового состояния триггерного устройства, вторая (триггер Т2 - «ведомый») - для последовательного запоминания и хранения этого состояния триггерного устройства.

Триггеры Т1 и Т2 управляются разными фазами тактовых импульсов. При С = 0 блокируется первая ступень, а вторая открывается и информация переписывается из первой ступени во вторую и появляется на выходе. Двухступенчатые триггеры устраняют критические гонки сигналов в цифровых системах, которые могут появляться за счет разброса средней задержки распространения сигналов.

3.3. Условия функционирования элементарных автоматов с памятью

Триггерное устройство является элементарным автоматом Мура. Поэтому принципы его функционирования можно описывать всеми способами, применяемыми для описания таких автоматов. Наиболее часто функциональную зависимость между входными и выходными сигналами в двух соседних тактах n и n + 1 представляют таблицами переходов

Qn + 1 = f(Qn; An + 1; Tn + 1), (3.1)

где Qn + 1 - новое состояние триггера (соответственно новый выходной сигнал) в такте n+1;

Qn - старое состояние триггера (соответственно старый выходной сигнал), зафиксированное в n-ом такте;

An + 1 - информационные входные сигналы+, действующие на входы триггера в (n+1) такте, i = 1 до k;

Tn + 1 - тактовые сигналы, действующие на входы триггера в (n+1)-ом такте.

Тактовые сигналы Tn + 1 в таблице переходов не показаны. Поскольку выходной сигнал триггера отождествляется с его состоянием, то таблица переходов одновременно является и таблицей выходов.

Функционирование RS-триггера (рис.3.8a) описывается таблицей переходов (рис.3.8б).

-

Sn

Rn

Qn

Qn+1

Режим

0

0

0

0

Хранение

0

0

1

1

0

1

0

0

Установка «0»

0

1

1

0

1

0

0

1

Установка «1»

1

0

1

1

1

1

0

–

Запрещено

1

1

1

–

б)

Рисунок 3.8 - Условно-графическое обозначение RS - триггера

и его функционирование

Аргументами являются входные сигналы триггера на n-ом такте, предыдущее состояние триггера Qn - 1.

Минимизацию функции Qn проведем с помощью карт Карно. Функция переходов триггера RS является неполностью определенной двоичной функцией. При минимизации проведем доопределение этой функции.

Минимальная дизъюнкция нормальной формы функции Qn имеет вид

Qn

= Sn

+

![]() Qn

- 1.

(3.2)

Qn

- 1.

(3.2)

Т.е. триггер устанавливается в состояние «1» под действием входного уровня S = 1, либо остается в этом состоянии если, его прежнее состояние Q = 1. Аналогично можно получить МКНФ с доопределенными запрещенными комбинациями «логическими» нулями

Qn

=

![]() (Sn

+ Qn-1).

(3.3)

(Sn

+ Qn-1).

(3.3)

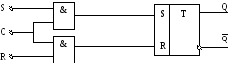

Рассмотрим синхронный RS-триггер (рис.3.9). На входах S и R включены логические элементы И. С помощью логических элементов И обеспечивается передача активных уровней информационных входов R и S синхронного триггера на входы S и R входящего в его состав асинхронного триггера только при наличии уровня лог.1 на синхронизирующем входе С.

Рисунок 3.9 - Синхронный RS - триггер

Таким образом, при С = 0 на входы асинхронного триггера не передаются активные уровни и триггер сохраняет ранее установленное в нем состояние Qn. При С = 1 состояние триггера определяется действующими на входах уровнями так же, как и в рассмотренном выше асинхронном RS-триггере.

Нормальная работа синхронного RS-триггера требует, чтобы за время действия лог.1 на синхронизирующем входе С уровни на информационных водах R и S оставались неизменными. Смена уровней на входах допускается лишь в то время, когда С = 0 и триггер не реагирует на уровни, действующие на входы S и R. На рис.3.10 показано условное изображение синхронных RS-триггеров.

ЭА должен обладать полной системой переходов, если для каждой пары его состояний аi и аj найдется хотя бы один входной сигнал, который переводит автомат из состояния аi в состояние аj. Требование полных переходов означает, что каждому из четырех его возможных пар переходов состояний (0-0, 0-1, 1-0, 1-1) должен соответствовать определенный входной сигнал.

Каждый ЭА должен обладать и полной системой выходов, если в каждом состоянии он выдает сигнал, отличный от сигналов, выдаваемых в других состояниях.

Полной системой переходов и выходов обладают все триггеры и элементы задержки.

При решении задач структурного синтеза алгоритм функционирования ЭА удобно задавать с помощью матриц переходов (таблица 3.1), имеющих в общем виде следующую структуру:

Таблица 3.1

-

Q(t)

—

Q(t + 1)

q0

q1

qθ

0

0

1

1

—

—

—

—

0

1

0

1

α00(0)

α01(0)

α10(0)

α11(0)

β00(1)

β01(1)

β10(1)

β11(1)

γ00(θ)

γ 01(θ)

γ 10(θ)

γ 11(θ)

Каждая строка матрицы соответствует одному из четырех возможных переходов ЭА из состояния Q(t) в состояние Q(t+1).Число столбцов матрицы равно числу входов ЭА.

Элемент

матрицы aij(γ)

(i, j ε {0, 1}, γ =

![]() )

- это значение функции возбуждения qij

по входу γ ЭА, переводящее этот автомат

из состояния i в состояние j. Значение

элементаaij(γ)

может быть неопределенным, равным 1 или

0.

)

- это значение функции возбуждения qij

по входу γ ЭА, переводящее этот автомат

из состояния i в состояние j. Значение

элементаaij(γ)

может быть неопределенным, равным 1 или

0.

Неопределенное значение элемент bij(γ) может принимать тогда, когда значение параметра e ≥ 2.

Матрицы переходов ЭА могут составляться либо по таблице переходов этих автоматов, либо непосредственно по описанию процесса их функционирования.

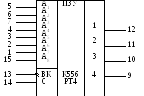

Пример. В качестве ЭА выбран RST-триггер (рис.3.10).

Рисунок 3.10 - Условное графическое изображение синхронного

двухступенчатого RS-триггера

Функция переходов RST-триггера приведена в таблице 3.2.

Таблица 3.2

-

qR(t)

qS(t)

qT(t)

Q(t)

Q(t+1)

0

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

0

1

0

0

1

0

1

0

1

1

0

1

1

0

—

0

1

1

1

—

1

0

0

0

0

1

0

0

1

0

1

0

1

0

—

1

0

1

1

—

1

1

0

0

—

1

1

0

1

—

1

1

1

0

—

1

1

1

1

—

Одновременная подача на любые два входа или на все три входа единичных сигналов запрещена, т.е.

qRqS = qRqT = qSqT = qSqRqT = 0.

Матрица переходов имеет вид (таб.3.3):

Таблица 3.3

qR qS qT

0 0 a1 0 0

1 0 0 a2 a3

1 0 a3 0 a3

1 1 0 a4 0

Переход 0 — 0 осуществляется при qS = 0, и qT = 0. Значения сигнала Qq на этот переход не влияет, и его положим равным неопределенному коэффициенту α1.

Переход 0 — 1 осуществляется при qT = 1 и qS = 0, или qT = 0 и qS = 1. Значение сигнала qS и qT на переход 0 — 1 не влияет и их положим равными неопределенному коэффициенту. Один выбираем произвольно α2, а другой - имеет значение противоположное значению выбранного входа α2, и т.д.

3.4. Формализация закона функционирования конечных автоматов

Как правило, для математического исследования автомата с памятью, его представляют в следующем виде (рис.3.11).

В автоматах с памятью (конечные автоматы) значение выходного сигнала в данный момент времени определяется не только значением входного сигнала, но и внутренним состоянием автомата, в которое он перешел под воздействием сигналов, поступивших в предшествующие моменты времени.

Для описания функционирования автомата необходимо рассматривать соответствие между последовательностями входных и выходных символов, т.е. между входными и выходными словами.

Нахождение канонической формы задания автомата составляет задачу абстрактного синтеза автомата.

Построение структурных схем на основании канонической формы задания автомата составляет задачу структурного синтеза автомата.

Основной математический аппарат, используемый при структурном синтезе конечных автоматов тот же, что и при синтезе логических схем. Поэтому структурный синтез рассмотрим раньше абстрактного синтеза. Это целесообразно и с методической точки зрения, поскольку наличие сведений о структурном синтезе позволяет весьма доступно и наглядно сформулировать конкретные задачи абстрактного синтеза автомата.

Для задания автомата необходимо описать переходы из одного состояния в другое под воздействием каждого входного сигнала и правила определения значений выходных сигналов, т.е. определить функции переходов и выходов.

Описание функций переходов и выходов может быть сделано различными способами: в виде уравнений, таблиц и граф-схем.

Функции переходов и выходов часто называют алфавитными операторами, поскольку они дают связь между словами во входном и выходном алфавитах.

Различают две модели автомата с памятью: автоматы Мили и автоматы Мура.

В автоматах Мили значение выходного сигнала Y(t) в момент времени t определяется значениями входных сигналов Х(t) и состоянием автомата а(t) в тот же момент времени.

Закон функционирования автомата Мили описывается следующим образом

Y(t) = f1[X(t), a(t)] - функция выходов;

a(t+1) = f2[X(t), a(t)] - функция переходов. (3.4)

В автоматах Мура значение выходного сигнала Y(t) в момент времени t полностью определяется состоянием автомата в тот же момент времени.

Y(t) = f1[a(t)] - функция выходов;

a(t+1) = f2[x(t), a(t)] - функция переходов. (3.5)

На рис. 3.12, 3.13 приведены соответственно схемы автоматов Мили и Мура.

Рисунок 3.12 – Схема автомата Мили

Рисунок 3.13 – Схема автомата Мура

Любой автомат с памятью можно описать как по модели автомата Мили, так и по модели автомата Мура.

Задача структурного синтеза конечных автоматов состоит в выборе типов и количества элементарных автоматов и способа соединения их между собой с помощью логических элементов, при котором получается оптимальная в некотором смысле (минимальная) схема, функционирующая в соответствии с заданными алфавитными операторами.

Практически в качестве элементов памяти блока памяти в основном используются устройства с двумя внутренними состояниями, а исходными элементами комбинационных схем являются различные логические элементы.

В теории дискретных автоматов устройства с двумя состояниями принято называть элементарными автоматами (ЭА).

О бобщенная

структурная схема КА может быть

представлена так, как показано на рис.

3.14, где Q1,

Q2,...,

Qm

- элементарные автоматы (элементы

памяти).

бобщенная

структурная схема КА может быть

представлена так, как показано на рис.

3.14, где Q1,

Q2,...,

Qm

- элементарные автоматы (элементы

памяти).

Рисунок 3.14 – Обобщенная структурная схема КА

КС-1, КС-2 - комбинационные схемы.

Х, Y, А - алфавиты входов, выходов и состояния соответственно. Сигналы q1, q2,..., qm являются логическими функциями физических входов и состояний конечных автоматов и называются функциями возбуждения элементарных автоматов, соответственно Q1,Q2,...,Qm. Функция возбуждения формируется с помощью КС-1, а функция выходов - с помощью КС-2.

Функции возбуждения определяют переход ЭА Qi из одного состояния в другое.

Аргументами функции возбуждения являются входные переменные Х1, Х2,..., Хк и состояния ЭА Q1,Q2,...,Qm , т.е.

qij(t) = Fij[xi(t), Qj(t)]. (3.6)

Данная функция, как и ее аргументы, может принимать лишь два значения и, следовательно, является логической.

Совокупность этих функций определяет структуру комбинационной схемы КС-1.

Функции выходов тоже являются логическими и определяют структуру комбинационной схемы КС-2

yi(t) = Fi[xi(t), Qj(t)] - для автомата Мили,

qi(t) = Fi[Qj(t)] - для автомата Мура.

Структура КС-1 и КС-2 существенным образом зависит как от числа и типов выбранных ЭА и логических элементов, так и от выбранных вариантов кодирования входов, выходов и состояний.

Конечная цель структурного синтеза КА состоит в определении выражений для функции возбуждения qi всех ЭА Qi, а также в определении функций физических входов и построения на их основе функциональной схемы. В целом решение задачи структурного синтеза КА оказывается возможным свести к следующим последовательно выполняемым шагам:

выбору числа и типов ЭА, а также базиса (ФПС ЛФ);

выбору вариантов кодирования входов, выходов и состояний КА;

формирование входных сигналов ЭА;

построение схемы дискретного автомата.

При использовании канонического метода синтеза структуры дискретных устройств выражения функций возбуждения и выходов определяют с помощью так называемой кодированной таблицы функционирования КА. Это определенным образом трансформированная и дополненная символами функций возбуждения ЭА таблица переходов и выходов, все элементы которой представлены соответствующими им двоичными кодами.

Методика структурного синтеза автоматов с памятью

1. Задание автомата в канонической форме.

2. Выбор структуры сигналов на физических входах и выходах.

3. Кодирование входных, выходных сигналов и состояний автомата в соответствии с выбором сигналов.

4. Выбор типа элементарных автоматов и базиса.

5. Составление кодированных таблиц переходов и выходов (кодированного графа) автомата.

6. Составление таблиц функций возбуждения элементарных автоматов, входящих в синтезируемый конечный автомат.

7. Получение минимальных форм этих функций и функций выходов.

8. Выбор типа логических элементов и выражение полученных минимальных форм с учетом базиса.

9. Составление структурной схемы конечного автомата.

10. Проверка функционирования схемы.

3.5. Синтез функциональных схем конечных автоматов

Пример.

Синтезировать конечный автомат Мили, который под воздействием входного сигнала Х0 не изменяет своего состояния, при подаче каждого сигнала Х1 последовательно переходит в состояние а0, а1, а2, а3, а4, а5, а0, а1, а2,... и т.д., выдавая при переходе из а5 в а0 выходной сигнал y1. Во всех остальных случаях автомат выдает сигнал y0.

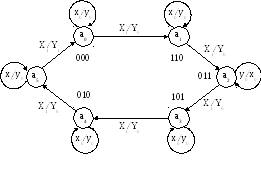

1. Зададим закон функционирования автомата в канонической форме. В соответствии с формулировкой, приведенной в примере, построим таблицу переходов и выходов (таблица 3.4), или граф (рис. 3.15).

Таблица 3.4

-

a

j

jxi

a0

a1

a2

a3

a4

a5

x0

a

0

0Y0

a

1

1Y0

a

2

2Y0

a

3

3Y0

a

4

4Y0

a

5

5Y0

x1

a

1

1Y0

a

2

2Y0

a

3

3Y0

a

4

4Y0

a

5

5Y0

a

0

0Y1

Рисунок 3.15 – Граф конечного автомата

2. Выбор структуры сигналов.

В качестве физических сигналов выбираем электрические сигналы, способные принимать любое из двух значений 0 или 1.

3. Кодирование входных и выходных сигналов, и состояний автомата с помощью выбранных физических сигналов.

Количество входов и выходов состояний определяется из выражения

2k ≥ N > 2k - 1 K = ]log2N[,

где N - количество состояний (значений входного или выходного сигналов) синтезируемого автомата;

К - количество двоичных переменных (элементарных автоматов).

В данном случае требуется один вход и один выход.

Квх = 1, Квых = 1.

Т.к. число состояний автоматов 6, то количество элементарных автоматов Кэл = 3.

Кодирование входных и выходных сигналов выполним, например, следующим образом:

Хi

U

Yi

Z

Хi

U

Yi

Z

x0 0 y0 0

x1 1 y1 1

Кодирование состояний автомата (таблица 3.5) проведем произвольно.

Таблица 3.5

-

aj

Q1

Q2

Q3

a0

a1

a2

a3

a4

a5

0

1

0

1

0

1

0

1

1

0

1

0

0

0

1

1

0

0

Наборы 001, 111 не используются, т.е. запрещены, что может быть использовано при минимизации.

4. Выбор типа элементарного автомата. В качестве элементарного автомата выберем RST- триггер (рис.3.16)

Рисунок 3.16 – Условное графическое обозначение RS-триггера

Среди множества возможных вариантов кодирования могут быть найдены варианты с очень интересными свойствами, существенно упрощающие оборудование или увеличивающие быстродействие. Однако достижения, которые имеются в этом направлении, носят пока характер более или менее случайных находок, какой-либо систематизации выбора вариантов кодирования еще нет, отсутствуют и обобщающие работы по этому вопросу.

Функция переходов RST-триггера приведена в таблице 3.6.

Таблица 3.6

-

n(t)

qS(t)

qT(t)

Q(t)

Q(t+1)

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

1

–

–

0

0

–

–

–

–

–

–

Одновременная подача на любые два или на все три входа единичных сигналов запрещена, т.е.

qRqS = qRqT = qSqT = qRqSqT = 0.

Матрица переходов имеет вид (таблица 3.7).

Таблица 3.7

-

Q(t)

Q(t+1)

qP

qS

qT

0

0

1

1

0

1

0

1

α1

0

α3

0

0

α2

0

α4

0

1

1 3

30

Переход 0-0 осуществляется при qS = 0 и qT = 0. Значение сигнала qR на этот переход не влияет и его положим равным неопределенному коэффициенту α1.

Переход 0-1 осуществляется при qT = 1 и qS = 1. Значения сигналов qT или qS не влияют и их положим равными неопределенному коэффициенту. Первый коэффициент выбирается произвольно, а второй имеет значение, противоположное значению первого и т.д.

5. На основании проведенного кодирования и выбранного типа элементарного автомата (RST-триггера) строим кодированную таблицу переходов, выходов и функций возбуждения.

Кодированная таблица переходов и выходов определяет зависимость состояния элементарных автоматов, входящих в синтезируемый автомат Мили, в момент t+1 и сигналов на его физических выходах в момент t от значений сигналов на физических входах и состояний элементарных автоматов в момент времени t.

Чтобы происходили заданные кодированной таблицей переходов и выходов переходы элементарных автоматов, необходимо для каждого из них вырабатывать соответствующие входные воздействия, определяемые функциями возбуждения.

Функции возбуждения каждого элементарного автомата определяют значения его управляющих сигналов в момент времени t в зависимости от состояния всех элементарных автоматов и значений входных сигналов синтезируемого автомата в тот же момент времени.

Если Q1, Q2,..., Qк - состояние элементарных автоматов, а V1, V2,..., Vm - сигналы на физических входах конечного автомата, то в общем случае функция возбуждения qij для i-го входа j-го элементарного автомата может быть записана следующим образом:

qij(t) = Fij[V1(t), V2(t),..., Vm(t), (3.7)

Q1(t), Q2(t),..., Qk(t)].

В нашем случае k = 3, а m = 1. Аргументами функций возбуждения являются V(t), Q(t) и Q2(t), и Q3(t), тогда

qR1(t) = FR1[V(t), Q1(t), Q2(t), Q3(t)]

qS1(t) = FS1[V(t), Q1(t), Q2(t), Q3(t)] (3.8)

qT1(t) = FR1[V(t), Q1(t), Q2(t), Q3(t)].

Функции возбуждения определяются аргументами, действующими в момент времени t, поэтому синтезировать на их основе схемы можно по способу комбинационных схем. Все аргументы действуют в момент времени t.

Функция выхода записывается в виде

Z(f) = F[V(f), Q1(t), Q2(f), Q3(f)]. (3.9)

Кодированная таблица переходов, выходов и функций возбуждения (таблица 3.8).

Таблица 3.8

|

V(t) |

Q1(t) |

Q2(t) |

Q3(t) |

Q1(t+1) |

Q2(t+1) |

Q3(t+1) |

Z(t) |

qR1(t) |

qS1(t) |

qT1(t) |

qR2(t) |

qS2(t) |

qT2(t) |

qR3(t) |

qS2(t) |

qT3(t) |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

α1 |

0 |

0 |

β1 |

0 |

0 |

γ1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

α2 |

0 |

0 |

β2 |

0 |

γ2 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

α3 |

0 |

0 |

0 |

β3 |

0 |

0 |

γ3 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

α4 |

0 |

β4 |

0 |

0 |

0 |

γ4 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

α5 |

0 |

0 |

0 |

β5 |

0 |

γ5 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

α6 |

0 |

β6 |

0 |

0 |

γ6 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

α7 |

α7 |

0 |

β7 |

|

γ7 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

α8 |

0 |

|

0 |

β8 |

0 |

0 |

γ8 |

|

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

α9 |

|

β9 |

0 |

|

0 |

γ9 |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

α10 |

0 |

|

0 |

β10 |

|

γ10 |

0 |

|

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

α11 |

|

β11 |

0 |

β11 |

γ11 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

α12 |

0 |

|

β12 |

0 |

0 |

γ12 |

0 |

0 |

В последних девяти столбцах приведены значения функций возбуждения, полученные на основании переходов элементарных автоматов Q1, Q2 и Q3 (таблица 3.6) и матрицы переходов (таблица 3.7).

Каждая из функций возбуждения является неполностью заданной. Минимизируем функции возбуждения с помощью карт Карно (рис.3.17). Минимальные формы функций возбуждения автоматов:

qR1 = 0; qS1 = 0; qT1 = V;

qR2 = 0; qS2 = VQ1Q3; qT2 = VQ; (3.10)

qR3 = VQ2; qS3 = VQ1Q2; qT3 = 0.

Функция кодированного выхода автомата Мили определяет зависимость значения сигнала на некотором физическом выходе в момент времени t от состояний всех элементарных автоматов и значений сигналов на всех физических входах синтезируемого конечного автомата в тот же момент времени.

В общем виде

Zj(t) = φj[V1(t), V2(t),..., Vm(t), Q1(t), Q2(t),..., Q3(t)].

В нашем случае Z(t) = φj[V(t), Q(t), Q2(t), Q3(t)] и определяется по одному набору, поэтому

Z(A)

= VQ1![]() 2

2![]() 3

(3.11)

3

(3.11)

На основании минимальных форм функций возбуждения и функции выхода строится структурная схема конечного автомата, обобщенная схема которого состоит из запоминающей и комбинационной частей (рис.3.18).

В нашем примере запоминающая часть включает 3 элементарных автомата (RST-триггера), а комбинационная часть зависит от выбора функционального полного набора логических элементов. Допустим, для данного случая принята основная функционально полная система элементов, состоящая из элементов И, ИЛИ, НЕ. Тогда в основу построения схемы положим выражения (3.10) и (3.11) (рис.3.19).

Комбинационная часть может быть реализована на программируемых логических матрицах.

На рис.3.18 и 3.19 введена цепь подачи синхроимпульсов t.

Одной из основных причин их ввода является потенциальный характер выходных сигналов элементарных автоматов. При этом моменты переключения определяются синхронизирующими импульсами.

Функции возбуждения любого триггера с одним или двумя входами могут рассматриваться как частные случаи функций возбуждения триггера с тремя входами (RST-триггера). Если в матрице переходов (таблица 3.7) неопределенные коэффициенты α2, α3 принять равными нулю, то ее третий столбец следует исключить и получается матрица переходов RS-триггера. Если же принять равным нулю коэффициенты α2 и α4, то получим триггер RT-типа. И, наконец, если принять равным нулю коэффициенты α1, α2, α3, α 4, то получим Т-триггер.

Поэтому структурный синтез конечных автоматов на триггерах в общем случае целесообразно производить на RST-триггерах. Затем, подбирая значения коэффициентов, следует получить оптимальные формы совокупности функций возбуждения.

При этом критерии оптимальности могут быть различными. Так, предельная минимальность схем иногда достигается применением в одном устройстве различных типов триггеров, а с точки зрения унификации это нежелательно. Если использовать триггеры одного типа, то это приведет к некоторому возрастанию количества необходимого оборудования.

В некоторых случаях состояния автоматов могут быть неустойчивыми. Пусть автомат под воздействием входного сигнала Хi переходит из состояния ак в состояние аm (рис.3.20). Тогда, если длительность входного сигнала превышает время переключения автомата из одного состояния в другое, он проскочит состояние а1 и сразу окажется в состоянии аm. Состояние автомата будет при этом неустойчивым.

Рисунок 3.20 - Состояния конечного автомата

а) Обеспечение устойчивости путем выбора необходимой длительности синхронизируемых импульсов

Одним из возможных путей обеспечения устойчивости состояний является выбор длительности синхронизирующих импульсов.

Устойчивость обеспечивается, если длительность синхросигнала меньше времени, необходимого для двух последовательных срабатываний элементарных автоматов памяти. Данный способ повышает требование к стабильности длительности синхроимпульсов

τср.триггера < τсинхр. < 2τср.триггера.

б) Обеспечение устойчивости путем использования двойной памяти автоматов.

Недостаток: объем памяти увеличивается в 2 раза.

в) Обеспечение устойчивости путем использования 2-х серий синхроимпульсов, сдвинутых относительно друг друга на полупериод

Реальные элементарные автоматы (триггеры) имеют свое, отличное от других, время переключения. Это обстоятельство приводит к тому, что триггеры переключаются неодновременно. Такое явление называют “гонками” (состязаниями). Если при изменении состояния автомата должны переключаться несколько триггеров, то один из них может выиграть гонки, т.е. переключиться раньше других. При этом изменяются выходные сигналы возбуждения триггеров, и в результате переходы других триггеров могут произойти не в соответствии с заданным законом функционирования.

Если гонки не изменяют заданный закон функционирования автомата, то такие гонки называют некритическими. Если же гонки изменяют закон функционирования автомата, то такие гонки называются критическими.

Все возможные способы обеспечения устойчивости функционирования автомата устраняют условия критических гонок.

3.6 Назначение и классификация регистров

Осуществляя классификацию дискретных устройств, прежде всего необходимо их разделить на типовые дискретные устройства общетехнического применения и типовые дискретные устройства специального применения. К типовым устройствам общетехнического применения следует отнести дискретные устройства, широко применяемые в различных областях техники.

Отличительной особенностью этих устройств является то, что образуемые ими функциональные блоки нецелесообразно разбивать на более малые функциональные блоки.

К типовым устройствам специального применения относятся дискретные устройства, используемые в определенных областях техники. В соответствии с вышеизложенным к типовым дискретным устройствам общетехнического применения можно отнести: регистры, счетчики, сумматоры, шифраторы и дешифраторы. К типовым дискретным устройствам специального применения в АСУ и связи можно отнести: коммутаторы, устройства сравнения, мажоритарные устройства и т.д.

В соответствии с форматами данных выбирается разрядность регистра. Каждый разряд регистра используется для ввода, вывода и хранения одного разряда двоичного числа.

В зависимости от назначения регистры делят на следующие основные группы: накопительные или запоминающие, сдвигающие и регистры-преобразователи, преобразующие коды двоичных чисел.

Числа в регистр поступают в параллельном двоичном или последовательном коде.

Сдвигающие регистры используют для ввода, хранения, сдвига и вывода двоичных чисел.

Регистры-преобразователи работают с двоичной информацией в параллельном и последовательном коде, выполняя, помимо операций ввода, вывода, хранения, сдвига, ряд логических действий - дизъюнкцию, конъюнкцию, сложение по модулю два и другие.

Регистры - неотъемлемая часть блоков и узлов ЦУ. Основа регистра - триггеры и комбинационные логические элементы.

Регистры сдвига (РС) широко применяются в информационных цифровых устройствах. Например, в калькуляторах, где при наборе каждой новой цифры на клавиатуре , числа на индикаторе сдвигаются влево. Например, для набора числа 325, нужно сделать следующее. Сначала набирается клавиша с цифрой 3. Цифра 3 появляется в крайней правой позиции на индикаторе, затем нажимается клавиша с цифрой 2. В результате цифра 3 на индикаторе сдвигается на одну позицию влево, и на ее месте в крайнем правом положении появляется цифра 2 и т.д. Данный пример иллюстрирует две важные характеристики регистра сдвига: 1) регистр сдвига, устройство, обладающее временной памятью, благодаря чему числа остаются на индикаторе даже при отпускании клавиши; 2) это устройство сдвигает числа на индикаторе на одну позицию влево каждый раз, когда набирается новая цифра. Пример применения регистра сдвига в цифровой системе приведен на рис.3.21.

Рисунок 3.21 - Обобщенная схема цифровой системы

Регистры - это последовательностные устройства, предназначенные для приема, временного хранения, выполнение простых логических преобразований и передачи кодов двоичных чисел.

Основное функциональное назначение регистров - оперативная память для многоразрядных двоичных чисел.

Чаще всего регистр представляет собой совокупность триггеров, количество которых равно количеству разрядов числа и вспомогательных логических схем, обеспечивающих выполнение в регистре всех или части следующих элементарных операций:

установку регистра в нуль;

прием кода из другого устройства;

выдачу кода в другое устройство;

преобразование кода числа (преобразование обратного кода в прямой, прямого - в обратный);

сдвиги кодов “вправо” и “влево” на требуемое количество разрядов;

преобразование последовательного кода в параллельный и наоборот;

поразрядное логическое сложение;

поразрядное логическое умножение;

поразрядное сложение (сравнение чисел).

В зависимости от назначения схемы конкретных регистров обычно допускают выполнение лишь некоторых из перечисленных операций.

Регистры можно классифицировать следующим образом.

1. По типу используемых запоминающих элементов:

регистры на активных элементах памяти (с использованием триггеров);

регистры на пассивных элементах памяти (с использованием элементов на магнитных материалах или заряда емкости).

2. По виду обработки входных кодов:

регистры без сдвига, в которых значения одноименных разрядов входного и выходного кодов совпадают;

регистры со сдвигом, в которых значения разрядов входного кода совпадают со значениями тех разрядов выходного кода, которые сдвинуты в одну и ту же сторону относительно входного кода на одинаковую величину;

регистры с обратными логическими связями, в которых над входными кодами осуществляются однотипные логические преобразования, определяемые видом обратных связей регистра.

3. По виду входных и выходных сигналов:

регистры с потенциальными сигналами;

регистры с импульсными сигналами;

регистры с импульсно-потенциальными сигналами (вход импульсный, выход - потенциальный), с потенциально-импульсными сигналами (вход потенциальный, выход - импульсный).

4. По количеству тактов:

регистры однотактные;

регистры многотактные.

5. По виду входных и выходных кодов:

регистры последовательные;

регистры параллельные;

регистры последовательно-параллельные, у которых входной код представлен последовательно, а выходной - параллельно и наоборот;

регистры универсальные.

В параллельных регистрах или регистрах памяти ввод/вывод всех разрядов числа производится одновременно за один такт. Для построения n-разрядного регистра памяти требуется n-триггеров. Параллельные регистры служат основным функциональным элементом для построения оперативных запоминающих устройств.

В последовательном регистре ввод/вывод информации осуществляется через один информационный вход и один выход поразрядно со сдвигом числа. Поэтому последовательные регистры называют сдвигающими. За один такт вводимая и выводимая информация сдвигается на один или несколько разрядов вправо или влево. Сдвигающие регистры, реализующие по команде управления сдвига информации влево или вправо, называют реверсивными.

Последовательно-параллельные регистры имеют один информационный вход для последовательного ввода числа в режиме сдвига и выходные вентили для выдачи n-разрядного числа параллельным кодом. Такие регистры выполняют преобразование последовательного кода в параллельный. В параллельно-последовательные регистры информация вводится параллельным кодом за один такт через тактируемые входные вентили, а выводятся из них последовательно по одному разряду в каждом тактовом интервале. Тем самым реализуется операция преобразования параллельного кода в последовательный.

Универсальные регистры сочетают в себе возможности вышеперечисленных типов регистров и, кроме того, обеспечивают режимы отключения входов и выходов (третье логическое состояние) регистра от общей информационной шины, перекоммутацию местами входов и выходов регистра и тем самым переключение функций прием/передача информации в общую информационную шину.

Технические параметры регистров определяются параметрами их основного функционального узла - триггера и разрядностью операнда.

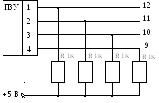

Условное графическое обозначение основного поля регистров имеет вид, представленный на рис.3.22.

a) б) в) г)

д)

Рисунок 3.22 - Условное графическое обозначение регистра и его полей

3.22 а - поле регистра без сдвига,

3.22 б - поле регистра со сдвигом вправо,

3.22 в - поле регистра со сдвигом влево,

3.22 г - поле реверсивного регистра,

3.22 д - графическое обозначение параллельного регистра.

3.7. Регистры параллельного действия

В зависимости от формы представления числа (параллельной или последовательной), используемой при его вводе в регистр, различают два типа регистров: параллельные и последовательные. В параллельный регистр, предназначенное для хранения число, подается одновременно всеми разрядами, т.е. в параллельной форме. В последовательный регистр ввод числа производится путем последовательной во времени подачи цифр отдельных разрядов (обычно, начиная с цифры младшего разряда), т.е. в последовательной форме.

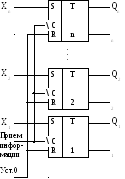

При построении параллельных регистров обычно используются простейшие несинхронные и синхронные RS и D-триггеры. На рис.3.23 приведена схема параллельного регистра, построенного на синхронном RS-триггере, а на рис.3.24 временная диаграмма, в котором осуществляется прием информации с предварительной установкой в нуль. Для этого применяются две управляющие шины “Уст.0” и “Прием информации”. Основной недостаток данного регистра - необходимость предварительной очистки регистра, из-за чего обновление информации осуществляется за два такта.

Возможна организация приема информации в регистр без предварительной установки в нуль. Для этого используется представление записываемой информации парафазным кодом, как показано на рис.3.25. Здесь управляющая шина “Уст.0” отсутствует, так как нет необходимости перед приемом информации гасить содержимое регистра. При парафазной передаче информации сигнал “1” существует на одном из входов R или S каждого триггера в соответствии со значениями разрядов кода.

Рисунок 3.23 - Схема параллельного Рисунок 3.24 - Временная диаграмма

регистра с предварительной сигналов в параллельном

установкой в нулевое состояние регистре

Он устанавливает триггеры в требуемое состояние независимо от той информации, которая в нем хранилась ранее.

Рисунок 3.25 - Схема параллельного регистра без предварительной

установки в нулевое состояние

Если

цифра i-го разряда Xi

= 1, то на вход S соответствующего триггера

поступает сигнал равный 1, и при подаче

уровня логической 1 на вход С триггер

устанавливается в состояние 1. Если Xi

= 0 (![]() i

= 1), то на вход R поступает 1, и этот триггер

устанавливается в состояние 0. Таким

образом, триггеры устанавливаются в

состояния, определенные поступающими

на их входы цифрами разрядов числа.

i

= 1), то на вход R поступает 1, и этот триггер

устанавливается в состояние 0. Таким

образом, триггеры устанавливаются в

состояния, определенные поступающими

на их входы цифрами разрядов числа.

Быстродействие такой схемы выше, чем схемы регистра с предварительной установкой в нуль.

Выдача информации с регистра осуществляется путем включения на выходах триггеров логических схем “И”.

При снятии прямого кода с регистра (схемы “И”) высокие уровни устанавливаются на прямых выходах триггеров, обратного кода - на инверсных выходах.

Процесс передачи информации из одного регистра в другой во многих случаях сопровождается выполнением таких поразрядных операций над кодами, как логическое сложение, логическое умножение, логическое сравнение. Рассмотрим схемы межрегистровых передач, при которых реализуются вышеперечисленные операции. При этом будем полагать, что один операнд записан в регистр RG 1, а второй – в RG 2, а результат должен быть образован в регистре RG 2.

Логическое сложение. Qi = Xi + Yi

На рис.3.26 приведена схема, выполняющая логическое сложение двух n-разрядных чисел, т.е. операцию «ИЛИ» над цифрами каждого разряда обоих чисел. Операция реализуется путем передачи кода с прямых выходов триггеров регистра RG 1 на входы S-триггеров регистра RG 2 без предварительного гашения регистра RG 2. Такая операция может быть использована для формирования n-разрядного кода из двух или нескольких других кодов.

Рисунок 3.26 - Схема, выполняющая логическое сложение двух чисел

Логическое умножение. Qi = Xi ∙ Yi

При логическом умножении для каждого разряда выполняется операция “И” над цифрами кодов, расположенных в регистрах RG 1 и RG 2. Операция сводится к передаче кода с инверсных выходов триггеров регистра RG 1 на входы R-триггеров регистра RG 2 без предварительного гашения, рис.3.26 - пунктирные линии. Операция логического умножения обычно используется для выделения части кода.

3.8. Сдвигающие регистры

Автомат, функции возбуждения которого qD = x, qr = Qr-1, r = 1,..., m-1, называется m-разрядным сдвигающим регистром.

Сдвиг кода - это операция, при которой все разряды кода перемещаются на некоторое одинаковое количество разрядов “вправо” или “влево”. В общем случае операция сдвига кода в регистре означает, что каждый запоминающий элемент этого регистра Тj должен передать хранимую информацию элементу Тj + i и после этого принять информацию от запоминающего элемента Тj - i (сдвиг на i разрядов). В некоторых случаях, освобождающиеся при сдвиге i старших (младших) разрядов элементы регистра сохраняют прежнее состояние, заполняются нулями или принимают новую информацию извне, а информация, выдвигаемая из младших (старших) разрядов регистра, теряется или передается во внешние цепи. В других случаях регистр может быть замкнут в кольцо так, что информация, выдвигаемая из младших (старших) разрядов регистра, принимается в освобождающиеся запоминающие элементы старших (младших) разрядов регистра, такие регистры называются - кольцевыми.

Информация в кольцевой регистр вводится параллельным кодом и затем циркулирует в замкнутом кольце под действием тактовых синхроимпульсов. Кольцевые регистры удобно использовать для построения, например, тактовых генераторов цифровых устройств.

По направлению сдвигов регистры делятся на три вида:

сдвигающие код “вправо”;

сдвигающие код “влево”;

реверсивные, осуществляющие сдвиг “влево” или “вправо” в соответствии со значениями управляющих сигналов. В зависимости от способов приема и выдачи информации различаются следующие сдвигающие регистры:

с последовательным приемом и последовательной выдачей кодов;

с последовательным и параллельным как приемом, так и выдачей разрядов кода.

Основная трудность, которая возникает при построении сдвиговых регистров, состоит в том, что при выполнении сдвига каждый разряд (запоминающий элемент) должен одновременно выдавать информацию в следующий разряд и принимать новую информацию из предыдущего разряда. Для предотвращения явления гонок эти процессы должны быть разделены во времени. Это достигается включением элементов линий задержек между разрядами, либо использованием двухтактных триггеров. В интегральной схемотехнике сдвигающие регистры строятся преимущественно на двухтактном D- и JK-триггерах. В регистрах на D-триггерах для передачи информации между разрядами требуется связь между Qi и Di - 1, а в случае использования JK-триггеров - двойные связи: Qi с Ii + 1 и Qi с Ki + 1. Структуры, принцип работы и параметры данных регистров аналогичны. В зависимости от системы используемых запоминающих и логических элементов регистры сдвига строят по разным схемам.

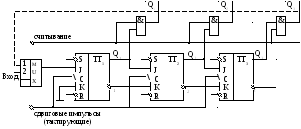

На рис.3.27 приведена схема регистра, обеспечивающего сдвиг информации вправо. Сдвиг осуществляется при подаче импульса на вход “Сдвиг”.

Рисунок 3.27 - Схема регистра сдвига

Для реализации функции сдвига вправо необходимо соединить прямой выход триггера i-го разряда со входом J триггера (i + 1)-го разряда, а инверсный выход - со входом К. Синхронизирующие входы всех триггеров объединяют и образуют шину сдвига.

В момент поступления импульса сдвига значения сигналов на выходах J и К каждого триггера определяют его переход в новое состояние. Это новое состояние каждый триггер принимает после окончания импульса сдвига.

Данная схема регистра может быть применена для преобразования параллельного кода в последовательный. Для преобразования последовательного кода в параллельный может быть использована схема (рис.3.28).

Рисунок 3.28 - Схема регистра для преобразования последовательного кода в параллельный

При подаче каждого сдвигового импульса в триггерах осуществляется запись очередного разряда входного последовательного кода и сдвиг информации вправо на 1 разряд. После подачи трех сдвиговых импульсов в регистре записывается 3-х разрядное число, которое может быть считано параллельным кодом при подаче импульса считывания.

Для получения сдвига “влево” необходимо выходы триггеров присоединить ко входам J не “правых”, а “левых” соседних триггеров (рис.3.28 - показано пунктиром).

В зависимости от формы представления числа (параллельной или последовательной), используемой при его вводе в регистр, различают два типа регистров: параллельные и последовательные. В параллельный регистр предназначенное для хранения число подается одновременно всеми разрядами, т.е. в параллельной форме. В последовательный регистр ввод числа производится путем последовательной во времени подачи цифр отдельных разрядов (обычно, начиная с цифры младшего разряда), т.е. в последовательной форме.

При построении параллельных регистров обычно используются простейшие несинхронные и синхронные RS и D-триггеры.

Очень часто используются реверсивные сдвигающие регистры, в которых направление сдвига определяется (диктуется) значением специального управляющего сигнала. Основные принципы их построения те же, что и однонаправленных сдвигающих регистров. При этом выход каждого триггера связывается одновременно со входами двух соседних (справа и слева) триггеров через управляемые вентили.

Схема реверсивного сдвигающего регистра на JK-триггерах показана на рис. 3.29. Она управляется двумя сигналами “Правый” и “Левый” и сдвигающими импульсами “Сдвиг”.

Если на шину “Правый” подать единичный сигнал, то под действием каждого сдвигающего импульса, поступающего на шину “Сдвиг”, будет происходить сдвиг кода, хранимого в регистре “Вправо”. При единичном сигнале на шине “Левый” сдвиг информации осуществляется в противоположном направлении. Одновременная подача единичных сигналов на шины “Правый”, “Левый” запрещена, поскольку при этом порядок функционирования не определен и под действием сигнала “Сдвиг” информация в регистре будет испорчена.

Рисунок 3.29 - Схема реверсивного сдвигающего регистра

Если сигналы “Правый” и “Левый” одновременно равны нулю, то цепи связи между триггерами разорваны и подача импульса сдвига на шину “Сдвиг” приводит к гашению содержимого регистра.

Кроме рассмотренных схем сдвиговых регистров, у которых сдвиг информации происходит на один разряд при подаче одного сдвигающего импульса, применяются сдвиговые регистры, у которых при подаче одного сдвигающего импульса происходит сдвиг на два или больше разрядов. Для этого необходимо связывать между собой триггеры не соседних разрядов, а через один, два, или три и т.д.

Синтез регистров осуществляется методом синтеза конечных автоматов.

Динамические регистры - регистры, для которых определена верхняя граница временного интервала хранения информации без восстановления. Чаще всего в них физическим носителем информации является заряд некоторой емкости или зарядовый пакет в объеме полупроводника. Для управления зарядом используются транзисторы, обладающие весьма большим сопротивлением в запертом состоянии (1012 - 1015 Ом). Используя логические элементы на МДП-транзисторах, можно по заданному алгоритму управлять зарядом и напряжением на некоторой паразитной межэлектродной емкости.

Основное достоинство динамического регистра на МДП-транзисторах - низкое потребление мощности.

Недостаток динамических регистров - ограничение сверху длительностей тактовых импульсов, которое связано с конечным временем хранения заряда на паразитных емкостях МОП-транзисторов. Вследствие этого рабочая частота динамического регистра ограничена f ≥ 1-10 кГц.

Другой недостаток - сложность тактирования регистра четырьмя сдвинутыми во времени тактовыми последовательностями.

Отмеченные достоинства и недостатки присущи и динамическим регистрам на основе приборов с зарядовой связью (ПЗС). Регистры на основе ПЗС относятся к элементам функциональной электроники, у которых нет четких границ между электронными компонентами. Динамические регистры применяют в качестве цифровых линий задержки, в устройствах с последовательной обработкой информации и в последовательных ОЗУ большой емкости.

3.9. Назначение, классификация и основные характеристики запоминающих устройств

Хранение небольших массивов кодовых слов осуществляется с помощью регистров. Но уже при необходимости хранить десятки слов применение регистров приводит к неоправданно большим аппаратурным затратам. Для хранения больших массивов слов строят специальные запоминающие устройства.

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ее с другими частями ЭВМ или микропроцессорных систем. ЗУ подразделяются на внешние, буферные и внутренние. Внешние ЗУ служат для хранения больших объемов информации и программного обеспечения системы. В них используются ЗУ с прямым доступом на магнитных барабанах (дисках) и ЗУ с последовательным доступом на магнитных лентах. Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внутренней и внешней памятью. Внутренние ЗУ делят на оперативные и постоянные. Оперативные ЗУ выполняют запись, хранение и считывание произвольной двоичной информации и массивов обрабатываемых данных. Постоянные ЗУ осуществляют хранение и выдачу постоянно записанной информации, содержание которой не изменяется во время работы системы. Это используемые в процессе работы стандартные подпрограммы и микропрограммы, табличные значения различных функций, константы и др. Мы будем рассматривать внутренние ЗУ.

По способу организации обмена информацией между отдельными ЗУ, системами памяти и микропроцессорами различают ЗУ:

с произвольной выборкой (ЗУПВ);

с последовательным обращением (ЗУПО);

с последовательно-параллельной организацией обмена.

Информацию из ПЗУ можно только считывать. Имеются три типа ПЗУ:

ПЗУ, запрограммированное изготовителем ЭВМ;

программируемые ПЗУ (ППЗУ);

репрограммируемые ПЗУ (РППЗУ) или стираемые ПЗУ.

Оперативное ЗУ - это память, из которой процессор может считывать или в которую может записывать информацию.

Поиск нужного слова в памяти можно производить либо по его адресу (адресные ЗУ), либо по его содержанию (ассоциативные ЗУ). ЗУ имеют ряд показателей качества. Основными из этих характеристик являются следующие.

Емкость ЗУ.

Любое ЗУ состоит из некоторого числа ячеек, в каждой из которых может храниться слово с определенным числом разрядов n. Ячейки последовательно нумеруются двоичным числом. Номер ячейки называется адресом и выражается двоичным числом 2n. Количество информации, которая может храниться в ЗУ, определяет его емкость. Емкость можно выражать числом ячеек N с указанием разрядности n хранимых в них слов, либо ее можно определить в битах: N × n.

Рисунок 3.30 - Структура пакета

Часто в цифровой электронике разрядность ячеек выбирают равной байту (1 байт равен 8 битам, рис.3.30), поэтому емкость оказывается удобным представить в байтах. Большие значения емкости часто выражаются в единицах К, М и Г. Например, К = 210 = 1024, тогда N = 64 Кбайт означает емкость, равную N = 64 х 1024 байт = 64 х 1024 х 8 бит информации.

Таким образом, емкость памяти может выражаться не только в битах, байтах, но и в словах, состоящих из определенного числа байтов. Так как эта емкость может быть очень велика (до 1012 бит), то обычно используют крупные единицы, образованные присоединением приставок К(кило), М(мега) и Г(гига) к перечисленным выше единицам. При этом надо учитывать, что в системах передачи и обработки информации приставки К, М и Г соответственно равны 210 = 1024, 220 = 1048576 и 230 = 1073741824.

Время обращения определяется с момента подачи в устройство сигнала записи или чтения до того момента, когда закончатся все действия, связанные с выполняемой операцией и устройство будет готово принять и реализовать следующую операцию обращения к накопителю информации. Это время называется также длительностью цикла обращения к ЗУ. В течение цикла можно выбрать информацию (чтение), ввести информацию (запись), обновить или модифицировать состояние некоторого элемента ЗУ. Таким образом следует отличать время обращения к ЗУ от времени выборки - времени от момента подачи сигнала записи или чтения до завершения соответствующей операции.

Скорость обмена информацией между ЗУ и другими устройствами определяется числом бит (байт), передаваемых в единицу времени.

Стоимость 1 бита определяется отношением стоимости к ее информационной емкости.

Энергозависимые и энергонезависимые ЗУ это способность сохранять или не сохранять информацию при отключении источников питания.

Кроме приведенных характеристик, довольно часто указывают и другие практически важные показатели качества ЗУ, например, потребляемую мощность, способ организации, физические свойства запоминающих элементов, массогабаритные и другие характеристики.

В большинстве случаев требуются дешевые энергонезависимые ЗУ большой емкости с малым временем выборки, однако устранение этого противоречия представляет собой в настоящее время практически неразрешимую задачу.

Улучшение технических и эксплуатационных характеристик вычислительных средств в значительной степени связано с увеличением емкости и быстродействия запоминающих устройств. В микропроцессорных вычислительных устройствах, в зависимости от их назначения, ЗУ занимают от 40 до 70% всего оборудования. Команды и исходные данные хранятся в основной памяти. Основная память состоит из памяти программ и памяти данных (рис.3.31).

Рисунок 3.31 - Структура основной памяти

Полупроводниковая память базируется на основе триггеров и регистров. Каждый триггерный элемент может хранить один бит (0 или 1). Совокупность триггеров образует слово.

По технологическому исполнению полупроводниковые ЗУ имеют следующие структуры: биполярные и МПД, использующие схемотехнику ТТЛ, ЭСЛ, И2Л, КМДП. В ЭВМ нового поколения во внутренних ЗУ в основном используются полупроводниковые интегральные схемы, которые с традиционными магнитными имеют следующие достоинства: высокую информационную емкость, относительно низкую стоимость, высокую надежность.

По способу хранения информации ОЗУ представляют собой бистабильные элементы и обеспечивают считывание информации без ее разрушения.

В динамических ЗУ для хранения информации используют инерционные свойства реактивных элементов (конденсаторов), что требует периодического восстановления (регенерации) состояния ЭП в процессе хранения информации.

На рис.3.32 приведена типовая структура запоминающего устройства с произвольной выборкой (ЗУПВ) с организацией 1024х4.

Рисунок 3.32 - Структура запоминающего устройства с произвольной выборкой

Четыре

двунаправленные шины Д3-Д0 предназначены

для обмена данными между памятью и

остальными компонентами системами. Они

подключаются к системной шине данных

и работают как входные линии при записи

и как выходные линии при считывании

информации. Сигналы

![]() (чтение) и

(чтение) и

![]() (запись) определяют выполняемую операцию,

иногда линии

(запись) определяют выполняемую операцию,

иногда линии

![]() и

и

![]() объединяются в одну линию RD/WR. Десять

входных линий А9

- А0

используются для адресации ячеек памяти.

Линии выбора кристалла разрешают

выполнение операции записи или чтения,

их в схеме не более трех; в кристалле

имеется логическая схема И, срабатывающая

при одной определенной комбинации

сигналов на линиях CS. Если комбинация

совпадает с требуемой для данного

кристалла, то он выбирается для выполнения

нужной операции. В противном случае

кристалл является не выбранным, выходные

буферные линии данных переводятся в

состояние высокого сопротивления и

кристалл отключается от шины данных.

Наличие входов СS позволяет подключать

параллельно большое число кристаллов

к одним и тем же шинам данных и адреса.

объединяются в одну линию RD/WR. Десять

входных линий А9

- А0

используются для адресации ячеек памяти.

Линии выбора кристалла разрешают

выполнение операции записи или чтения,

их в схеме не более трех; в кристалле

имеется логическая схема И, срабатывающая

при одной определенной комбинации

сигналов на линиях CS. Если комбинация

совпадает с требуемой для данного

кристалла, то он выбирается для выполнения

нужной операции. В противном случае

кристалл является не выбранным, выходные

буферные линии данных переводятся в

состояние высокого сопротивления и

кристалл отключается от шины данных.

Наличие входов СS позволяет подключать

параллельно большое число кристаллов

к одним и тем же шинам данных и адреса.

Иногда кристаллы имеют сигнал разрешения выдачи ОЕ, который стробирует выходные усилители при чтении информации.

3.10. Оперативные полупроводниковые запоминающие устройства

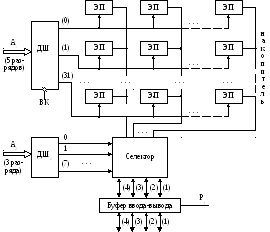

Обобщенная схема полупроводникового ОЗУ приведена на рис.3.33. Схема состоит из накопителя констант (НК), дешифраторов строк и столбцов (ДСХ и ДСУ), устройства записи (УЗ), устройства считывания (УС) и устройства управления (УУ). Основой накопителя статических ОЗУ являются триггерные элементы памяти, реализованные на многоэмиттерных транзисторах, а динамических – однотранзисторные запоминающие элементы, состоящие из ключевого транзистора и емкости хранения информации.

Рисунок 3.33 - Обобщенная схема полупроводникового ОЗУ

На рис.3.34 приведена типовая структура микросхемы ОЗУ. Информация хранится в накопителе. Он представляет собой матрицу, составленную из элементов памяти (ЭП), расположенных вдоль строк и столбцов.

Рисунок 3.34 - Типовая структура микросхемы ОЗУ

Элемент памяти может хранить 1 бит информации (лог.0, либо лог.1). Кроме того, он снабжен управляющими цепями для установки элемента в любой из трех режимов: режим хранения, в котором он отключается от входа и выхода микросхемы; режим записи, в котором в ЭП записывается новая поступающая со входа микросхемы информация и режим считывания, в котором из ЭП считывается информация.

Каждому ЭП приписан номер, называемый адресом элемента. Для поиска требуемого ЭП указываются строка и столбец, соответствующие положению ЭП в накопителе. Адрес ЭП в виде двоичного числа принимается по шине адреса в регистр адреса. Число разрядов адреса связано с емкостью накопителя. Числа строк и столбцов накопителя выбираются равными целой степени двух. И если число строк Nстр = 2n1, и число столбцов Nстолб = 2n2, то общее число ЭП (емкость накопителя)

N = NстрNстолб * 2n1 * 2n2 - 2n1+n2 = 2n,

где n = n1 + n2 – число разрядов адреса, принимаемого в регистр адреса.

Например, при емкости N = 210 = 1024 число разрядов адреса n = 10; при этом выбирается n1 = n2 = n/2 = 5, в этом случае число строк и число столбцов накопителя равно 2n1 = 2n2 = 32.

Разряды регистра адреса делятся на две группы: одна группа в n1 разрядов определяет двоичный номер строки, в которой в накопителе расположен ЭП, другая группа в n2 разрядов определяет двоичный номер столбца, в котором расположен выбираемый ЭП. Каждая группа разрядов адреса подается на соответствующий дешифратор: дешифратор строк и дешифратор столбцов. При этом каждый из дешифраторов создает на одной из своих выходных цепей уровень лог.1 (на остальных выходах дешифратора устанавливается уровень лог.0); выбранный ЭП оказывается под воздействием уровня лог.1 одновременно по цепям строки и столбца. При чтении содержимое ЭП выдается на усилитель чтения и с него на выходной триггер и выход микросхемы. Режим записи устанавливается подачей сигнала на вход разрешения записи (РЗ). При уровне лог.0 на входах РЗ открывается усилитель записи и бит информации со входа данных поступает в выбранный ЭП и запоминается в нем.

Указанные процессы происходят в том случае, если на входе выбора кристалла (ВК) действует активный уровень лог.0. При уровне лог.1 на этом входе на всех выходах дешифратора устанавливается уровень лог.0. При уровне лог.1на этом входе на всех выходах дешифратора устанавливается уровень лог.0 и ЗУ оказывается в режиме хранения.

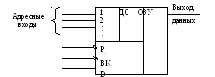

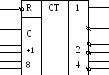

На рис. 3.35 показано условное графическое обозначение микросхемы ОЗУ.

Рисунок 3.35 - Условное графическое обозначение микросхемы ОЗУ

Микросхемы ОЗУ допускают наращивание емкости памяти путем наращивания разрядности и, следовательно, разрядности хранимых в них слов и наращивания числа ячеек и, значит, числа слов, которые можно хранить в памяти.

Таким образом, используя соответствующее число микросхем в определенном соединении, можно построить память с требуемой организацией.

Рассмотрим схему наращивания разрядности ячеек (рис.3.36). На все микросхемы подается один и тот же адрес. При чтении каждой микросхемой выдается определенный разряд считываемого слова. При записи входное слово поразрядно заносится в ЭП отдельных микросхем.

Рисунок 3.36 - Схема наращивания разрядности ячеек ЗУ

Таким образом, если микросхемы имеют организацию N∙1 (N одноразрядных ячеек), то для блока памяти N∙n (ячеек с разрядностью каждой из них, равной n) потребуется n микросхем.