- •Формализация словесного задания

- •Составление таблицы истинности

- •Запись функции в сднф

- •Минимизация логической функции.

- •Синтез схемы в базисе “и-не”

- •Учет коэффициента объединения по входу и коэффициента разветвления по выходу элементов при синтезе схем автоматов без памяти

- •Учет при синтезе схем коэффициента разветвления элементов по выходу

- •2.4. Шифраторы и дешифраторы

- •2.5 Синтез схем шифраторов

- •2.6 Синтез схем дешифраторов

- •Линейный дешифратор

- •Пирамидальный дешифратор

- •Прямоугольные матричные дешифраторы

- •2.7 Синтез преобразователей кодов

- •Принцип построения мультиплексоров

- •Принцип построения демультиплексора

- •Устройства проверки кодов на четность

2.5 Синтез схем шифраторов

При построении дискретных электронных схем широкое применение находят шифраторы как преобразователи некоторой позиции в соответствующий ей код. Необходимость в этом возникает, например, при телеуправлении, преобразовании кодов, посылке различных символов в линии связи, во входные устройства цифровых машин и т.д.

Шифратором называется схема с m входами и n выходами, в которой единичному сигналу на любом входе соответствует однозначно определенная комбинация сигналов на выходных шинах. Значение "1" в фиксированный момент времени может принимать сигнал только на одном входе. Условные обозначения шифратора приведены на рис. 2.25

Рисунок 2.25 - Условно-графическое изображение шифратора

Количество входов m и выходов n должно находиться в соотношении

m ≤ 2n

На условном обозначении шифратора входы помечаются десятичными обозначениями кодовых комбинаций, соответствующих им. Выходы помечают десятичными числами, указывающими двоичные веса позиций кода.

Рассмотрим принцип построения полного шифратора на четыре входа. Он должен иметь две выходные шины. Обозначив входные сигналы символами (Х0, X1, X2, Х3), а выходные – символами (Р0, P1), составим таблицу истинности для шифратора, формирующего только прямые сигналы.

|

Х0 |

X1 |

X2 |

Х3 |

P1(Х0, X1, X2, Х3) |

P1(Х0, X1, X2, Х3) |

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

Выходные сигналы описываются неполностью определенными переключательными функциями. На рис. 2.26 изображены карты Карно для этих функций P1(Х0, X1, X2, Х3) и P0(Х0, X1, X2, Х3)

Рисунок 2.26 - Карты Карно для функций шифратора

Минимальные ДНФ функции имеют вид

P1(Х0,

X1,

X2,

Х3)

= Х2

+ Х3

=

![]() (2.8)

(2.8)

P0(Х0,

X1,

X2,

Х3)

= X1

+ Х3

=

![]()

Таким образом, выходные сигналы могут формироваться как дизъюнкции входных сигналов, принимающих значение "1" в строках таблицы, в которых равны единице входные сигналы.

Это положение распространяется на любое число входов. Так, для полного шифратора на восемь входов, таблица истинности приведена в таблице 2.3. МДНФ функции будет следующими

P1(V)

= Х4

+ Х5

+ Х6

+ X7

=

![]()

P2(V)

= Х2

+

Х3

+ Х6

+ Х7

=

![]() (2.9)

(2.9)

P3(V)

= X1

+ ХЗ

+ Х5

+ Х7

=

![]()

где V = (Х1, X2, X3, …, Х7).

Таблица 2.3

|

Х0 |

Х1 |

Х2 |

Х3 |

Х4 |

Х5 |

Х6 |

Х7 |

P1 |

P2 |

P3 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

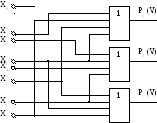

Структурные схемы, соответствующие табл. 2.2 и 2.3, и формулам (2.8) и (2.9), приведены на рис. 2.27а,б. На рис. 2.27а приведена схема шифратора на 4 входа, а на рис. 2.276 - восемь входов.

a)

б)

Рисунок 2.27 - Структурные схемы шифраторов

Необходимо отметить, что кодирование позиции Х0 осуществляется тривиально: она не соединяется ни с одной из выходных шин. Ее код (000) будет существовать на выходе не только при возбуждении шины Х0, но и в состоянии покоя, и при выключении схемы, и во многих случаях даже при неисправности шифраторa. Поэтому код (000) и соответствующую ему позицию (Х0) часто не используют.

Шифраторы удобно реализовать с помощью элементов "ИЛИ-НЕ", если применяются интегральные микросхемы.

Рассмотренные шифраторы относятся к преобразователям кода " 1 из n" в двоичный код 8421, Очень часто ограничения на количество нажимаемых клавиш оказывается неприемлемым и требуется построить шифратор так, чтобы он при определенном нажатии нескольких клавиш реагировал только на самый старший (или самый младший) из них. Преобразователи кода данного вида называют приоритетными шифраторами. Они реализуют преобразование кода "x из n" в код 8421. В таблице истинности (табл. 2.4) для приоритетного шифратора, в котором входные переменные с максимальными номерами имеют максимальный приоритет, значение входных переменных слева от диагонали из "1" не должны определять выходной код.

Таблица 2.4

|

номера клавиш |

f0 |

F1 |

f2 |

f3 |

f4 |

f5 |

f6 |

f7 |

f8 |

f9 |

Р3 |

Р2 |

Р1 |

Р0 |

|

* |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

i - |

* |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

2 |

* |

* |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

3 |

* |

* |

* |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

4 |

* |

* |

* |

* |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

5 |

* |

* |

* |

* |

* |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

6 |

* |

* |

* |

* |

* |

* |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

7 |

* |

* |

* |

* |

* |

* |

* |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

8 |

* |

* |

* |

* |

* |

* |

* |

* |

1 |

0 |

1 |

0 |

0 |

0 |

|

3 |

* |

* |

* |

* |

* |

* |

* |

* |

* |

1 |

1 |

0 |

0 |

1 |

Каждая

строка при нажатии одной клавиши

определяет входной код "1 из 10",

который преобразуется обычным образом

в код 8421. Если одновременно нажать

несколько клавиш, то формируется код

"x

из 10", который необходимо предварительно

преобразовать в код "1 из 10", а затем

уже в код 8421. Если обозначить выходные

переменные преобразователя кода "x

из 10" через х0,

x1,...,

X9,

то функции преобразователя кода "x

из 10" в код "1 из 10" можно записать

следующим образом. Входная переменная

f9

имеет максимальный приоритет, поэтому

не зависит от других переменных. Любая

другая выходная переменная xi

принимает

значение "1", если fi

= 1  при

условии, что ни на один из "старших"

входовfj,

j

=

при

условии, что ни на один из "старших"

входовfj,

j

=

![]() не подана логическая единица, т.е

не подана логическая единица, т.е

X 1

= f1(X2

+ Х3

+ ... + Х9);

1

= f1(X2

+ Х3

+ ... + Х9);

Х2 = f2(X3 + Х4 + ... + Х9);

(2.10)

Х7 = f7(X8 + Х9);

Х8 = f8 X9;

Х9 = f0

Схема преобразователя кода "x из 10" в код "1 из 10", построенная на основе выражения (2.10), приведена на рис. 2.28а. К достоинству этой схемы можно отнести равномерную задержку распространения сигналов по всем входам, а к недостатку – необходимость применения многовходных схем ИЛИ-НЕ. Как правило, при клавиатурном вводе, где не требуется большого быстродействия, схему преобразователя кода "x из 10" в код "1 из 10" можно построить по итерационному принципу (рис. 2.286). В этой схеме сигнал приоритетного запрета распространяется от старшего входа к младшему через последовательно соединенные элементы ИЛИ. Длительность преобразования определяется временем установки сигнала на выходе X1, запаздывание на котором максимально.

a)

б)

Рисунок 2.28 - Схемы преобразователей кодов "X из 10" в код "1 из 10"