Конвейер cpu

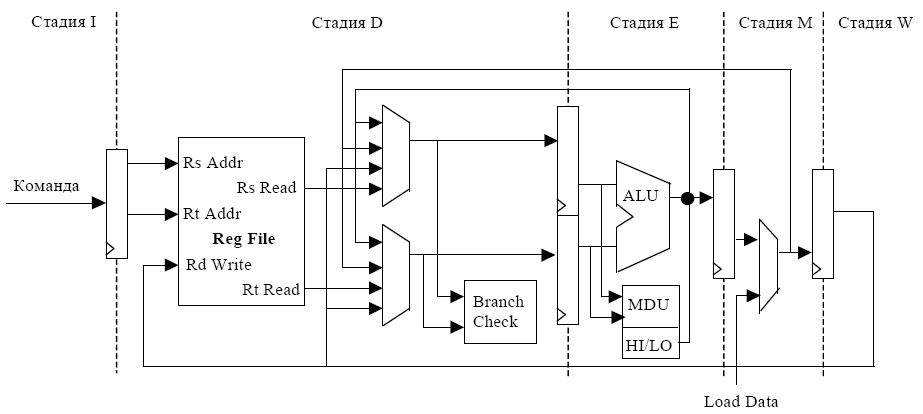

В RISC-ядре процессора реализован конвейер, состоящий из пяти стадий:

Выборка команды (стадия I- Instruction)

Дешифрация команды (стадия D - Data)

Исполнение команды (стадия E - Execution)

Выборка из памяти (стадия M - Memory)

Обратная запись (стадия W – Write Back)

Конвейер осуществляет выполнение команд перехода с задержкой в один такт. Однотактная задержка является результатом функционирования логики, ответственной за принятие решения о переходе на стадии D конвейера. Эта задержка позволяет использовать адрес перехода, вычисленный на предыдущей стадии, для доступа к команде на следующей D-стадии. Слот задержки перехода (branch delay slot) позволяет отказаться от остановок конвейера при переходе.

После исполнения на ALU результат, в принципе, готов для использования другими командами. Но запись результата в регистровый файл осуществляется только на стадии W. Это лишает следующую команду возможности использовать результат в течение 3-х циклов, если ее операндом является результат выполнения последней операции, сохраненный в регистровом файле. Для преодоления этой проблемы используются обходные пути передачи данных. Мультиплексоры обходных путей передачи данных для обоих операндов располагаются между регистровым файлом и ALU (рисунок 3).

Рис. 3. Обходные пути передачи данных

Данные, выбираемые командами загрузки (Load), становятся доступными на конвейере только после выравнивания на стадии M. При этом данные, являющиеся исходными операндами, должны предоставляться командам для обработки уже на стадии D. Поэтому, если сразу за командой загрузки следует команда, для которой один из регистров исходных операндов совпадает с регистром, в который производится загрузка данных, это вызывает приостановку в работе конвейера на стадии D. Эта приостановка осуществляется аппаратной вставкой команды NOP. Во время этой задержки часть конвейера, которая находится дальше стадии D, продолжает продвигаться.

Цифровой сигнальный процессор (dsp)

В состав процессора 1892ВМ10Я входит 2-ядерный DSP-кластер DELcore-30М - симметричный мультипроцессор (СМП), состоящий из 2-х DSP-ядер ELcore-30М - DSP0 и DSP1, работающих на общем поле памяти данных, имеющих набор общих регистров управления/состояния, а также буфера обмена XBUF.

Кластер DSP представляет собой 2-ядерную MIMD систему. Каждое DSP ядро обладает собственной программной памятью, и может работать независимо. Для синхронизации работы DSP ядер в кластере предусмотрено два механизма: механизм прерываний и механизм обменов через XBUF в синхронном режиме.

Каждое из двух DSP-ядер ELcore-30М представляет собой ядро сопроцессора-акселератора сигнальной обработки. Оно имеет гарвардскую архитектуру с внутренним параллелизмом по потокам обрабатываемых данных и предназначено для обработки информации в форматах с фиксированной и с плавающей точкой. Система инструкций, реализующих параллельно несколько вычислительных операций и пересылок, 7-фазный программный конвейер и гибкие адресные режимы позволяют реализовать алгоритмы сигнальной обработки с высокой производительностью. Каждое DSP-ядро функционирует под управлением CPU-ядра и расширяет его возможности по обработке сигналов.

В качестве отличительных особенностей цифрового сигнального процессора можно назвать: