Национальный исследовательский ядерный университет «МИФИ»

|

Факультет Кибернетики и информационной безопасности

Кафедра «Компьютерные системы и технологии»

|

Реферат по предмету

«Архитектура вычислительных систем»

на тему:

Микропроцессор 1892ВМ10Я

Студент гр. К1-12М Агеева А. В.

Руководитель Чепин Е. В.

Москва 2012

Оглавление

Общие сведения 3

Взаимодействие процессоров 7

Центральный процессор (CPU) 9

Конвейер CPU 12

Цифровой сигнальный процессор (DSP) 14

Конвейер DSP 19

Структурная нотация 22

Список литературы 24

Общие сведения

Микросхема интегральная 1892ВМ10Я («Навиком-02Т») спроектирована и изготовлена по 130-нм проектным нормам как однокристальная трехъядерная гетерогенная многопроцессорная “система на кристалле” на базе библиотек отечественной платформы проектирования микросхем «МУЛЬТИКОР», разработанной в ОАО НПЦ «ЭЛВИС» совместно с партнерами.

Микросхема продолжает ряд микропроцессоров серии «Навиком» («Навиком-01»), предназначенных для одновременного решения задач связи, навигации, обработки видео и графической информации на базе одной и той же микросхемы. В настоящее время портированы ОС Linux с поддержкой приложений и RTOS uOS, а в перспективе планируется портирование ОС Android и QNX.

В качестве процессоров микросхема 1892ВМ10Я содержит 32-разрядный центральный процессор (CPU) на основе процессорного RISC-ядра RISCore32F64 с архитектурой MIPS32 и два высокопроизводительных DSP процессора-акселератора в составе “DELCore-30М (Dual ELCore-30М)” для цифровой обработки сигналов с плавающей и фиксированной точкой, обеспечивающих обработку информации с переменными форматами данных.

Все процессоры работают независимо друг от друга (каждый по своей собственной программе) и, вследствие этого, представляют трехъядерную систему на кристалле MIMD–архитектуры (MIMD – Multiple Instructions Multiple Data).

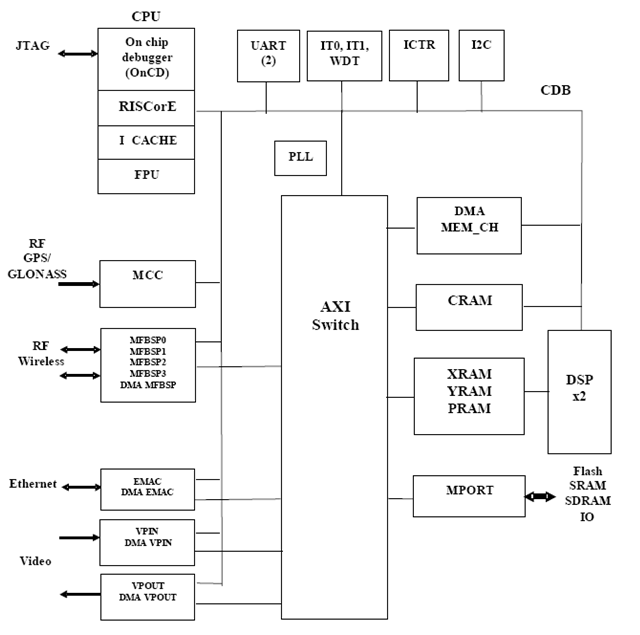

Структурная схема микросхемы 1892ВМ10Я приведена на рисунке 1.

Рис. 1. Структурная схема 1892ВМ10Я

Важнейшими устройствами в структуре процессора являются интеллектуальные устройства прямого доступа (DMA), которые могут обеспечивать взаимную синхронизацию, к примеру, c DSP –ядрами.

При этом возможны два варианта MIMD–организации:

CPU–ядро осуществляет функцию главного менеджера исполняемой программы, руководит DSP-ядрами и устройствами DMA, а DSP–ядро является интеллектуальным акселератором, работающим по собственной программе и обладающим возможностью самоинициализации по выполнению своей программы. CPU-ядро имеет доступ ко всем ресурсам процессора.

И CPU-, и DSP–ядра имеют возможности доступа к ресурсам микросхемы. DSP–ядра имеют доступ ко всему адресному пространству микросхемы, в том числе к регистрам DMA–каналов и периферийных блоков. При одновременном доступе к одним и тем же ресурсам приоритет предоставляется CPU.

Кроме того, широкое использование в структуре процессора двухпортовых ОЗУ обеспечивает их одновременное использование парами CPU/DSP, CPU/DMA или DSP/DMA. Поэтому параметры реальной производительности устройств процессора близки к пиковым, так как ввод и вывод данных и промежуточных результатов процессорных ядер возможен одновременно с основными вычислениями.

В микросхему также встроен многоканальный аппаратный коррелятор (МСС) для обработки навигационной информации для ГЛОНАСС/GPS-навигации, который функционирует независимо от работы CPU и DSP.

Порт внешней памяти (MPORT) со встроенным контроллером служит для подключения к микропроцессору внешней памяти типов SRAM/ROM/SDRAM/Mobile SDRAM/EPROM/FLASH и внешних устройств. Шина данных – 32 разряда, шина адреса – 32 разряда.

Для передачи данных в 1892ВМ10Я имеются: шина CDB (CPU Data Bus) и коммутатор AXI Switch. Коммутатор обеспечивает передачу данных между любым исполнительным устройством (Slave) и любым задатчиком (Master). При этом процесс передачи данных между любыми парами Slave-Master выполняется параллельно и без конфликтов.

Исполнительными устройствами являются блоки внутренней памяти, (CRAM, память DSP) или любая внешняя память, доступная через MPORT. Задатчиками могут быть CPU, MFBSP, Ethernet MAC (EMAC)и каналы DMA типа память-память.

Периферийные устройства микросхемы 1892ВМ10Я:

контроллер Ethernet MAC 10/100 МГц;

4 универсальных порта MFBSP (LPORT, совместимый с Analog Device, SPI, I2S, GPIO) с DMA;

4 - канальный контроллер прямого доступа (DMA) типа память-память. Поддержка 2-мерной и разрядно-инверсной адресации. 4 внешних запроса прямого доступа;

Контроллер прерываний. 4 внешних прерывания;

порт ввода видеоданных;

порт вывода видеоданных;

два универсальных асинхронных порта (UART) типа 16550;

два универсальных 32-разрядных таймера, интервальные/реального времени (IT/RTT);

32-разрядный сторожевой таймер (WDT).