Cortex-a9 mpCore

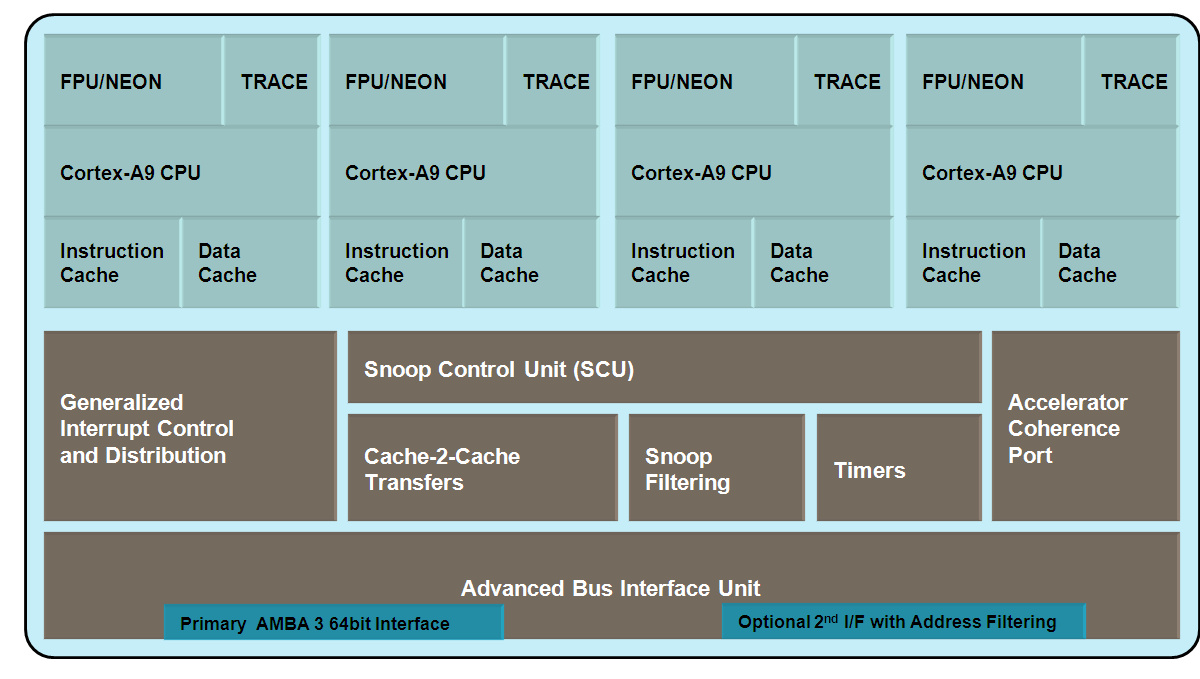

Процессор Cortex-A9 MPCore (рисунок 5) состоит из:

От 1 до 4 процессоров Cortex-A9 в кластере и модуля управления поиском данных (Snoop Control Unit), который может использоваться для обеспечения когеретности в кластере;

Набора частной отображенной в память периферии, включая глобальный таймер и сторожевой таймер, для каждого процессора Cortex-A9 в кластере;

Встроенного контроллера прерываний, который является реализацией GIC (General Interrupt Controller) архитектуры. Регистры встроенного контроллера прерываний расположены в конфиденциальной области памяти процессора Cortex-A9 MPCore.

Рис. 5. Схема процессора Cortex-A9 MPCore

Процессоры Cortex-A9 в составе Cortex-A9 MPCore могут быть сконфигурированы независимо друг от друга. Для упрощения работы ПО, ARM рекомендует использовать единую конфигурацию для всех процессоров.

Основные опции конфигурирования Cortex-A9 MPCore:

Один или два интерфейса ведущего порта AXI с возможностью фильтрации адреса;

Опциональный порт ускорения согласования (Accelerator Coherency Port);

Конфигурироемое число линий прерываний.

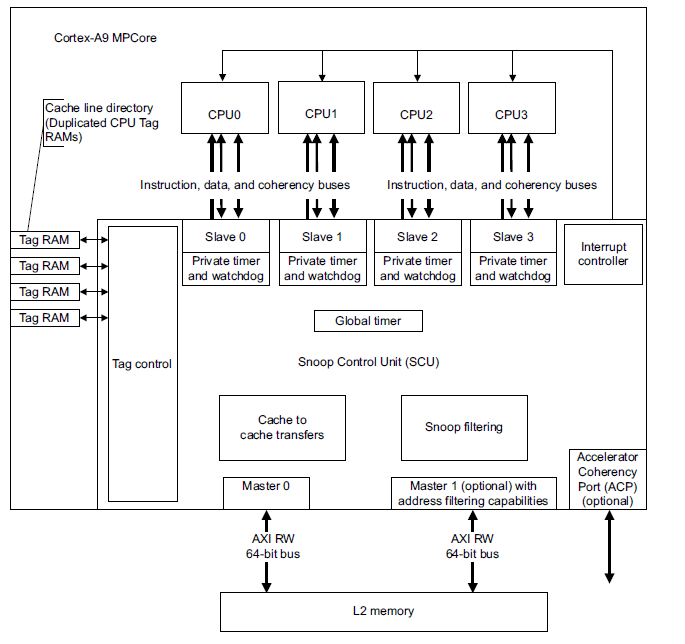

Структура Cortex-A9 MPCore из 4 процессоров представлена на рисунке 6.

Рис. 6. Структура 4-х ядерного процессора Cortex-A9 MPCore

Snoop Control Unit

SCU – центральный интеллект в многопроцессорной ARM системе, он отвечает за управление межпроцессорным соединением, арбитрацию, связь, передачу информации cache-2-cache и в системной памяти, когерентность кэш и другие многопроцессорные возможности для всех процессоров с технологией MPCore.

Cortex-A9 MPCore предоставляет эти возможности и другим системным ускорителям и некэшироемому прямому доступу к памяти, управляемому периферией, для повышения производительности и сокращения потребляемой мощности всей системы, путем разделения доступа к иерархии кэша процессора.

Accelerator Coherence Port

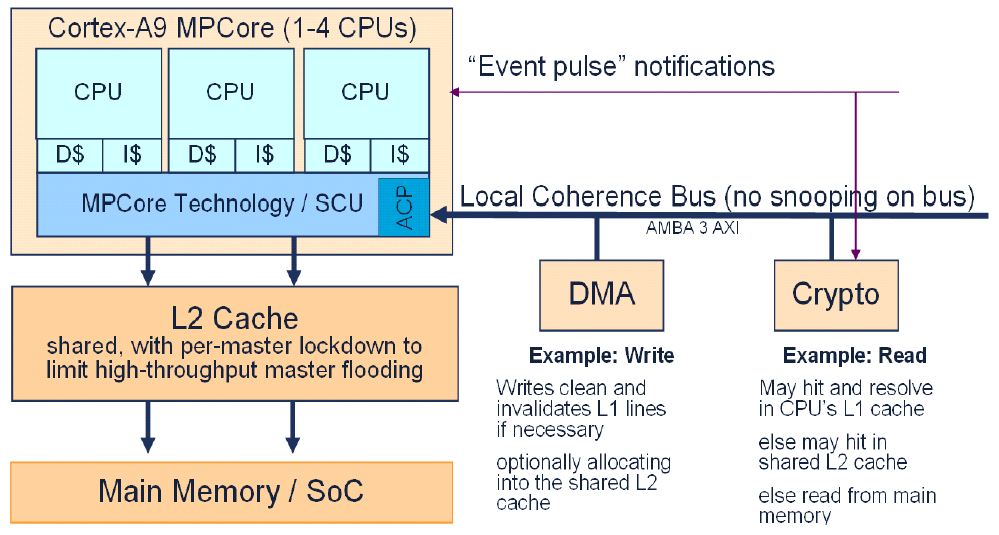

ACP – ведомый интерфейс в SCU, совместимый с AMBA 3 AXI, предоставляет точку соединения для набора системных ведущих устройств, которым по каким-либо причинам (производительность, потребляемая мощность или структура ПО) желательна связь напрямую с процессором Coretex-A9 MPCore. Данный интерфейс работает как стандартное ведомое устройство AMBA 3 AXI и поддерживает все стандартные операции чтения и записи без дополнительных условий когерентности, накладываемых на присоединенные компоненты. Схема подключения ACP представлена на рисунке 7.

Рис. 7. Применение ACP

Каждая операция чтения из когерентной области памяти будет взаимодействовать с SCU, чтобы проверить находится ли запрашиваемая информация уже в кэш L1 процессора. В случае нахождения, информация возвращается напрямую запрашивающему устройству. Если информации нет в L1, перед обращением в основную память, проводится проверка кэш L2.

При операции записи в когерентную область памяти SCU принудительно установит когерентность перед записью в систему памяти. Опционально операция может быть проведена в кэш L2, для сокращения затрат питания и мощности, необходимых для записи непосредственно во внешнюю память.

Advanced Bus Interface

Доступны конфигурации с одним или двумя 64-разрядными ведущими интерфейсами AMBA 3 AXI. Полная нагрузка межсистемного соединения может составлять более чем 12ГБ/с на скорости ядра. Дополнительно второй интерфейс может установить фильтр транзакций для разделения глобального адресного пространства для обеспечения гибкости адресных подсистем на уровне структуры процессора.

Каждый интерфейс может предоставлять различное соотношение частоты CPU и шины, включая синхронную половинную тактовую частоту, для повышения гибкости проектирования и улучшения системной пропускной способности. Так же поддерживаются дополнительные возможности по управлению энергопотреблением.

Контроллер кэш L2

ARM контроллер кэш L2 PrimeCell PL310 подходит для поддержки нескольких незавершенных AXI транзакций на каждом интерфейсе с блокировкой на ведущее устройство на канал, что позволяет управлять совместным применением несколькими CPU или компонентами, использующими ACP.

PL310 включает в себя возможности порта ускорения согласования и также предоставляет поддержку синхронной половинной тактовой частоты для сокращения задержек высокоскоростного процессора, и возможности фильтрации адреса второго ведущего AXI интерфейса для разделения доменов, частот и быстрого доступа к встроенной памяти.

Поддерживая до 8МБ 4-х или 16-ти ассоциативной кэш памяти L2, PL310 обеспечивает возможность дополнительной интеграции с RAM и способен работать на одной частоте с процессором. Усовершенствованный механизм блокировок позволяет использовать кэш для передачи данных между устройствами ACP и процессорами.

Структурная нотация

P(Cortex-A9 MPCore)SMP = 4P̅(Cortex-A9)RISC↔SCU↔Csh2128KB(128KB-8MB)

P(Cortex-A9)RISC = IP32[EP, Cshi116KB(16KB, 32KB, 64KB), Cshd116KB(16KB, 32KB, 64KB)]

EP = {E1(ALU), E2(Advanced SIMD and FP)}

E1(ALU) = {BP32, BP32(*), 13Rg32}

E2(Advanced SIMD and FP) = {BP8,16,32,64, FP16,32,64, 16Rg128}

Список литературы

ARM Architecture & NEON, Ian Rickards, Stanford University, 28 Apr 2010

Cortex-A9 MPCore Technical Reference Manual (Rev. r4p1), ARM Ltd, 15 июня 2012

Cortex-A9 NEON™ Media Processing Engine (Rev. r4p1), ARM Ltd, 15 июня 2012

Cortex-A9 Technical Reference Manual (Rev. r4p1), ARM Ltd, 15 июня 2012

The ARM Cortex-A9 Processors (Rev. 2.0), ARM Ltd, 2009

Процессорные ядра семейства Cortex, Д.Козлов-Кононов, ЭЛЕКТРОНИКА: Наука, Технология, Бизнес 8 / 2010