- •1. Кс як об'єкт дослiдження.

- •2. Принцип дiї кс.

- •3. Принципи фон Неймана та Лєбєдєва побудови кс.

- •4. Класифiкацiя кс. Класифiкацiя за призначенням.

- •5. Класификацiя кс за функцiональним призначенням.

- •7. Класифiкацiя кс за швидкодiєю.

- •8. Базовi шляхи пiдвищення продуктивностi та надiйностi кс.

- •9. Apxiтeктypa набору команд.

- •10. Органiзацiя пам'ятi. Шляхи пiдвищення продуктивностi.

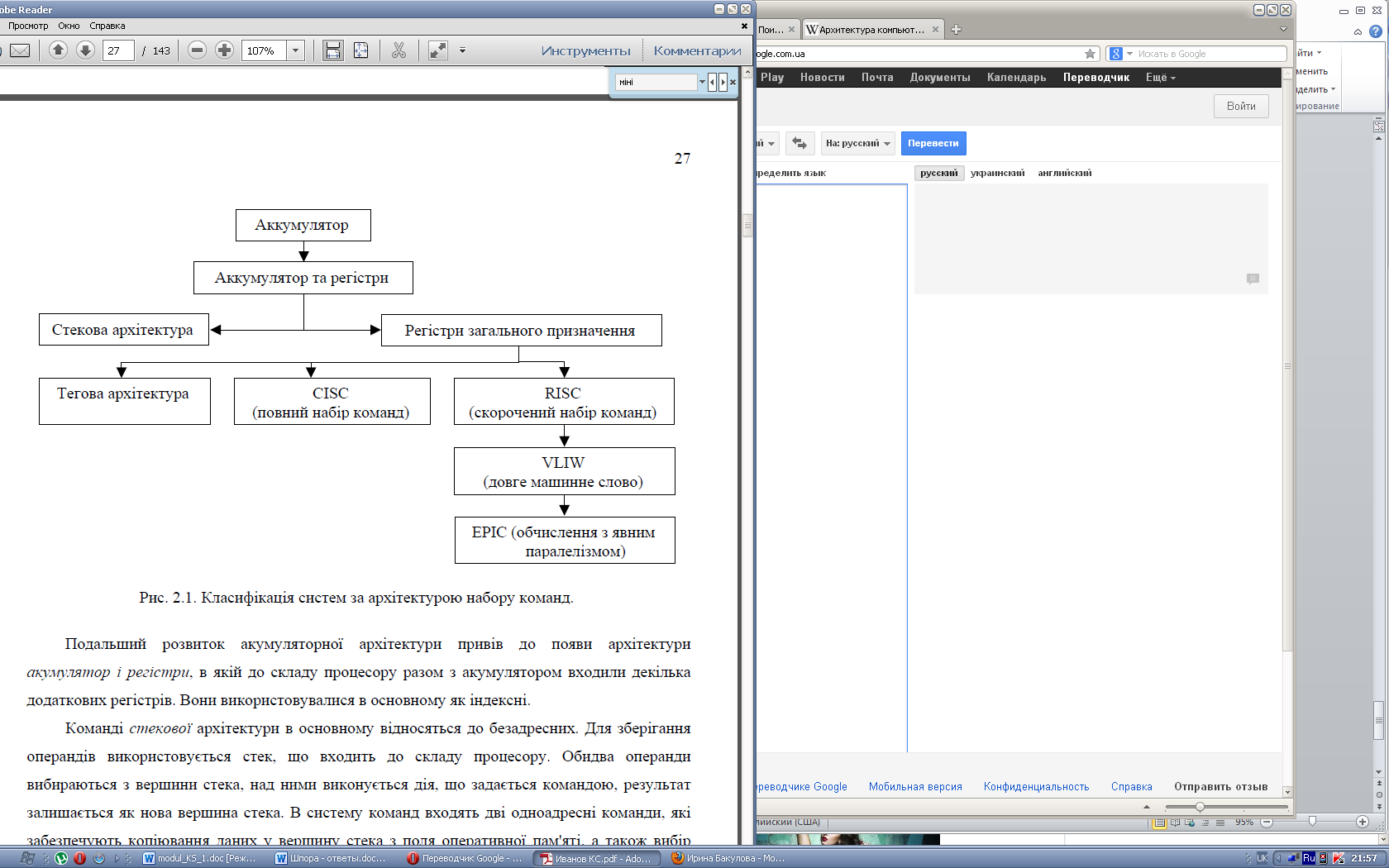

9. Apxiтeктypa набору команд.

З нати:

акумуляторна, стекова,

peгіcтрів

загального призначення,

CISC, RISC, VLIW, EPIC архiтектури,

їх ознаки.

нати:

акумуляторна, стекова,

peгіcтрів

загального призначення,

CISC, RISC, VLIW, EPIC архiтектури,

їх ознаки.

Аккумуляторная архитектура В этой архитектуре основой арифметико-логического устройства является единственный регистр, который называется аккумулятором. Типичная команда выбирает операнд из оперативной памяти и использует его в операции с аккумулятором, где, при необходимости, уже должен находиться второй операнд. Результат остается в аккумуляторе. Система имеет две команды, которые могут работать с оперативной памятью. Одна команда необходима для загрузки в аккумулятор процессора из оперативной памяти, а вторая - для записи кода из аккумулятора в память.

Типичный пример последовательности машинных команд для такого процессора имеет вид:

load Ра; загрузка у акумулятор з ОП

add Pb ; складання

store Рс ; запис результату в ОП

Здесь Ра и Pb представляют адреса полей оперативной памяти, в которых находятся приложения, а Рс - адрес поля для записи результата.

Дальнейшее развитие аккумуляторной архитектуры привело к появлению архитектуры аккумулятор и регистры, в которой в состав процессора вместе с аккумулятором входили несколько дополнительных регистров. Они использовались в основном как индексные.

Команды стековой архитектуры в основном относятся к безадресным. Для хранения операндов используется стек, который входит в состав процессора. Оба операнда выбираются из вершины стека, над ними выполняется действие, которое задается командой, результат остаётся как новая вершина стека. В систему команд входят две одноадресные команды, которые обеспечивают копирование данных в вершину стека с поля оперативной памяти, а также выбор кода с вершины стека и запись в поле оперативной памяти.

push Ра ;запис першого операнда у вершину стека з ОП

push Pb ;запис другого операнда у вершину стека з ОП

add ;складання

pop Рс ;вибір результату з вершини стека і запис в ОП

Архитектура регистров общего назначения отличается тем, что процессор располагает набор высокоскоростных регистров, который принято называть регистровой

памятью или регистровый файл. В отличие от стековой архитектуры, операнды команд могут выбираться из любого регистра и записываться в любой регистр процессора.

Различают две большие группы архитектуры регистров общего назначения: с полным и сокращенным набором команд. Эти группы являются идеализированными (модельными). Любой реальный процессор фактически занимает некоторое промежуточное положение с преобладанием особенностей той или иной модели.

К архитектуре регистров общего назначения относится и так называемая теговая архитектура, отличительной особенностью которой является наличие связанного с каждым стандартным полем оперативной памяти аппаратно управляемого тега. В данном случае тег - это некоторый признак, определяющий типы данных, допустимых для поля, а также множеством команд, применяемых к нему.

CISC-архитектура. Особенностью этой разновидности архитектуры является наличие отдельной машинной команды для каждого возможного действия по обработке данных.

Для CISC характерно:

- Сравнительно небольшое число регистров общего назначения;

- Большое количество машинных команд, некоторые из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и для выполнения которых необходимо несколько тактов работы процессора;

- Большое количество методов адресации;

- Большое количество форматов команд различной разрядности;

- Преобладание двухадресных формата команд;

- Наличие команд обработки типа регистр-память;

- Развитый механизм адресации операндов, включает различные методы косвенной адресации.

К архитектуре CISC относятся системы команд семейств IBM 360/370, VAX, Intel 80x86, в том числе система команд машины IBM PC с процессором i8086.

RISC-архитектура - компьютер с сокращенным набором инструкций. В этом подходе предполагается включение в систему команд процессора только простых действий, которые часто встречаются. Реализация сложных операций над данными осуществляется с помощью последовательностей простых команд.

Система команд такого компьютера содержит только микрокоманды. Для архитектуры RISC характерно:

- Она построена на архитектуре, отделяющей команды обработки от команд работы с памятью;

- Упор на эффективную конвейерную обработку;

- Система команд разрабатывалась так, чтобы выполнение любой команды занимало небольшое количество машинных тактов (предпочтительно один машинный такт);

- С целью повышения производительности логика выполнения команд ориентируется на аппаратную, а не на микропрограммную реализацию;

- Для упрощения логики декодирования команд используются команды фиксированной длины и фиксированного формата;

- Большой регистровый файл: 32 и более регистров общего назначения;

- Частое использование трехадресных команд, дополнительно дает возможность хранить большое количество переменных в регистрах без их последующей перезагрузки;

- Использование только простых способов адресации (регистровая, прямая, непосредственная).

К RISС-архитектуре относят семейства SUN SPARC, Аlpha, Power PC, MIPS и некоторые другие....

Архитектура VLIW является разновидностью RISС-архитектуры. Архитектура процессоров этой группы - суперскалярная, с наличием большого количества арифметико-логических функциональных блоков. Основным ее отличием является возможность объединения нескольких простых команд в так называемые связи. Команды, которые в нее входят, должны быть независимы друг от друга, то есть их можно выполнять одновременно, параллельно. Таким образом, из нескольких независимых машинных команд транслятор формирует одно «очень длинное командное слово».

VLIW используют специальную систему команд и поэтому несовместимы с системой команд процессоров семейства Intel 80x86.

Архитектура EPIC является развитием VLIW-архитектуры. Отличительной чертой EPIC-архитектуры является устранение отмеченных недостатков VLIW-архитектуры, требовавших, например включение группы пустых команд для заполнения машинных тактов, возникающие при реализации параллельного выполнения некоторых команд.

Характерные особенности EPIC-архитектуры:

- Хорошая масштабируемость функциональных блоков процессора;

- Параллелизм, явно задается в машинном коде

- Предикативной выполнения команд.

Количество процессоров, входящих в состав одной вычислительной системы, уже в настоящее время исчисляется десятками тысяч. Поэтому проблеме масштабируемости в архитектуре EPIC уделяется много внимания.

Задание параллелизма в команде EPIC-архитектуры призвано упростить и ускорить работу процессора, а предиктативное выполнение фактически превращает обработку разветвлений на параллельное выполнение нескольких линейных фрагментов программы, лишает конвейерную схему от проблем с очисткой и заполнением конвейера.