- •Краткие сведения о системе автоматизированного проектирования цифровых устройств – Xilinx ise.

- •Программируемые логические интегральные схемы

- •Система автоматизированного проектирования Xilinx ise.

- •2. Создание проекта

- •2.2. Создание принципиальной схемы.

- •3. Проверка работоспособности схемы

- •Реализация на языке vhdl

- •Содержание отчета

- •Контрольные вопросы

3. Проверка работоспособности схемы

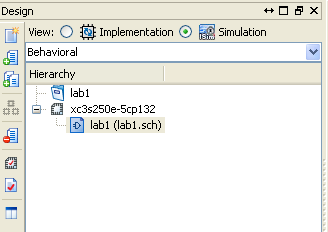

Обычно после того, как был создан проект с помощью схемотехнического редактора, перед этапом автоматизированного размещения проекта в кристалле, должен быть этап предварительного функционального моделирования для выявления ошибок и проверки работоспособности проектируемого проекта или отдельных его частей. Проверка работоспособности схемы производится при помощи симулятора ISim. Для этого в режиме симуляции выделяется исследуемая схема (рис.19.а) и запускается ISim Simulator (рис. 19.б).

Рис 19 (а, б). Запуск режима симуляции проекта.

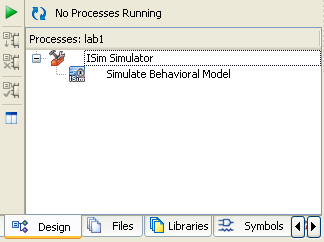

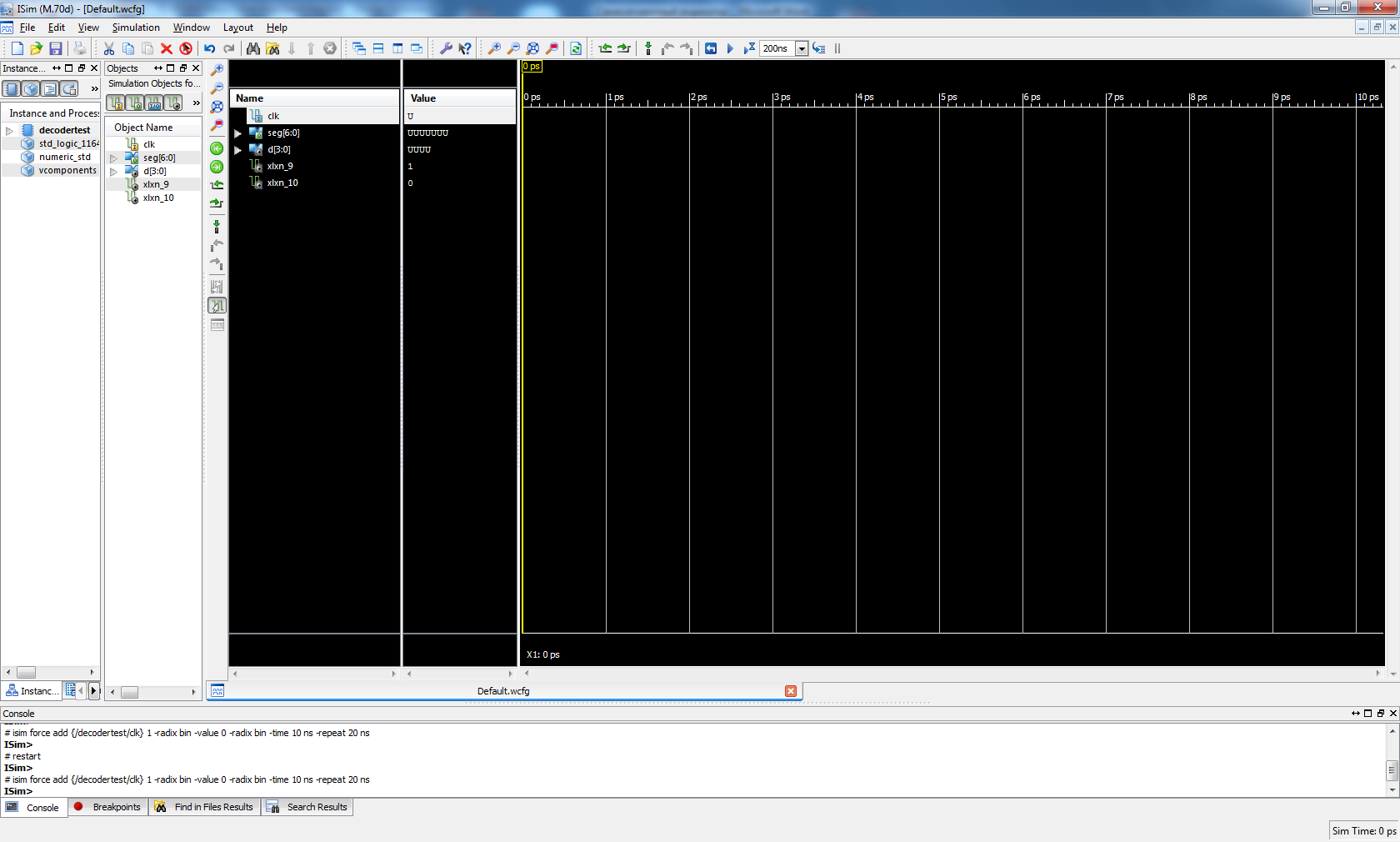

Рис. 20. Рабочее окно симулятора

После открытия окна симулятора следует выполнить следующие действия:

1.

Сбросить текущие настройки

![]() ;

;

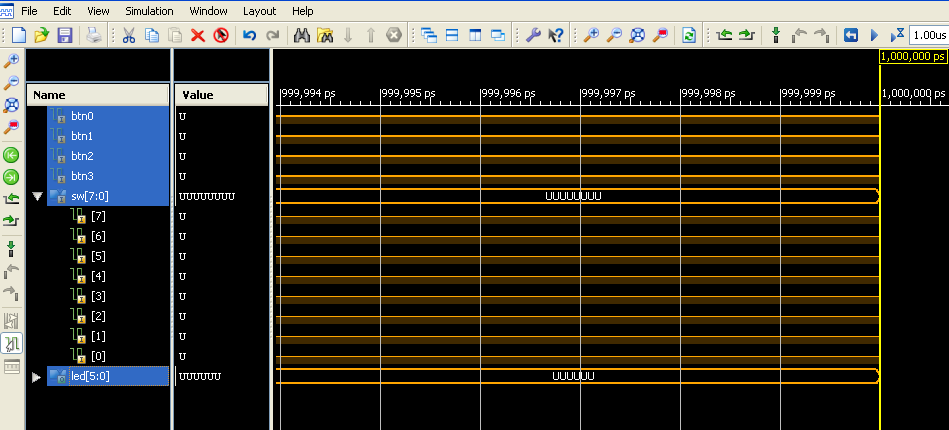

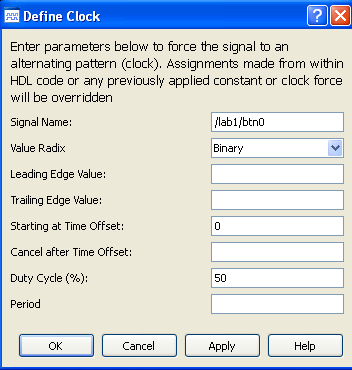

2. Настроить параметры входных сигналов (Рис. 21). Для этого следует выделить каждый из источников сигнала и в меню Force Clock задать его параметры.

Рис.21. Меню настройки источников сигнала.

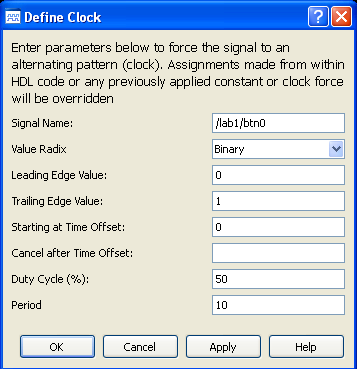

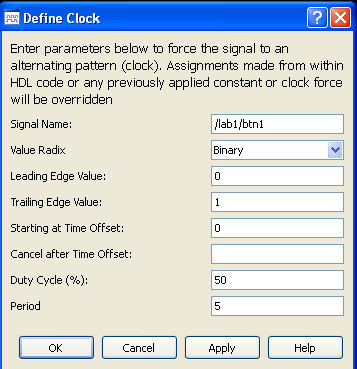

На примере настроек btn0 и btn1, проверим работу элемента AND. Задаваемые параметры приведены на рис. 22a – для btn0 и рис.22б – для btn1.

a b

Рис. 22.

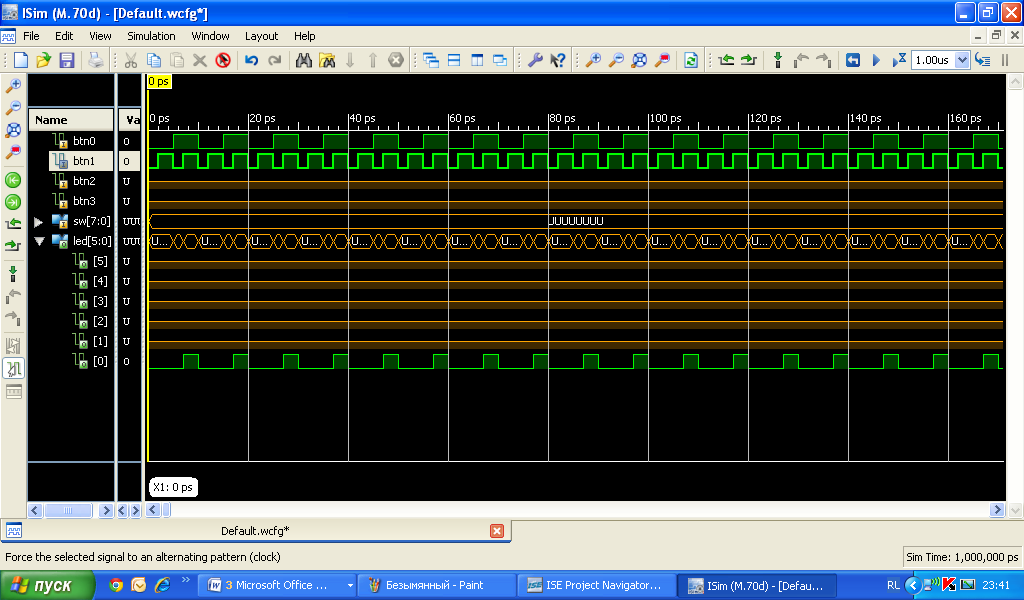

Устанавливается шаг времени наблюдения равный 1 us

,

данная величина из расчета. Затем

выполняется запуск схемы

,

данная величина из расчета. Затем

выполняется запуск схемы .

.

Рис. 23. Временная диаграмма работы элемента AND.

Основываясь на полученных данных, составляется таблица истинности для элемента “логическое И”, которая сравнивается с таблицей приводимой в литературе. На основе этого сравнения можно сделать вывод о правильности работы схемы. Аналогичным образом можно проверить работоспособность каждого элемента представленной схемы.

Подключение схемы к внешним выводам ПЛИС и загрузка файла конфигурации в ПЛИС. После того, как произведена компиляция проекта следует выполнить прошивку ПЛИС. Для этого необходимо скомпоновать файл конфигурации с расширением *.bit на устройство. Выбираем меню Пусквсе программыDigital Adeptвыбираем свой файл в папке Lab.1открытьнажать кнопку program. Прошивка схемы закончена.

Реализация на языке vhdl

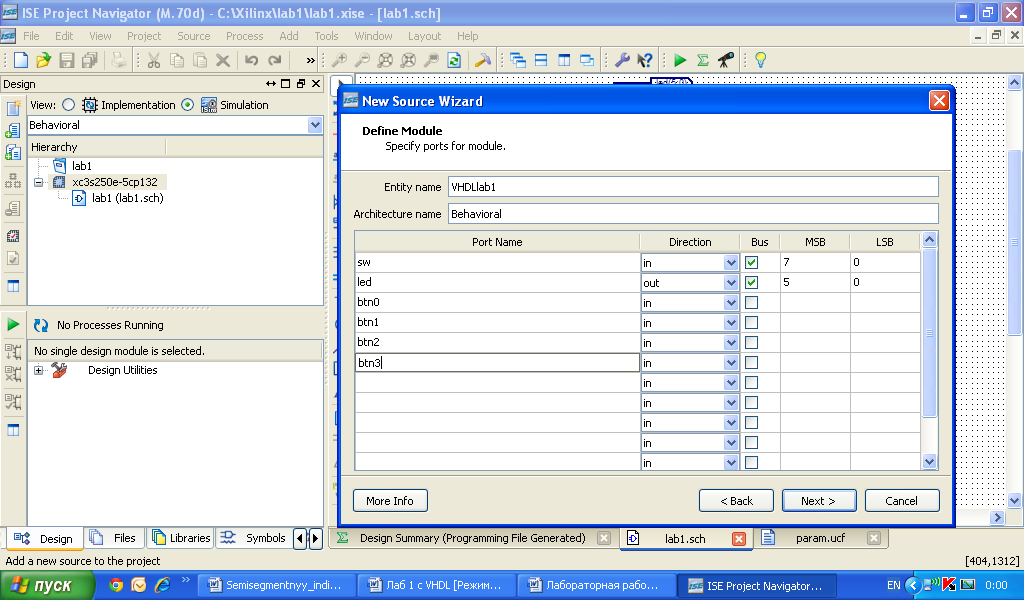

Для начала создается модуль VHDL “DecoderLogicVHDL.vhd”. Для этого в меню New Source выбираем Implementation Constraints File и называем создаваемый файл. В появившемся окне указываем все имеющиеся входы и выходы схемы (Рис. 24).

Рис. 24. Инициализация выводов схемы.

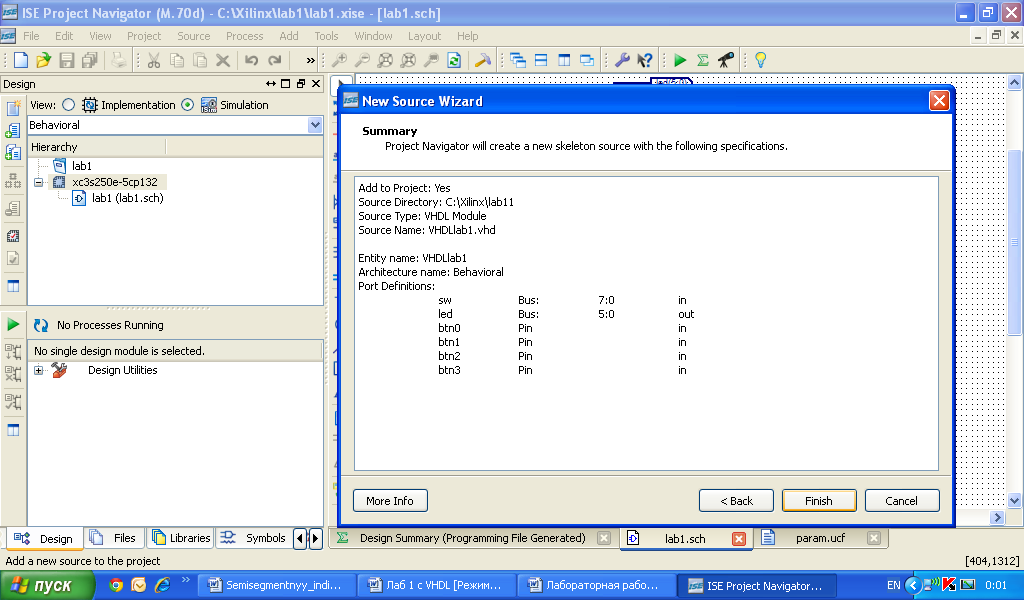

По завершению этой операции нажимаем Next, появляется окно, в котором описан результат инициализации выводов схемы (Рис.25). Проверив правильность обозначения выводов, завершаем этот этап нажатием Finish.

Рис. 25. Результат обозначения выводов проекта.

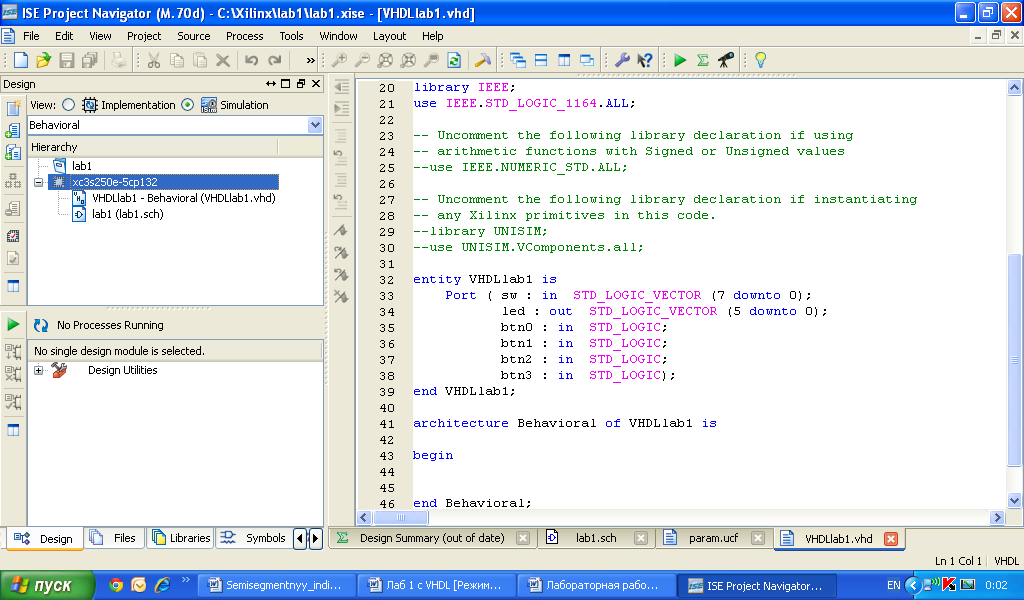

Входные и выходные параметры модуля могут в последующем изменяться. После нажатия кнопки Finish будут создан файл модуля (рис. 26) со следующим базовым текстом:

Рис. 26. Базовый файл VHDL.

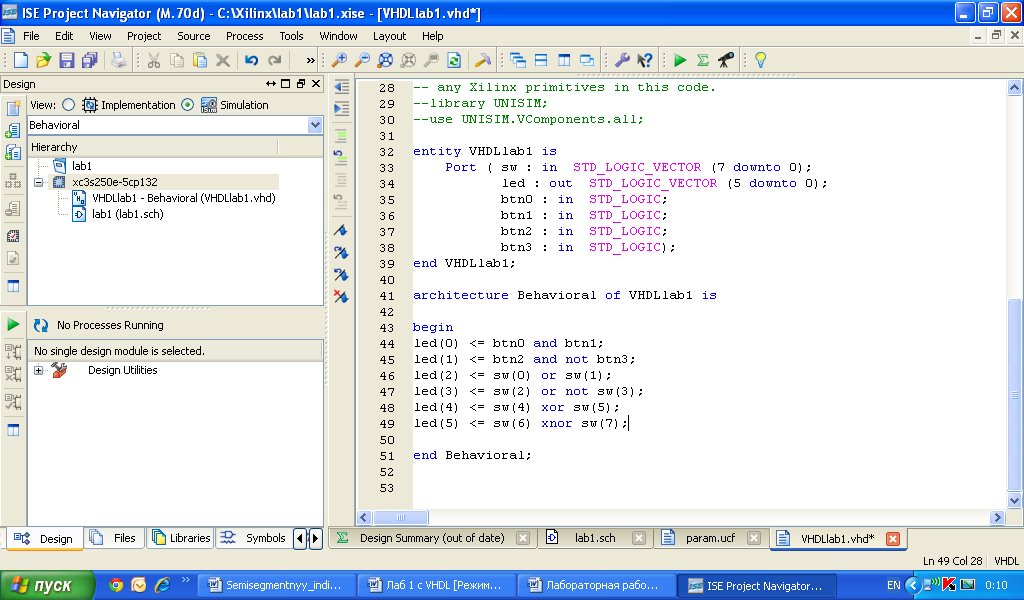

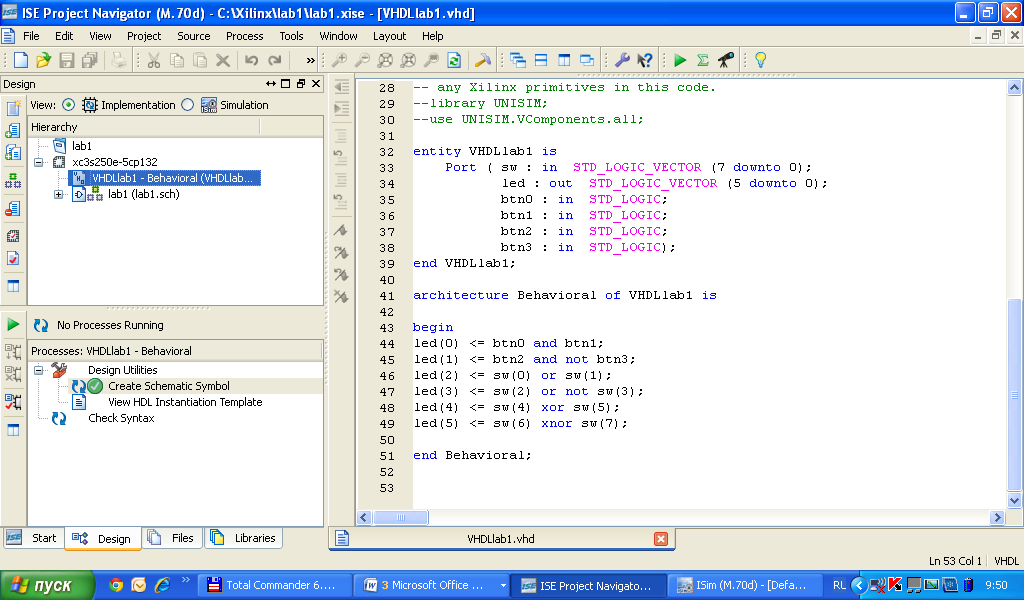

Далее после слова begin записываются логические уравнения для каждого сегмента (Рис. 27).

Рис. 27. Описание логических уравнений для каждого элемента.

Затем путем нажатия кнопки Create Schematic Symbol в режиме Implementation (рис.28.б) создается визуальный компонент для данного модуля.

Рис. 28. Создается визуальный компонент.

Для проверки модуля запускается симулятор. Проверка работоспособности схемы является аналогичной приведенной в пункте 3.