- •Лекция 14 Импульсные устройства автоматики и вычислительной техники

- •14.1 Общая характеристика импульсных устройств

- •14.2 Электронные ключи и простейшие формирователи импульсных сигналов

- •14.3 Логические элементы

- •14.4 Триггеры

- •14.5 Цифровые счётчики импульсов

- •14.6 Регистры, дешифраторы

- •14.7 Компараторы и триггеры Шмитта

- •14.10 Цифроаналоговые и аналого-цифровые (цап и ацп) преобразователи

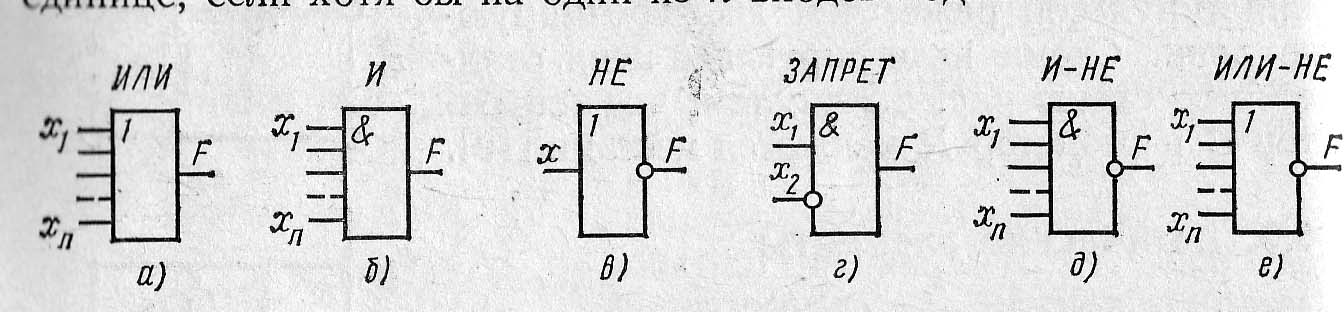

14.3 Логические элементы

Логические элементы вместе с запоминающими элементами составляют основу устройств цифровой (дискретной) обработки информации. Логические преобразования двоичных символов включают три элементарных операции:

логическое сложение (дизъюнкция), или операцию ИЛИ, обозначаемую знаками «+» или «V» :

F=x1+x2+ …+xn;

2) логическое умножение (конъюнкция),

или операция И, обозначаемую знаком

«•», « »

или написанием переменных рядом без

знаков разделения:

»

или написанием переменных рядом без

знаков разделения:

F=x1x2x3…xn;

3) логическое отрицание (инверсия), или операция НЕ, обозначающую чертой над переменной:

.

.

Самостоятельное значение имеет

логическая операция ЗАПРЕТ, которая

символически записывается в виде

.

.

Рисунок 14.23 - Условное обозначение логических элементов в схемах

Совокупность элементов ИЛИ, И, НЕ представляет собой функционально полную систему: используя эти логические элементы можно составить любую логическую функцию.

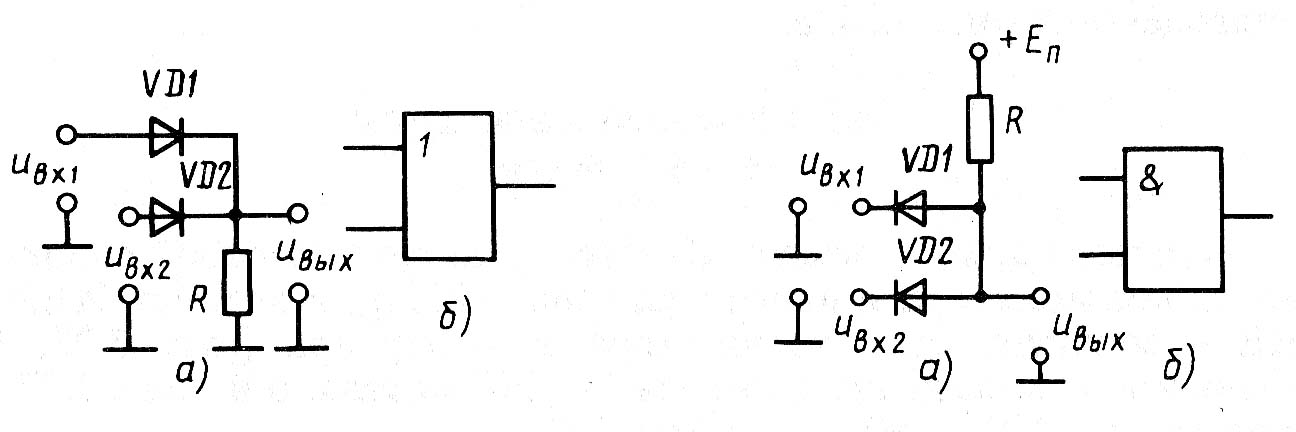

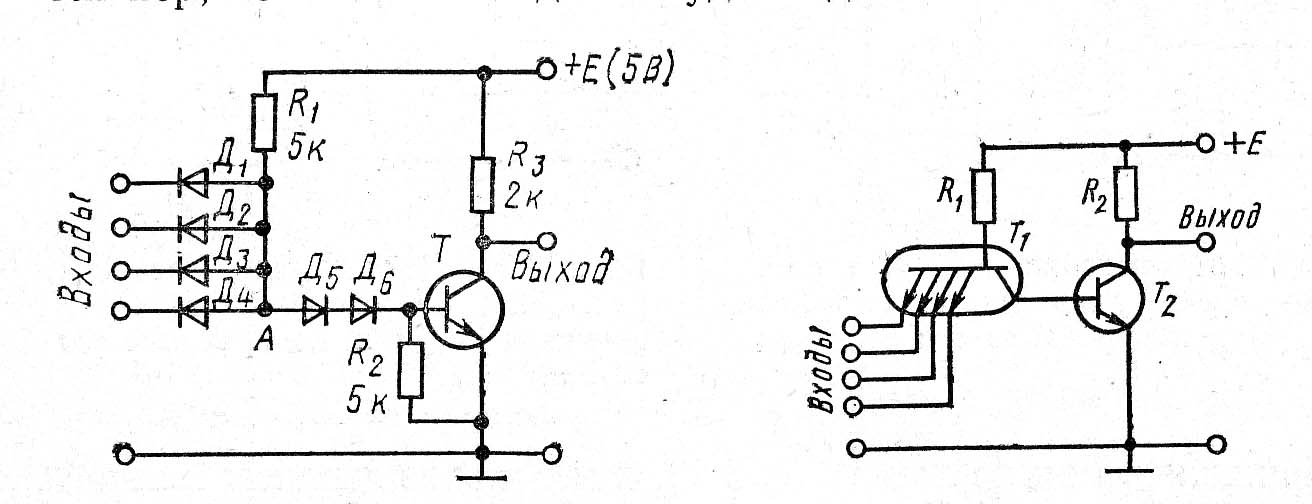

Логические элементы выполняются в виде ИМС на базе диодных элементов, транзисторных элементов, с использованием ДТЛ - элементов (диодно-транзисторная логика); ТТЛ - элементов (транзисторно-транзисторная логика); ЭСЛ – элементов (эмиттерно-связанная логика); КМОПЛ (КМДПЛ) – элементов (комплементарно-транзисторная логика). Для большинства микросхем элементы И – НЕ (ИЛИ – НЕ) являются базовыми. Рассмотрим принципиальные схемы базовых элементов различной логики.

Рисунок 14.24 - Схема (а) диодного элемента Рисунок 14.25 - Схема (а) диодного

«ИЛИ» и его условное обозначение (б) элемента «И» и его условное обозначение (б)

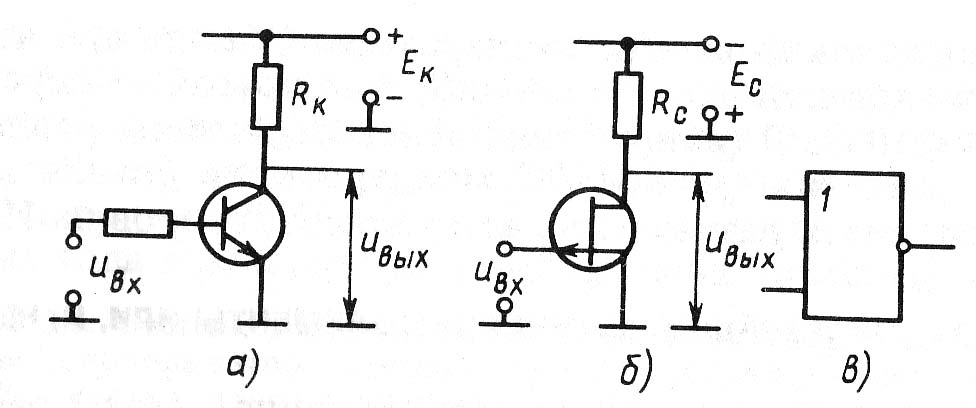

Рисунок 14.26 - Схема (а,б) транзисторного элемента «НЕ» и его условное обозначение

(в)

а) б)

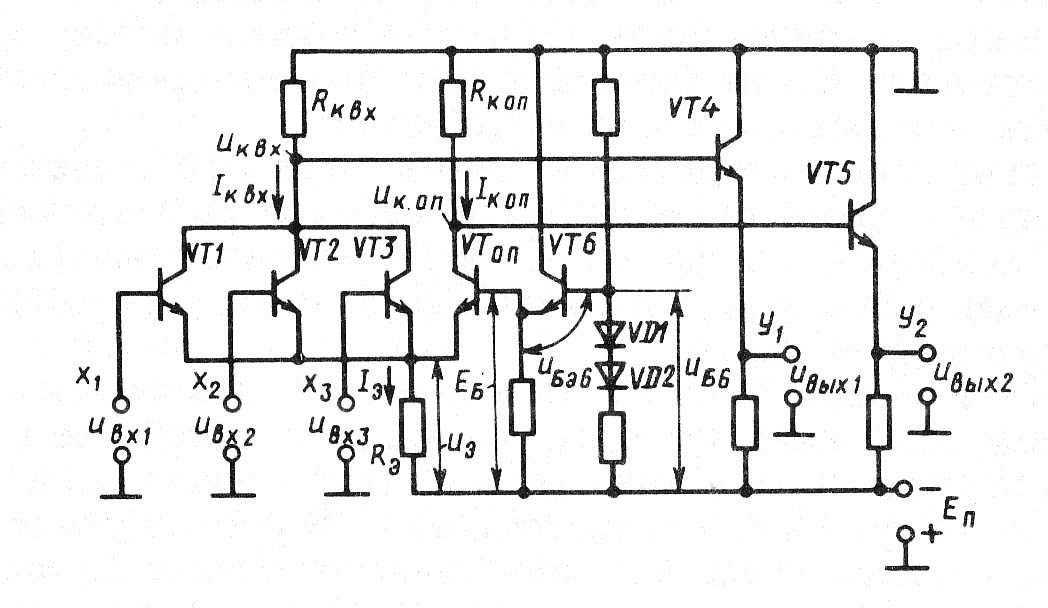

Рисунок 14.27 - Схема ДТЛ – элемента (а) и схема ТТЛ – элемента (б) «И – НЕ»

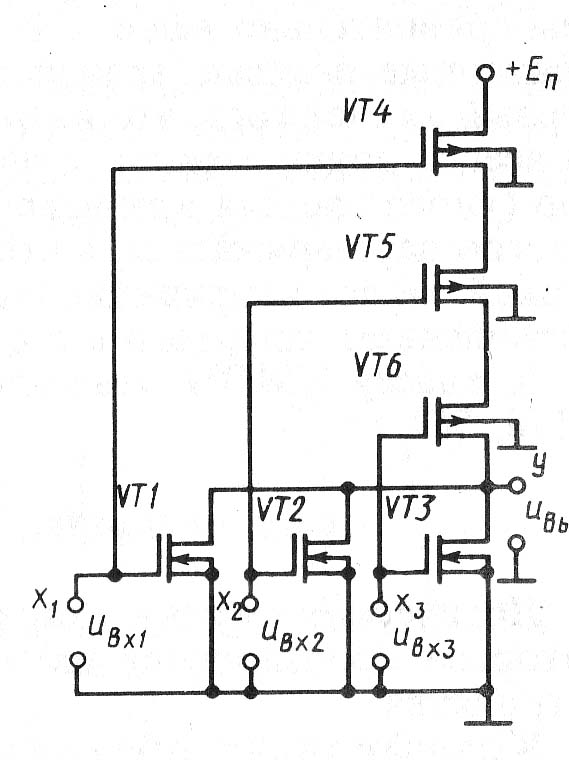

Рисунок 14.28 - Схема базового ЭСЛ – элемента «ИЛИ – НЕ»

Рисунок 14.29 - Схема базового КМОПЛ – элемента «ИЛИ – НЕ»

14.4 Триггеры

Триггером называют устройство, обладающее двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала. Применение триггера связано со следующими отличительными свойствами этого устройства:

- в интервале между переключающими сигналами состояние триггера не меняется, т.е. триггер можно использовать как элемент памяти;

- при переключении триггера потенциалы на его выходе меняются лавинообразно, образуя импульс с крутыми фронтами, что позволяет формировать прямоугольный импульс из напряжения другой формы;

- при поступлении каждой пары переключающих импульсов на выходе триггера формируется один импульс, что позволяет использовать триггер как делитель частоты на два.

Для перехода триггера из одного устойчивого положения в другое необходимо, чтобы входной сигнал превысил пороговое значение. Триггеры выполняются на транзисторах и в виде ИМС на основе логических элементов. Триггеры квалифицируют по функциональному признаку и по способу управления. По функциональному признаку различают триггеры RS, D, T, JK и других типов; по способу управления – асинхронные и синхронные (тактируемые), статические, реагирующие на изменение амплитуды входного сигнала, и динамические, реагирующие на перенос сигнала (с «1» в «0» или наоборот).

Физические процессы более просто рассмотреть при изучении транзисторных триггеров, к которым относят симметричные триггеры с внешним и автоматическим смещением и несимметричный триггер.

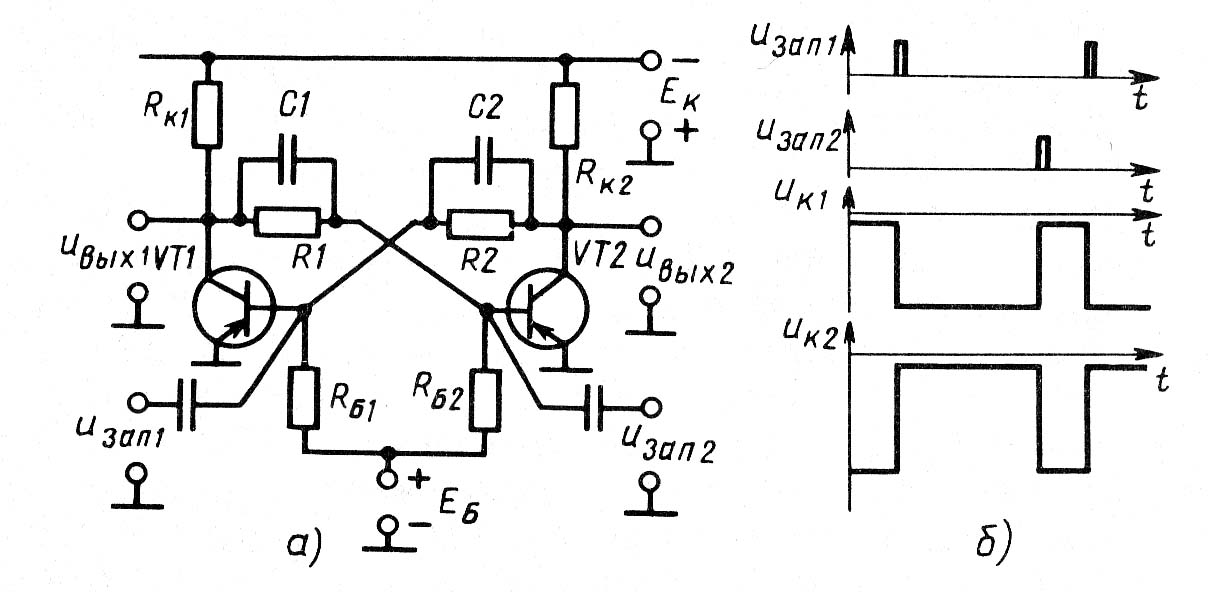

Рисунок 14.30 - Схема симметричного триггера с внешним смещением (а) и

динамическая диаграмма его работы (б)

Схема работает следующим образом: если транзистор VT1 закрыт (находится в состоянии насыщения), то при подаче на его базу отрицательного управляющего сигнала он начинает открываться; в этом случае на базу транзистора VT2 начинает поступать положительный сигнал через R1 – RБ2 и он начинает закрываться. Процесс заканчивается, когда VT1 открыт, а VT2 закрыт.

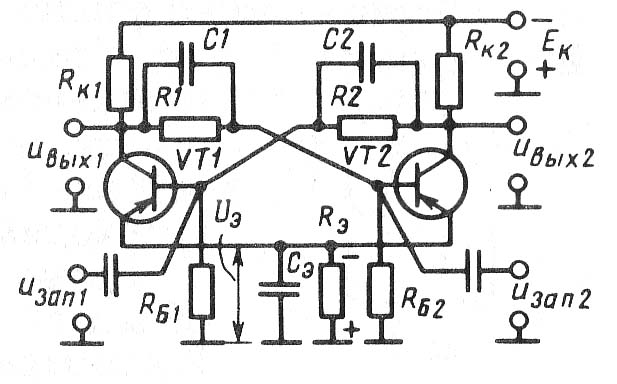

Напряжение, запирающее транзистор, можно получить не от специального источника, а от резистора Rэ в общей эмиттерной цепи (рисунок 14.31). Ток открытого транзистора создаёт на этом резисторе напряжение, которое через резистор RБ прикладывается между базой и эмиттером другого транзистора, запирая его. Чтобы устранить отрицательную обратную связь во время формирования фронтов импульсов, резистор Rэ шунтируют конденсатором Сэ.

Рисунок 14.31 - Схема симметричного триггера с автоматическим смещением

Благодаря лавинообразному формированию фронтов импульсов триггер обеспечивает лучшую форму импульсов при синусоидальном напряжении на входе и его можно использовать вместо формирователей импульсов и ограничителей амплитуды. Для этого применяют несимметричный триггер с эмиттерной связью (триггер Шмитта).

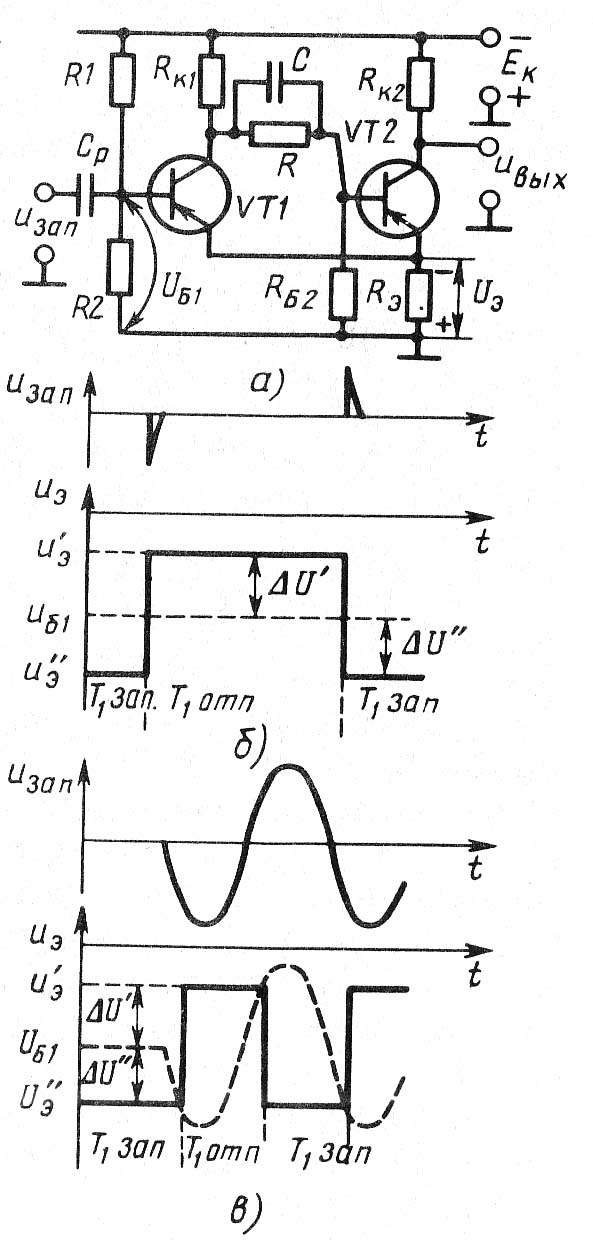

Рисунок 14.32 - Схема несимметричного триггера (а) и динамические диаграммы его

состояния (б) и формирования прямоугольных импульсов (в)

Здесь разность напряжения с левого плеча на правое передаётся через делитель R – RБ2, а с правого на левое плечо передаётся через общий резистор Rэ в общей эмиттерной цепи. Шунтировать этот резистор конденсатором не следует, так как напряжение на Rэ не сможет быстро изменяться. Конденсатор С является ускоряющим, делитель R1 – R2 обеспечивает необходимый режим работы транзистора VT1.

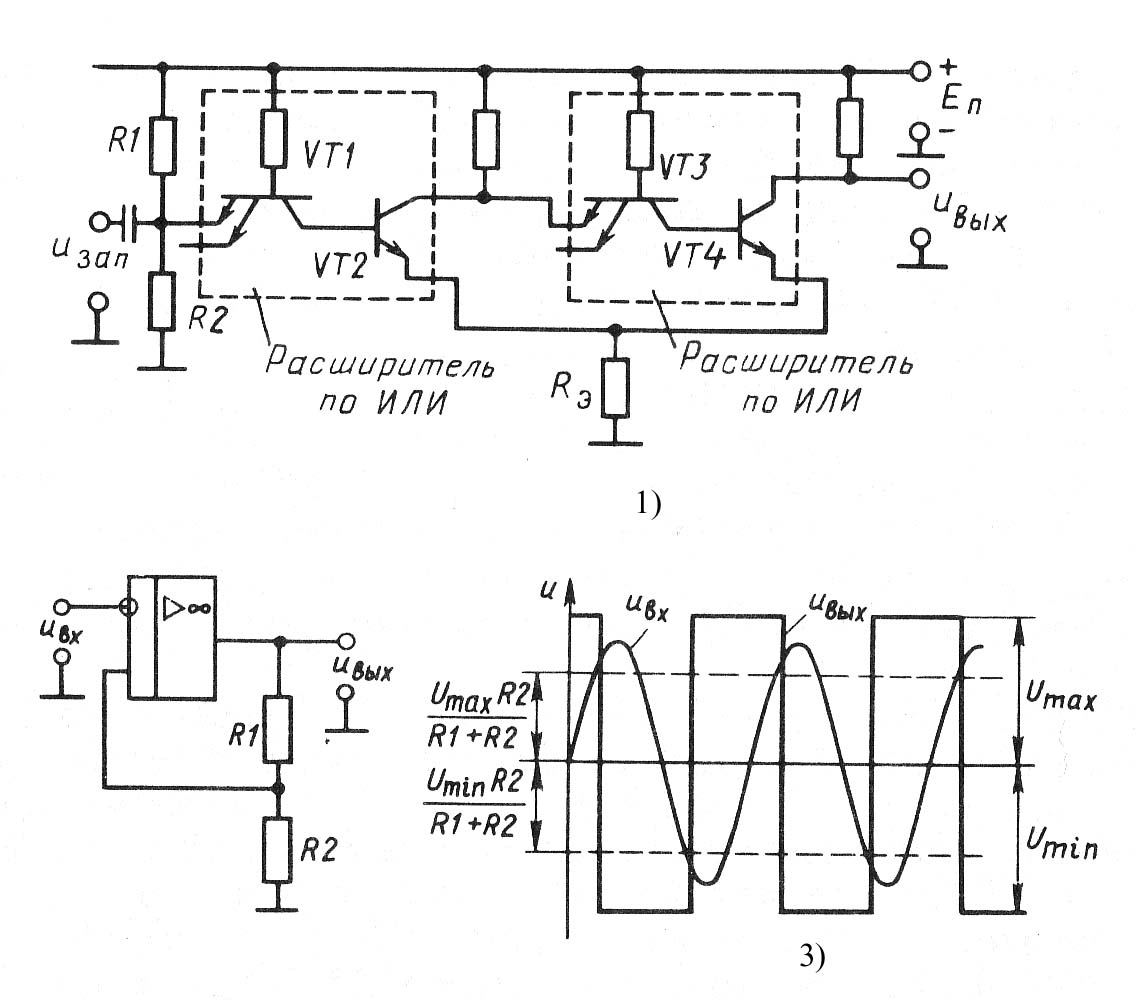

Интегральные триггеры Шмитта повторяют принципиальные особенности этих триггеров на дискретных элементах: одна связь плеч схемы является «коллекторно-базовой», а другая – «эмиттерной». Ниже приведена схема триггера Шмитта на расширителях по ИЛИ для базовых ТТЛ - элементов. Расширители являются плечами схемы. Коллектор транзистора VT2 связан с базой транзистора VT4 через транзистор VT3, эмиттерная связь осуществляется через резистор Rэ. Подбором резисторов R1, R2 можно настраивать пороги срабатывания триггера.

2)

Рисунок 14.33 - Схема триггера Шмитта на базовых ТТЛ – элементах (1),

на операционном усилителе с положительной обратной связью (2) и

статическая диаграмма его работы (3)

Если Uвх.

является отрицательным, а по абсолютному

значению превосходит напряжение на не

инвертирующем входе

,

то напряжение Uвых. =

Umax

(рисунок 14.33, 3) положительно. Изменение

Uвх. не влияет на

состояние выхода до тех пор, пока оно

не станет больше

,

то напряжение Uвых. =

Umax

(рисунок 14.33, 3) положительно. Изменение

Uвх. не влияет на

состояние выхода до тех пор, пока оно

не станет больше

.

При этом выходное напряжение изменяет

свой знак и принимает значение Uвых.

= Umin.,

которое сохраняется до тех пор, пока

Uвх. не окажется

отрицательным, а по абсолютному значению

больше

.

При этом выходное напряжение изменяет

свой знак и принимает значение Uвых.

= Umin.,

которое сохраняется до тех пор, пока

Uвх. не окажется

отрицательным, а по абсолютному значению

больше

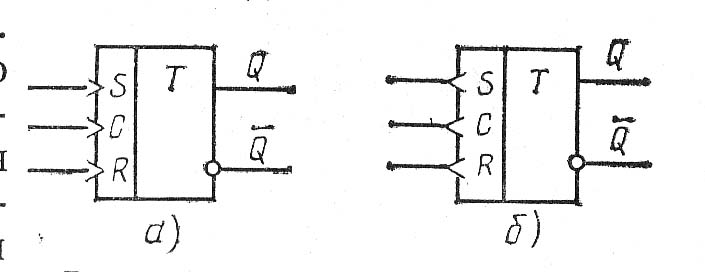

Триггер имеет два выхода. Потенциалы

на них взаимно инвертированы: высокий

потенциал на одном выходе соответствует

низкому потенциалу на другом выходе.

Один из выходов называют прямым (его

обычно обозначают Q

или Р); другой – инверсным (обозначают

).

).

О состоянии триггера судят по состоянию его прямого выхода. Если на нём установился потенциал, который кодируется логической единицей, то говорят, что триггер находится в состоянии «единица» и обозначают это как Q=1. Вход, по которому запускающий импульс переключает триггер в состояние Q=1, называют входом установки триггера в единицу и обозначают S. Другой вход называют входом установки триггера в нуль (вход сброса) и обозначают R. Входы S и R называют информационными. Таким образом, триггеры изображённые на рисунках 14.30 и 14.31 называют триггерами с установочными входами или RS – триггерами.

В рассмотренных триггерах сигналы на входах S и R продолжают воздействовать на его элементы и после переключения: такие входы называют статическими. Существуют также триггеры с динамическими входами, которые реагируют на перепады уровней сигналов: с 0 на 1 или с 1 в нуль.

В современной электронике триггеры выполняют в виде интегральных микросхем, построенных на основе логических элементов. Интегральные триггеры есть асинхронные (не тактируемые) и синхронные (тактируемые). Выше рассмотрены именно не тактируемые триггеры. Синхронный триггер, кроме информационных входов, имеет синхронизирующий (тактируемый) вход. Сигналы на информационных входах воздействуют на триггер только при появлении синхронизирующего импульса.

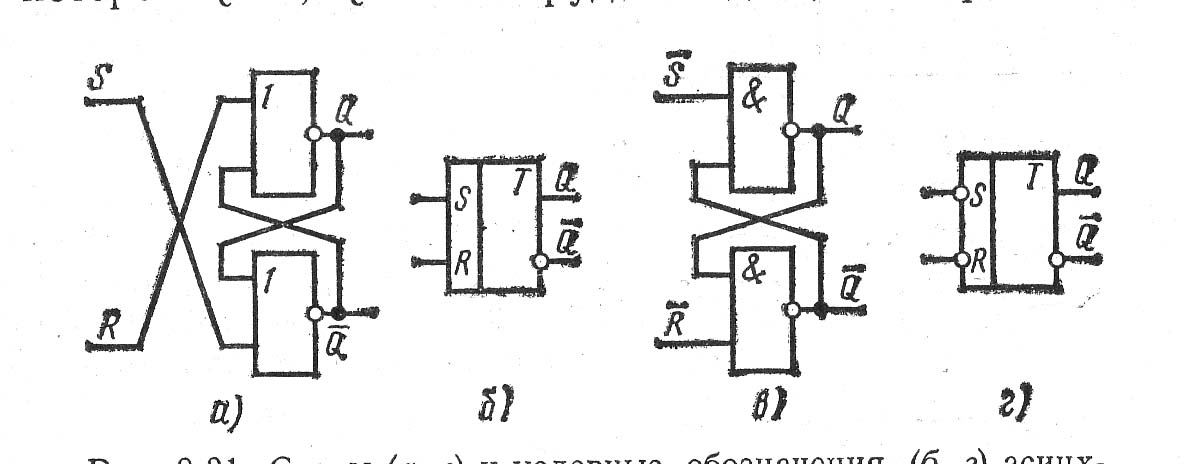

Схема и условное обозначение асинхронного RS – триггера таково:

Рисунок 14.34 - Схемы (а,в) и условное обозначение (б,г) асинхронных

RS – триггеров на элементах «ИЛИ-НЕ», «И-НЕ»

Комбинация состояний S=1, R=1 является недопустимой для триггера на логических элементах «ИЛИ-НЕ» , так как оба выхода должны установиться в «1». Триггер на логических элементах «И-НЕ» имеет недопустимую комбинацию S=0, R=0.

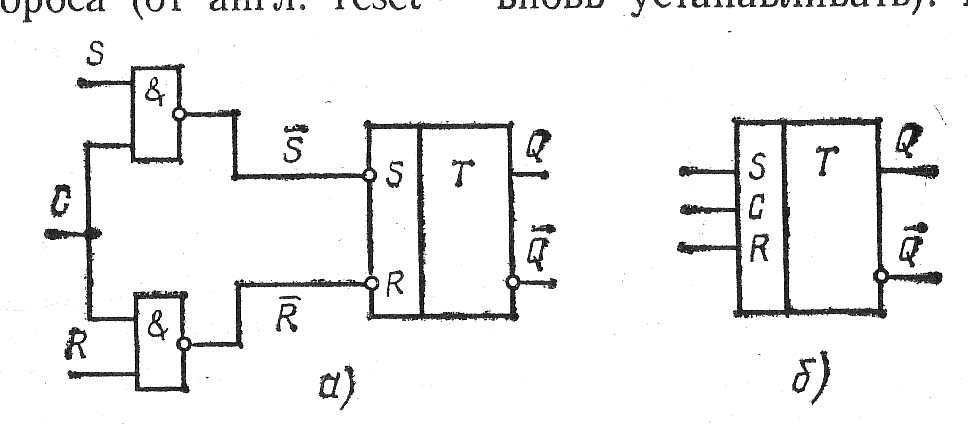

Схема и условное обозначение синхронного RS – триггера:

Рисунок 14.35 - Схема (а) и условное обозначение (б) синхронного

RS – триггера на элементах «И – НЕ»

Здесь управляющие сигналы проходят на входы S и R только при воздействии на синхронизирующий вход сигнала С=1.

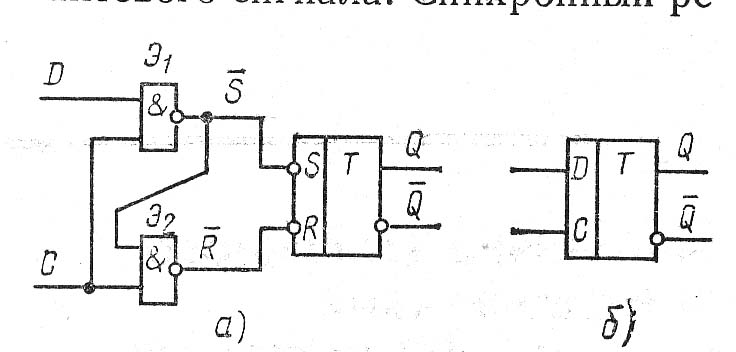

Для приема информации по одному входу используются D – триггеры (задержка). На рисунке ниже приведена схема и условное обозначение D- триггера на элементах «И-НЕ».

Рисунок 14.36 - Схема (а) и условное обозначение (б) D – триггера

на элементах «И-НЕ»

Логика работы D – триггера

такова:

.

В состоянии «1» D – триггер

остаётся до возвращения D

= 0. Таким образом, D –

триггер «задерживает» поступившую на

его вход информацию на время равное

периоду поступления импульсов на D

- вход.

.

В состоянии «1» D – триггер

остаётся до возвращения D

= 0. Таким образом, D –

триггер «задерживает» поступившую на

его вход информацию на время равное

периоду поступления импульсов на D

- вход.

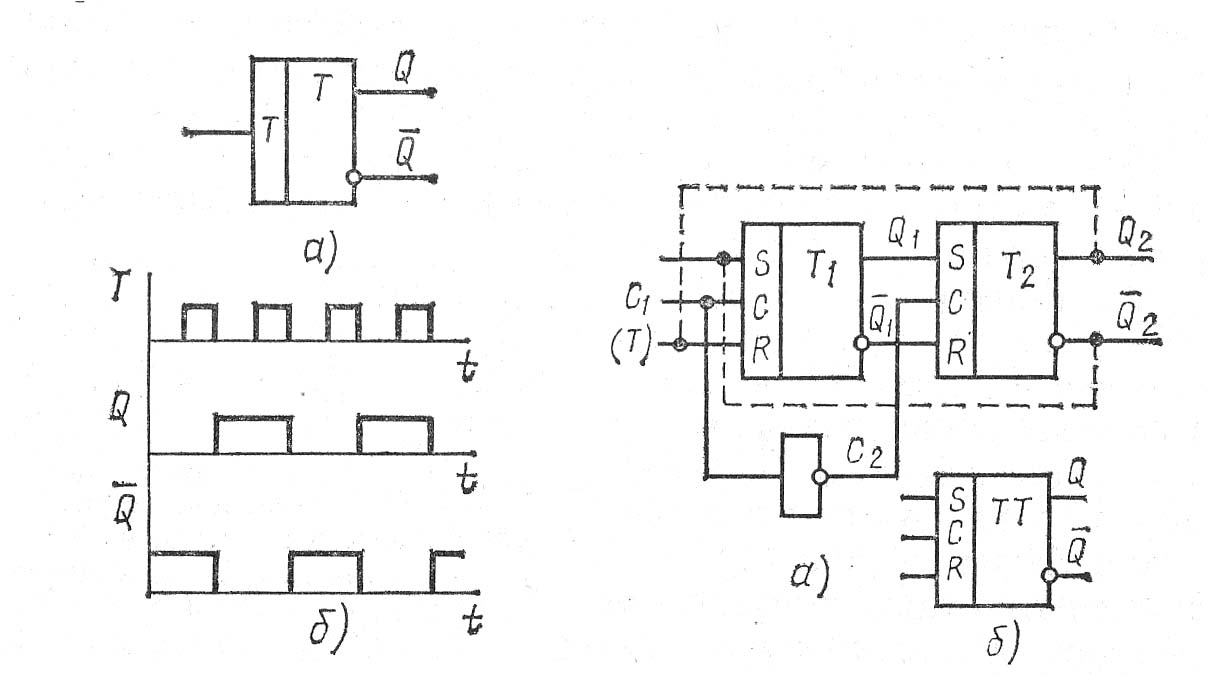

Т – триггер (tumdle – опрокидываться), или счетный триггер, имеет один информационный вход и переходит в противоположное состояние в результате воздействия на его вход каждого очередного сигнала. Название «счетный» связано с широким применением Т – триггеров в счётчиках импульсов.

Т – триггеры выполняют на основе двух последовательно соединенных RSС – триггеров, первый из которых называют ведущим, а другой – ведомым:

Рисунок 14.37 - Условное обозначение (а) Рисунок 14.38 - Схема (а) и условное

и динамическая диаграмма (б) обозначение двухступенчатого Т - триггера

одноступенчатого Т – триггера на базе RSC – триггеров

При поступлении сигналов на

информационные входы R и

S триггера Т1 он

принимает соответствующее состояние

«0» и «1» в момент, когда С1 = 1.

Сигналы с выходов Q1

,

ведущего триггера не проходят в ведомый,

так как С2 = 0. Информация пройдёт

в ведомый триггер только по окончании

синхронизирующего импульса при С1

= 0, С2 =1 и будет отображена на

выходах Q2 ,

ведущего триггера не проходят в ведомый,

так как С2 = 0. Информация пройдёт

в ведомый триггер только по окончании

синхронизирующего импульса при С1

= 0, С2 =1 и будет отображена на

выходах Q2 ,

.

.

Для получения двухступенчатого

Т – триггера вводят положительные

обратные связи, которые показаны

пунктиром, и используют вход С1

как информационный (Т). В этом случае

при Т=1 триггер Т1 устанавливается

в состояние противоположное состоянию

триггера Т2, а при Т=0 триггер Т2

переходит в состояние совпадающее с

состоянием триггера Т1. Таким

образом, на выходах

сигнал изменяется на противоположный

по окончании каждого очередного импульса

Т, что соответствует диаграмме рисунока

14.37, б.

сигнал изменяется на противоположный

по окончании каждого очередного импульса

Т, что соответствует диаграмме рисунока

14.37, б.

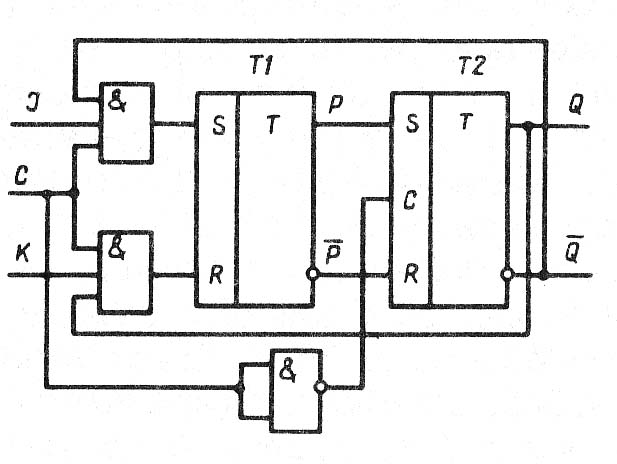

Универсальный триггер, или JK – триггер, имеет информационные входы J и K и синхронизирующий вход С. J-K триггер получают из двухступенчатого Т – триггера путем использования элементов «И–НЕ» на три входа во входных цепях ведущего триггера.

Рисунок 14.39 - Схема JK – триггера, использующая «И-НЕ» - элементы

на три входа: вход С является динамическим

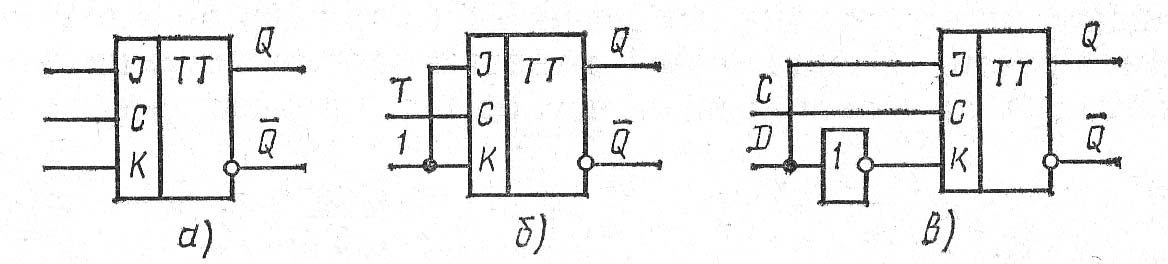

При J=K=1 JK - триггер изменяет свое состояние на противоположное в момент окончания каждого синхронизирующего импульса С. Используя вход J как вход S, а K – как R, реализуют синхронный RS – триггер, который при S=R=1 (что запрещено для обычного RS – триггера) переключается на каждый синхронизирующий сигнал. Таким образом, получают Т – триггер из JK - триггера. Добавлением инвертора на входе JK – триггера получают D – триггер.

Рисунок 14.40 - Условное изображение JK – триггера (а), схемы Т – триггера

и D – триггера на его основе

Все типы триггеров, реализуемые на основе JK – триггера, дают задержку в появлении выходных сигналов, равную длительности синхронизирующего сигнала.

Рассмотренные триггеры относят к статическим триггерам, реагирующим на уровни входных сигналов. Есть также динамические триггеры, которые реагируют на перепады уровней сигналов. Их условное изображение приведено ниже.

Рисунок 14.41 - Условное обозначение динамических синхронных

RS – триггеров с прямыми (а) и инверсными (б) входами

Динамические входы иногда обозначают короткой наклонной чертой на входе триггера.