- •Центральный процессор

- •1. Повышение производительности процессоров

- •2.1. Технологии многопоточности

- •2.2. Технология Hyper-Threading

- •2.3. Многоядерность

- •2.4. Технология виртуализации Hypervisor

- •2.5. Технология удаленного управления компьютерами сети

- •2.6. Технология ускорения процесса ввода-вывода данных – Acceleration Technology

- •3. Многоядерные процессоры корпорации Intel

- •3.1. Архитектурные особенности процессора Pentium d

- •3.2. Судьба системной шины

- •3.3. Производительность

- •3.4. Многоядерное будущее

- •5. Многоядерные процессоры компании ibm

- •5.1. Двухъядерный (dual-core) процессор Power 4

- •5.2. Следующий шаг - Power 5

- •5.5. Процессорный элемент Cell -"суперкомпьютер-на-кристалле"

- •7. Заключение

- •8. Планы Intel на 2009/2010 гг по выпуску процессоров

- •9. Тенденции развития средств вычислительной техники

- •1. Повышение тактовой частоты.

- •2. Увеличение объема и пропускной способности подсистемы памяти.

- •4. Системы на одном кристалле и новые технологии.

5.2. Следующий шаг - Power 5

Архитектураследующегопредставителя этой линейки -процессораPower 5,построенанапринципах,примененных вPower 4. Двапроцессорных ядрана одномкристалле имеют раздельный кэш L1 для данных и инструкций и общий кэш L2. Кешпамять второго уровня выполнена в виде трех отдельных блоков, у каждого из которыхесть свой контроллер. Ядра могут обращаться независимо друг от друга к любому из трех контроллеров.

Ряд важных нововведений начинается с того, что хотя кэш L3 и располагается вне кристалла, он напрямую связан с кэш уровня L2, что снижает задержки при работе скэш -памятью иулучшаетмасштабируемость. Системана базеPower 5может включать до 64процессорных конфигураций. Вмикропроцессоре Power 5 IBM впервые реализовала технологию микроразделов (Micro-Partitioning), позволившую представитькаждый физическийпроцессоркакнесколько (до 10) логических. Micro-Partitioning такжепредусматриваетединуюконсоль дляуправлениясистемами любыхтипов и широкийнаборсистемныхсервисов дляуправления рабочиминагрузками иперераспределения ресурсов,что дает возможность выполнить больший объем работы.

Разработчикиинтегрировали вкристаллпроцессораPower 5не только двапроцессорных ядра,но и элементыуправленияпамятью и заданиями, ранее реализовавшиеся на внешних элементах. Встроенный в процессор контроллер памятииспользуется и в технологиях, представленных AMD (Athlon 64 и Opteron). Недостаток такой системы — необходимость заменять процессор для перехода на системную плату с новым типом памяти.

Многопоточность в Power 4 реализуется на аппаратном уровне: каждое из двух ядер выполняет свой поток команд, при задержке выполнения одного потока ресурсы обслуживающегоего ядранельзяпередать другомупотоку. ВPower 5 этазадача решена с помощьюмногопоточной технологии (SMT).

ОдновременнаямногопоточностьSMT,прикоторойпроцессорное ядроможетзапрограммировать порядок параллельного выполнения команд из нескольких потоков, впервые появилась только в Power 5. Как известно, технология SMT позволяет системе динамическиподстраиваться -если возникает длительнаязадержкапри выполнениикоманды одногопотока (треда), то все исполнительные блоки временнопередаются другому потоку. ТеоретическиSMT можнореализоватьне только для двух,но и для большегочислапотоков, однако, этослишкомусложнитмеханизммногопоточности,но не даст серьезного выигрыша в производительности.

В Power 5каждоепроцессорное ядроможет одновременно обрабатывать двапотокакоманд, т.е.работаеткак два логическихпроцессора, асамкристалл -какчетыре логических процессора. Команды обоих потоков извлекаютсяиз одной и той жекэш-памяти команд 1-го уровня и вместе загружаются в исполнительные блоки. Теоретически обапотокакомандпослесчитыванияизкэш-памятикоманд должныпроходить через конвейер и использовать ресурсы физического процессора безконфликтовмеждупотоками. В этомслучаеприменениеSMTудваиваетпроизводительность процессора. Однако если между потоками возникнет конфликт из-за ресурсовпроцессора, то одномуизнихпридется ждать, иприростпроизводительности оказываетсяменьше 100%.

SMT организует выполнение команд из потоков следующим образом. Несколькокомандизкаждогопотокаможнозагрузить внаборконвейеров в течениекаждого такта, причем любые пять команд из обоих потоков, представляющие до двух операцийзагрузки и сохранения, двух операций двоичной арифметики, двух операций сплавающей точкой и ветвление, допустимо загрузить в один конвейер в течение одного такта. За один такт по стадиям конвейера проходит только одна команда из одного изпотоков. Физическийпроцессор определяетпорядок выполнениякомандна основенабора правил с учетом зависимости операндов,времени ожиданияобработки команд инеобходимости внеочередного выполнения некоторых команд.

Каждый физическийпроцессорсодержиткэш-память данных икоманд1-гоуровня,которыесовместноиспользуютсяобоими логическимипроцессорами. Как говорилось выше,кэш-память2-гоуровня у физическихпроцессоров (ядер)Power 5 общая, поэтому онасовместно используется четырьмя потоками команд. Дляулучшения производительности SMT при выполнении различных приложений вPOWER5 реализованы динамическаябалансировка ресурсов иподстраиваемыйприоритетпотоков.

Распределениеприоритетов выполнения вычислительныхпотоковпроисходитна аппаратном уровне. Микропроцессор поддерживает восемь уровней приоритета (отседьмого,соответствующегонаивысшему приоритету потока, донулевого). Потоку сболее высоким приоритетом предоставляется большая часть ресурсов. Когда приложению требуетсяиспользовать всюполосу пропускания дляобмена данными спамятью,процессоравтоматически переходит в однопоточный режим.

Очевидно,чтоприменениеSMTпозволяеткаждому ядру выполнять большекомандза такт, вследствие чего увеличивается и энергопотребление.

Решение этой проблемы обеспечивают два механизма:

при низкомприоритете обоихпотоков (0или 1) включается встроенная технология энергосбережения;

возможно временное отключение техкомпонентовпроцессора,которыене потребуются во времяследующих тактов.

В результате,при одинаковыхзатратах энергии, Power 5выполняетна 50% больше инструкций,чем Power 4.

Технология сверхплотной компоновки, особенность которой заключается вприменении общей оперативной памяти и межузловых соединений с большойпропускной способностью, позволяет реализовать высокоскоростные соединениямежду восемью процессорами Power 5. Четыре кристалла Power 5 с четырьмякристалламикэш -памятиL3упаковываются вмногокристальныймодуль Multichip Module (MCM) размерами 95*95 мм. Так как Power 5 нацелен на работу с системамихранения данных нового поколения, то поддерживается адресация хранилища данныхемкостью до 96 Пентабайт! Отметим также, что Power 5 обратно совместим с Power 4на уровне программного обеспечения.

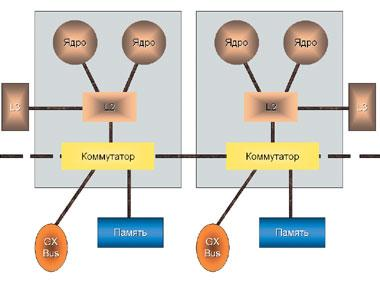

5.3. Power 5+

Следующим шагом для IBM стал Power 5+ (рис. 8), представляющий собой такназываемый"сервер-на-кристалле". Онсодержит двапроцессора,поддерживающихSMT-технологию, высокопроизводительный системный коммутатор, встроенную кэш-память объемом до 72 Мбайт,интерфейс ввода-вывода. Пиковаяпропускнаяспособность шины процессор—память составляет 42,6 Гбайт/с. Серверы, оснащенныемикропроцессорамиPower 5+,сконструированы сучетом требований к вычислительным системам малого и среднего бизнеса, они учитывают ограниченностьресурсов, характерную для многих таких компаний.

Рис.8.Схема процессора Power 5+

У нихестьудобныйпрограммныйинструментарий, и они обладают возможностью"внутреннегомасштабирования"засчет реализации технологий виртуализации Micro-Partitioning. Использование логических разделовпозволяетсоздавать ИТ-системы уменьшенных размеров иповышенной производительности.

5.4. Power PC 970MP

Технология Power была положена и в основу процессоров Power PC. Последнийпродукт этойсерии,PowerPC 970MP,представляетсобойпервую двуядерную 64- битовую версию Power PC, созданную на базе архитектуры Power 4 с использованием

90-нм технологии. Между 64- и 32-битовыми конфигурациями возможно динамическоепереключение. Эффективность работы поддерживается механизмом SMP-оптимизации.Каждое ядро вPowerPC 970MP обладаетсобственнойкэш-памятьюL2, а такженезависимым термодиодом и шинойпитания. Посравнению спредыдущимимодификациями унегоувеличенапропускнаяспособностьпроцессорной шины и размер кэш- памяти уровня L2. Раздельныйкэш L2 позволяет отключать илипереводить в спящий режим одно из ядер. За такт может быть выполнено до восьми инструкций. Для сравнения: процессоры AMD на базе архитектуры К8 выполняют не больше шести инструкций за такт. Тактовые частоты ядер регулируются синхронно.

На игровыхприставках Xbox 360 вместопроцессораIntel,установленного впервой приставке Xbox, теперь применяется кристалл на базе PowerPC, который IBMназвала "компьютер-на-кристалле" (SoСили System-on-Chip).

На одной подложке интегрированы три идентичных ядра, объединенных диспетчерской шиной XBAR,причемкаждоеиз ядерспособно выполнятьпо дванезависимыхпотокакоманд. Этотпроцессор,созданныйспециально дляигровых имультимедийныхприложений, эффективен и для обработки больших объемовпотоковых данных. В процессоре реализована также возможность обхода кэш-памяти второго уровняL2 с пересылкой до восьми пакетов данных предварительной выборкинепосредственно вкэшL1каждогоиз трех ядерпроцессора. При этомчастикэшпамяти L2 могут быть распределены в качестве буферов для потоковых данных. Xbox 360сталапервойприставкой спроцессоромседьмогопоколения,появившейсяна рынке.