Лабораторные работы / lab 2 / 18 / Отчет

.docПроектирование и исследование триггеров.

Цель работы: Изучение функционирования и схемных разновидностей триггеров, овладение методами их проектирования, приобретение навыков в отладке и определении характеристик триггеров.

Задание:

-

Вариант №18

0

0

0

1

1

1

0

0

1

1

0

Ход работы:

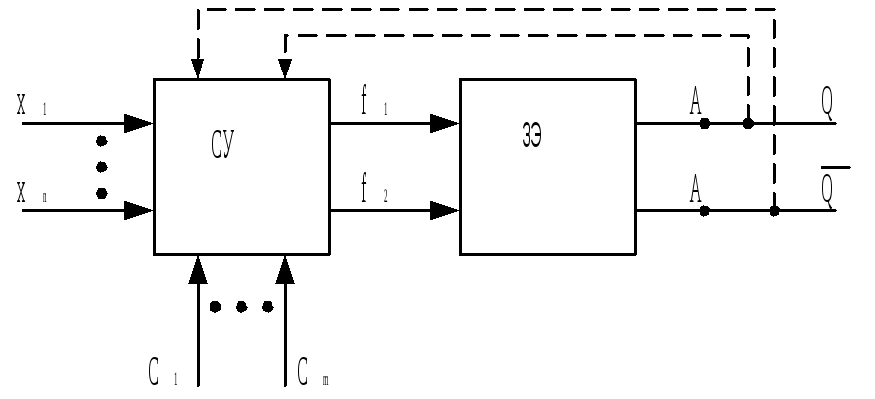

В

схемах цифровой вычислительной техники

в

качестве запоминающих элементов широко

используются триггеры. Триггер

представляет собой устройство с

двумя устойчивыми состояниями, содержащее

запоминающий элемент (ЗЭ) и схему

управления (СУ), как показано

на

рис. 1, где

![]() ,

… ,

,

… ,

![]() -

информационные

входы триггера;

-

информационные

входы триггера;

![]() ,

...,

,

...,

![]() - тактирующие входы;

- тактирующие входы;

![]() и

и

![]() - соответственно прямой и инверсный

выходы триггера;

- соответственно прямой и инверсный

выходы триггера;

![]() и

и

![]() - функции

возбуждения ЗЭ.

- функции

возбуждения ЗЭ.

Рисунок 1

Проектирование триггерных устройств состоит в выборе ЗЭ и синтезе СУ в заданном элементном базисе.

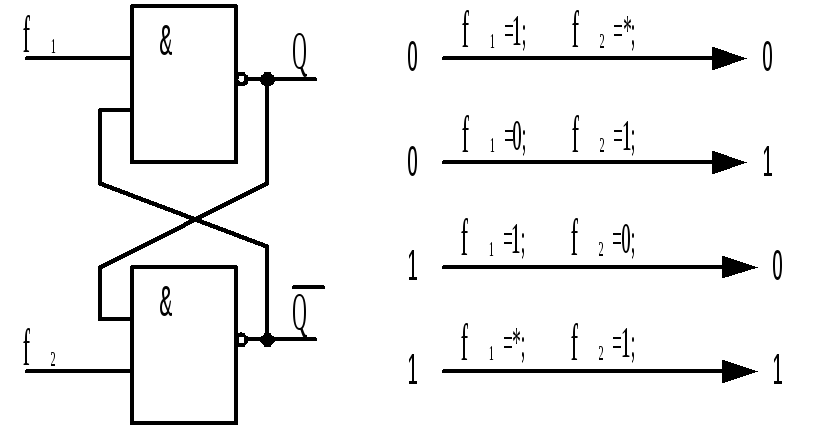

В триггерах, управляемых уровнем сигнала, используются элементарные запоминающие элементы на вентилях И-НЕ. Способ переключения описывается системами подграфов переходов.

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

1 |

* |

|

0 |

0 |

0 |

1 |

1 |

* |

1 |

|

0 |

0 |

1 |

0 |

0 |

1 |

* |

|

0 |

0 |

1 |

1 |

1 |

* |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

* |

|

0 |

1 |

0 |

1 |

1 |

* |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

* |

|

0 |

1 |

1 |

1 |

1 |

* |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

* |

1 |

|

1 |

1 |

0 |

0 |

0 |

1 |

* |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

* |

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

X1 C

Qs

|

1 |

1 |

0 |

1

X2 |

|

* |

1 |

* |

* |

|

* |

1 |

1 |

* |

|

1 |

1 |

0 |

1 |

|

* |

* |

* |

*

X1 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

1 |

* |

* |

Qs C X2![]()

![]()

![]()

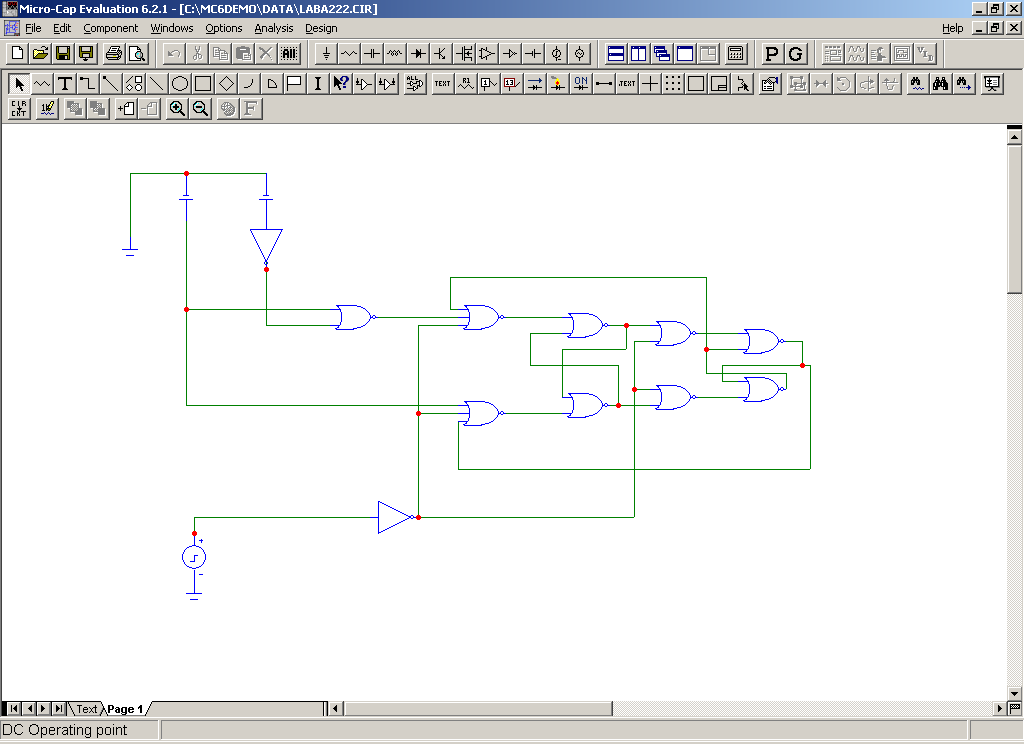

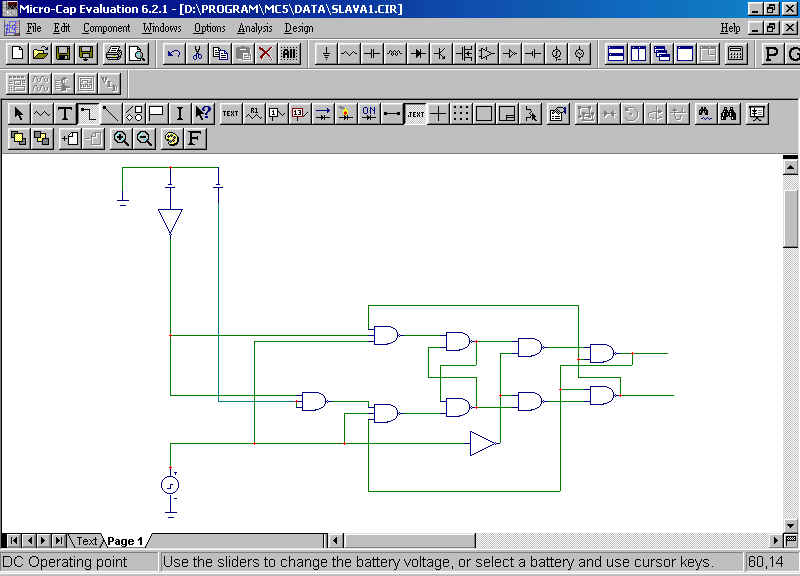

Схема выполненная в Micro-Cap 6.2.1

X1

X1

Qs

|

* |

* |

0 |

*

X2 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

* |

* |

0 |

* |

|

0 |

0 |

1 |

0

X2 |

|

* |

0 |

* |

* |

|

* |

0 |

0 |

* |

|

0 |

0 |

1 |

0 |

Qs![]()

C C

X1 X1

Qs

|

* |

* |

1 |

*

X2 |

|

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

* |

* |

1 |

* |

|

1 |

1 |

0 |

1

X2 |

|

* |

1 |

* |

* |

|

* |

1 |

1 |

* |

|

1 |

1 |

0 |

1 |

Qs![]()

C C

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Схема триггера на элементах ИЛИ-НЕ выполненная в Micro-Cap 6.2.1