- •Триггеры Общие сведения. Активные и пассивные логические уровни элементов и-не и или-не.

- •Назначение триггера.

- •Основные обозначения.

- •Типы триггеров.

- •Асинхронные триггеры.

- •Синхронные триггеры со статическим управлением.

- •Синхронные триггеры, построенные по принципу двухступенчатого запоминания информации.

- •Триггеры с динамическим управлением.

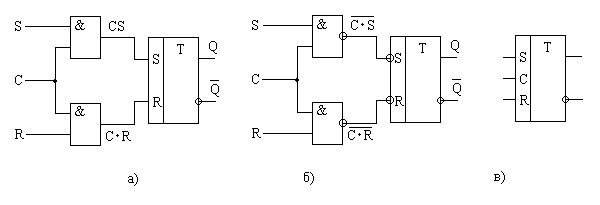

Синхронные триггеры со статическим управлением.

Рассмотрим триггеры, в которых действие управляющих сигналов на входе С проявляется в течение всего времени существования этих сигналов.

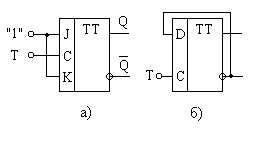

рис 4.3

RS-триггер.

На рис. 4.3,а,б показаны логические структуры синхронного RS-триггера. Как видно из представленных структур, синхронный RS-триггер состоит из асинхронного триггера с прямыми (либо инверсными) входами, на входах R и S которого включены логические элементы И (И-НЕ). С помощью логических элементов И (H-HE) обеспечивается передача активных уровней информационных входов S и R синхронного триггера на входы S и R входящего в его состав асинхронного триггера только при наличии уровня лог. 1 на синхронизирующем входе С.

Таким образом, при C = 0 на входы асинхронного триггера не передаются активные уровни и триггер сохраняет ранее установленное в нем состояние Q0. При C = l состояние триггера определяется действующими на входах уровнями так же, как и в рассмотренном выше асинхронном RS-триггере, Следовательно, функционирование синхронного RS-триггера может быть описано логическим выражением

|

(4.3) |

Нормальная работа синхронного RS-триггера требует, чтобы за время действия лог. 1 на синхронизирующем входе С уровни на информационных входах S и R оставались неизменными. Смена уровней на входах допускается лишь в то время, когда C = 0 и триггер не реагирует на уровни, действующие на входах S и R.

На рис. 3,в показано условное изображение синхронных RS-триггеров в схемах.

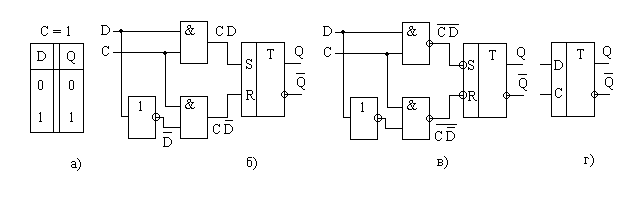

D-триггер.

Имеет лишь один информационный вход, называемый входом D, Вход С управляющий и служит для подачи синхронизирующего сигнала.

Функционирование D-триггера определяется таблицей состояний (рис. 4.4,а). Как видно из таблицы, при C = l триггер устанавливается в состояние, определяемое логическим уровнем на входе D (при C = 0 он сохраняет ранее установленное состояние Q0). Такое функционирование может быть описано логическим выражением

|

(4.4) |

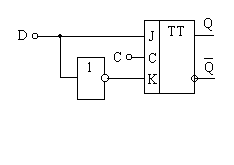

рис 4.4

На рис. 4.4,б представлены логические структуры D-триггера, состоящего из асинхронного RS-триггера с логическими элементами на входах. При C = 0 на выходах элементов И (И-HE) образуются пассивные для входов асинхронного RS-триггера уровни. При C = l уровень, поданный на информационный вход D, создает активный уровень либо на входе R (при D = 0) либо на входе S (при D = l) асинхронного RS-триггера, и триггер устанавливается в состояние, соответствующее логическому уровню на входе D). Таким образом, D-триггер воспринимает информацию со входа D при C = l и затем ее может хранить неопределенно длительное время, пока C = 0. На рис. 4,г показано символическое изображение D-триггера.

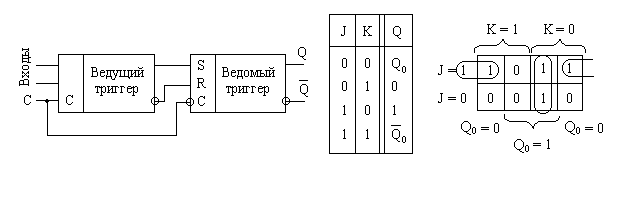

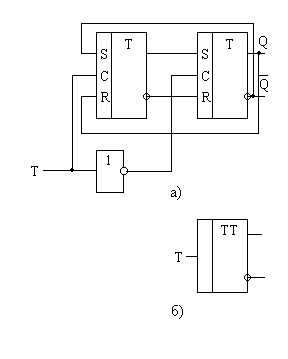

Синхронные триггеры, построенные по принципу двухступенчатого запоминания информации.

Особенность триггеров с двухступенчатым запоминанием информации состоит в том, что они содержат две триггерные структуры: одна из них образует так называемый ведущий триггер а другая - ведомый (рис. 4.5) . Оба триггера функционируют как синхронные триггеры со статическим управлением. При значении на синхронизирующем входе С = 1 ведущий триггер устанавливается в состояние, соответствующее сигналам, поступающим на информационные входы. Ведомый триггер, имеющий инверсный синхронизирующий вход при этом невосприимчив к информации, поступающей на его вход с выхода ведущего триггера. Он продолжает находиться в состоянии, в которое был ранее установлен (в предыдущем тактовом периоде).

|

|

рис 4.5 |

рис 4.6 |

При изменении значения С (с значения С = 1 на значение C = 0) ведущий триггер отключается от информационных входов и перестает реагировать на изменения значений сигналов на этих входах; ведомый триггер устанавливается в состояние, в котором находится ведущий триггер. С этого момента на выходах устанавливаются значения, соответствующие входным сигналам, поступавшим к моменту рассматриваемого фронта сигнала на синхронизирующем входе.

Таким образом, управление процессами в триггере с двухступенчатым запоминанием информации за время тактового периода осуществляется двумя фронтами сигнала на синхронизирующем входе: на положительном фронте происходят установка ведущего триггера, на отрицательном фронте - ведомого триггера. В качестве примера рассмотрим JK-триггep с двухступенчатым запоминанием информации.

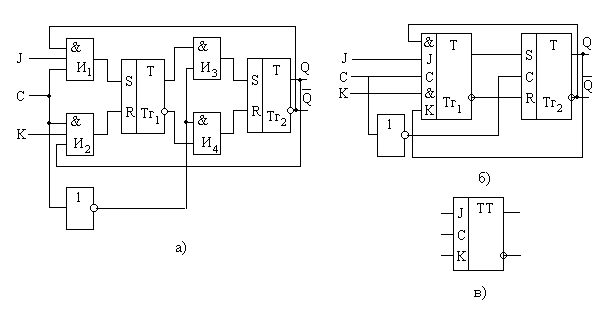

JK-триггер.

На рис. 4.6 таблица состояний JK-триггера представлена в форме диаграммы Вейча, из которой можно получить следующее логическое выражение, определяющее функционирование JK-триггера:

|

(4.5) |

Из (4.5) следует, что состояние Q, в которое устанавливается триггер, определяется не только уровнями на информационных входах J и K, но и состоянием Q0, в котором ранее находился триггер. Это определяет возможность построения логической структуры JK-триггера с использованием двух RS-триггеров. Один из RS-триггеров (ведомый) предназначен для хранения текущего состояния Q0; снимаемые с его выходов уровни Q0 и 0 совместно с информационными сигналами входов J и К используются для формирования нового состояния Q в другом RS-триггере (ведущем), JK-триггер с подобной логической структурой представлен на рис. 4.7,а. Так как каждый из триггеров совместно с элементами И на входах образует схему синхронного RS-триггера, то логическая структура может быть такой, как показано на рис. 4.7,б. Здесь ведущий триггер Тг1, имеет по две пары связанных операцией И входов J и К.

При уровне лог. 0 на входе С триггер Тг1, не реагирует на сигналы входов J и К. На синхронизирующий вход триггера Тг2 при этом подается уровень лог. 1, и состояние ведущего триггера Тг1 передается ведомому триггеру Тг2. Оба триггера оказываются в

рис 4.11

рис 4.10

рис

4.9

рис

4.9

рис4.8

рис 4.7

одном и том же состоянии. При переходе на входе С к уровню лог. 1 на синхронизирующий вход триггера Тг2 через инвертор подается уровень лог. 0 и логическая связь между триггерами обрывается. Триггер Тг1 устанавливается в состояние Q, определяемое выражением (4.5). Подача вновь на вход С уровня лог. 0 приводит к передаче состояния Q из триггера Тг1, в триггер Тг2. Символическое изображение описанного JK-триггера приведено на рис. 4.7,в.

На рис. 4.8 показано включение JK-триггера, при котором он выполняет функции D-триггера.

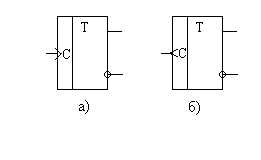

Т-триггер.

На рис. 4.9,а показана логическая структура Т-триггера. При поступлении на вход Т импульса на положительном его фронте ведущий триггер Тг1, устанавливается в состояние, противоположное состоянию ведомого триггера Тг2; на отрицательном фронте входного импульса происходит передача состояния триггера Тг1 в триггер Тг2.

На рис. 4.9,б приведено символическое изображение Т-триггера.

Режим Т-триггера может быть получен с помощью JK-триггера либо D-триггера, как показано на рис. 4.10,а,б.