Лабораторная работа 21 / Отчет по лабораторной 2

.docЦель работы: Описать на языке VHDL схему устройства, реализующего выполнение 3-х функций, описанных в таблице задания лабораторной 1.

Устройство состоит из следующих компонентов: дешифратор и 3 модуля 4-входовых элемента ИЛИ.

Структурная схема устройства:

Входной код подается в формате числа типа Integer. Дешифратор формирует на своих выходах значения, зависящие от входного кода и соответственно обеспечивают формирование логического сигнала на выходах элементов “ИЛИ” в соответствии с заданной функцией для каждого элемента. По таблице истинности заданных функций определяется разводка подключения элементов “ИЛИ” к выходам дешифратора.

В схеме данного устройства реализованы лог, функции соответствующие вариантам 4,5,6 в таблице заданий лаб. 1 . Ниже приведены их таблицы истинности.

|

Входной |

Числовой |

|

|||

|

код |

эквивалент |

Z1 |

Z2 |

Z3 |

|

|

000 |

0 |

1 |

0 |

0 |

|

|

001 |

1 |

0 |

1 |

0 |

|

|

010 |

2 |

0 |

0 |

1 |

|

|

011 |

3 |

1 |

0 |

1 |

|

|

100 |

4 |

1 |

1 |

1 |

|

|

101 |

5 |

1 |

1 |

0 |

|

|

110 |

6 |

0 |

0 |

1 |

|

|

111 |

7 |

0 |

1 |

0 |

|

Реализация на языке VHDL:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

ENTITY lab2 IS

port (input:integer range 0 to 7; --Описание внешних выводов

z1,z2,z3: out std_logic );

END lab2;

ARCHITECTURE structure OF lab2 IS

CONSTANT num_terms: integer :=8; --Разрядность выхода дешифратора

COMPONENT decod --Прототип компонента дешифратора

generic( num_outputs:integer; delay:time);

port(input:in integer range 0 to num_terms-1;

output: out std_logic_vector ( 0 to

num_terms-1));

end COMPONENT;

--Подключение компонента к программе

FOR ALL:decod USE ENTITY WORK.decod(behave);

COMPONENT OR4 --Прототип компонента “ИЛИ”

port (in1,in2,in3,in4 :in std_logic; hit:out std_logic);

end COMPONENT;

-- Подключение компонента к программе

FOR ALL:OR4 USE ENTITY WORK.OR4(behave);

--COMPONENT zero --Прототип компонента "zero"

--port (n: out std_logic); --В данном варианте не используется!!!

--end COMPONENT;

--Подключение компонента к программе

--FOR ALL:zero USE ENTITY WORK.zero(behave);

SIGNAL y : std_logic_vector(0 TO num_terms-1); --Вектор сигнал – выход

--дешифратора

--SIGNAL zero1:std_logic:='0'; --Сигнал для “zero”

BEGIN

u1: decod --Параллельный оператор дешифратора

generic map(num_terms, 5 ns)

port map(input, y);

u2:OR4 -- Параллельный оператор элемента ИЛИ 1

port map(y(0),y(3),y(4),y(5),z1);

u3:OR4 -- Параллельный оператор элемента ИЛИ 2

port map(y(4),y(5),y(1),y(7),z2);

u4:OR4 -- Параллельный оператор элемента ИЛИ 3

port map(y(2),y(3),y(4),y(6),z3);

--My_zero:zero --Параллельный оператор нуля

--port map(zero1);

END structure;

Примечание: В данном варианте реализаций функций компонент, обеспечивающий установку 0(zero) на входах элементов ИЛИ не используется по причине того , что все функции представляют из себя ДНФ с 4-мя конъюнкциями и ,следовательно, все входы их будут подключены к выходам дешифратора.

Текст программы теста:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE work.util_1164.all;

USE STD.textio.ALL;

ENTITY tb_lab2 IS

END tb_lab2;

ARCHITECTURE test OF tb_lab2 IS

component lab2 --Компонент lab2 включает в себя

--все вышеописанные архитектуры

port (input:integer range 0 to 7;

z1,z2,z3: out std_logic );

end component;

SIGNAL out1,out2,out3:std_logic; --Выходы значений функций z1,z2,z3

SIGNAL stim_integer: integer range 0 to 7; --Для отобр. входн. знач. на диагр.

for u1:lab2 use entity work.lab2(structure); --Подключение всех архитектур

--к тестовой программе

BEGIN

u1:lab2

port map(stim_integer, out1,out2,out3 );

stimulator:

PROCESS

variable i:integer range 0 to 7;

BEGIN

for i in 0 to 7 loop

stim_integer <=i;

Wait for 50 ns;

END LOOP;

assert false report "End of Simulation!"

severity note;

wait;

END PROCESS;

end test;

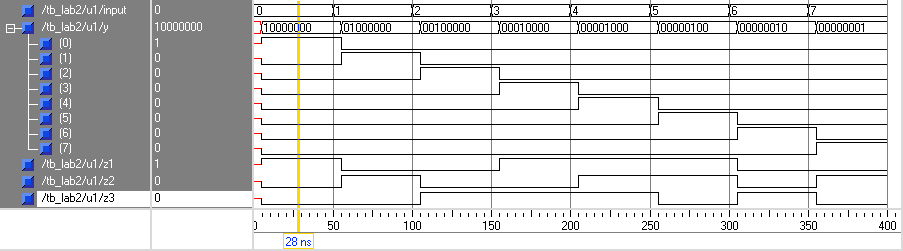

Результат работы программы:

Как видно из временной диаграммы работы устройства значения функций заданных в таблице истинности совпадают со значениями на выходах устройства, что свидетельствует о правильности синтеза.

В приложении представлен результат синтеза устройства с указанными значениями всех входов, выходов при одном из входных значений.

Вывод: Был произведен синтез и описание на языке VHDL устройства, параллельно реализующего 3 функции. В процессе работы были освоены

основы модульного и иерархического проектирования.