- •Глава 14 аналоговые компараторы напряжения

- •Глава 15 электронные ключи

- •Глава 17

- •Глава 18 цифро-аналоговые преобразователи

- •Глава 19 аналого-цифровые преобразователи

- •Глава 20 цифровые микросхемы

- •20.1. Цифровые сигналы

- •Глава 21 сопряжение интегральных схем

- •21.2. Управление входами ттл и кмоп

- •Глава 22 дешифраторы и шифраторы

- •Глава 23 мультиплексоры и демультиплексоры

- •Глава 24 сумматоры

- •Глава 25 триггеры

- •Глава 26 счетчики импульсов

- •Глава 27 регистры

- •Глава 28 полупроводниковые запоминающие устройства

- •Глава 29 программируемые логические интегральные схемы

Глава 26 счетчики импульсов

Рис. 26.1. Суммирующий счетчик

Рис. 26.2. Временные диаграммы счетчика

Рис. 26.3. Вычитающий счетчик

Рис. 26.4. Счетчики: а) К155ИЕ5, б) К155ИЕ2

Рис. 26.5. Структура счетчика ИЕ5

Рис. 26.6. Структура счетчика ИЕ2

Рис. 26.7. Декады на ИМС: а) типа ИЕ4, б) ИЕ5

Рис. 26.8. Временные диаграммы работы декады

Рис. 26.9. 12-разрядный асинхронный двоичный счетчик

Рис. 26.10. 12-разрядный синхронный двоичный счетчик

Рис. 26.11. Реверсивные счетчики: а) ИЕ6, б) ИЕ7, в) ИЕ12, г) ИЕ13

Рис. 25.12. Функциональная схема реверсивного счетчика с общим входом сложения / вычитания.

Рис. 26.13. Функциональная схема реверсивного счетчика с раздельными входами сложения / вычитания

Рис. 26.14. 8-разрядный реверсивный счетчик

Рис. 26.15. 8-разрядный реверсивный счетчик

Рис. 26.16. Реверсивный счетчик со знаковым выходом

Рис. 26.17. Счетчик с программируемым коэффициентом деления

Рис. 26.18. Генератор линейно изменяющегося напряжения

Рис. 26.19. Принципиальная схема и временные диаграммы работы счетчика-делителя типа ИЕ1

Глава 27 регистры

Рис. 27.1. Параллельный регистр

Рис. 27.2. Последовательный регистр

Рис. 27.3. Реверсивный регистр

Рис. 27.4. Условные графические обозначения регистров

Рис. 27.5. ИМС К155ИР1

Рис. 27.6. Двенадцатиразрядный сдвигающий регистр

Рис. 27.7. Делители частоты на 2, 3, 6, 7

Рис. 27.8. Параллельные регистры

Рис. 27.9. Реверсивный регистр

Таблица 27.1

Режимы работы регистра

Рис. 27.10. Реверсивный регистр КР1533ИР24

Таблица 27.2

Режимы работы КР1533ИР24

Таблица 27.3

Состояния шины КР1533ИР24

Глава 28 полупроводниковые запоминающие устройства

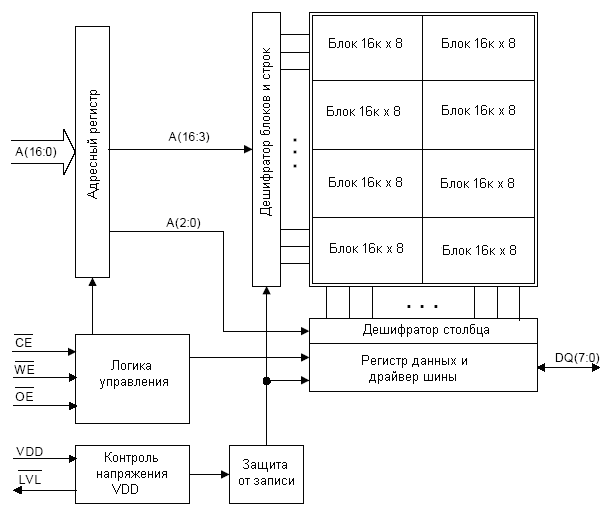

Рис.28.1. Обобщенная структурная схема большой интегральной схемы ЗУ

Рис.28.2. Структура ЗУ типа 2D

Рис.28.3. Структура ЗУ 3D

Рис.28.4. Структура типа 2DM

Рис.28.5. Принципиальная схема статического ЗЭ на МОП-транзисторах

Рис.28.6. Условное графическое обозначение статического ОЗУ типа 132РУ6

Рис.28.7. Статическое ОЗУ с организацией 512К × 16

Рис.28.8. ЗЭ динамического ОЗУ

Рис.28.9. Динамическое ОЗУ A43L4616

Рис.28.10. Условное графическое обозначение ПЗУ

Рис. 28.11. Схема ПЗУ

Таблица 28.1

Состояние простого ПЗУ

Слово |

Двоичное представление |

||||||||

А0 |

А1 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

D8 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

Рис. 28.12. Фрагмент схемы ППЗУ

Рис.28.13. Фрагмент схемы РПЗУ

а) б)

Рис.28.14. Структуры на основе NOR (a) и NAND (б)

Рис.28.15. Схема внешних выводов (а), назначение выводов (б) и структурная схема (в) Flas-памяти

Рис.28.16. Организация массива памяти NАND-структуры

а)

б)

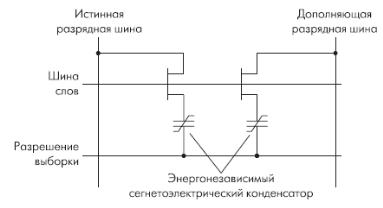

Рис.28.17. Ячейка памяти типа 2Т/2С (а) и 1Т/1С (б)

Рис.28.18. Структурная схема FRAM FM20L08

Табл.28.1.

Выводы FRAM FM20L08

Наимено- вание вывода |

Описание |

A(16:0) |

Адресные входы |

|

Вход выбора микросхемы |

|

Чтение |

|

Запись |

DQ(7:0) |

Линии данных |

|

Выход схемы контроля напряжения |

VDD |

Напряжение питания 3.3В |

VSS |

Общий питания |

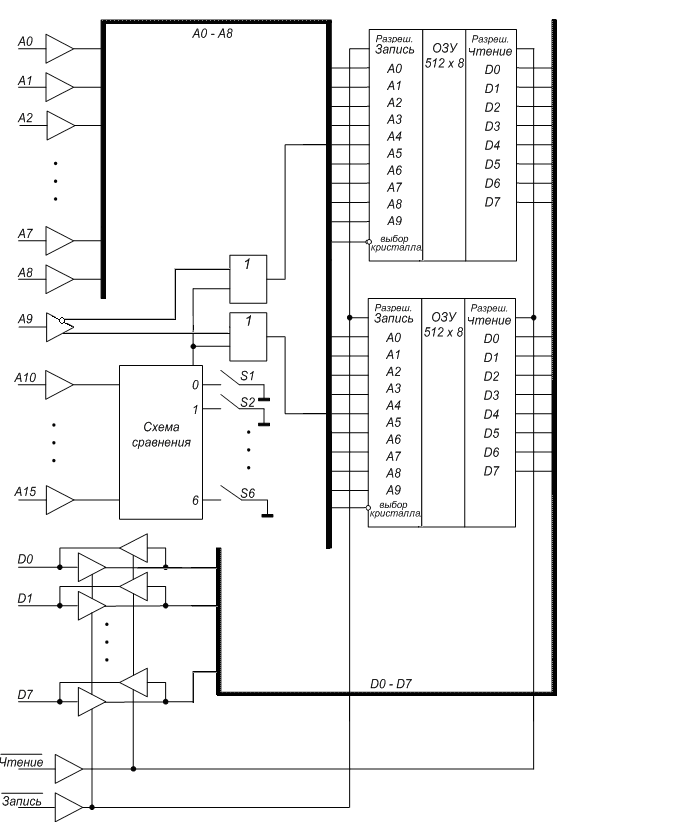

Рис. 28.19. Структурная схема памяти МП системы