- •Визначення автоматів та їх класифікація. Автомати Мілі і Мура.

- •МашинаТьюрінга. Машина Поста. Гіпотеза Черча. Поняття алгоритму.

- •Система числення. Алгоритми переведення чисел з однієї системи в іншу. Форми і формати зображення чисел в ца.

- •Зображення чисел в прямому, оберненому і доповнених кодах. Модифіковані коди.

- •Арифметичні дії над двійковими числами в прямому, оберненому і доповнених кодах.

- •Представлення чисел з плаваючою комою. Стандарт іеее 754. Числа з одинарною та подвійною точністю.

- •Основні поняття алгебри логіки. Логічні функції та їх властивості. Аналогія між логічною функцією та комбінаційною схемою.

- •Функція двох змінних. Поняття про логічний базис.

- •Днф та дднф (кнф та дкнф). Представлення функцій в дднф та дкнф.

- •Мінімізація логічних функцій. Метод Квайна. Мінімізація логічних функцій за допомогою графа – стіжка.

- •Дешифратори та шифратори. Прямокутні (матричні), пірамідальні, дво та багато ступеневі дешифратори, їх швидкодія та енергоспоживання.

- •Аналіз та синтез мультиплексорів та демультиплексорів. Побудова мультиплексорів та демультиплексорів на основі дешифраторів.

- •Схеми реалізації суматорів на базових елементах логіки. Наскрізне перенесення в багато розрядних суматорах. Арифметико логічні пристрої.

- •15. Аналіз та синтез цифрових автоматів зі зворотніми зв’язками. Стійкі стани. Режими генерації.

- •16. Аналіз та синтез суматорів. Напівсуматори. Повні суматори. Реалізація н-розрядних суматорів.

- •17. Аналіз та синтез суматорів. Паралельні, послідовні та паралельно послідовні суматори. Арифметико-логічні пристрої.

- •20. Аналіз та синтез цифрових компараторів.

17. Аналіз та синтез суматорів. Паралельні, послідовні та паралельно послідовні суматори. Арифметико-логічні пристрої.

В багаторозрядному суматорі паралельної дії, згідно визначення, операції складання повинні виконуватися одночасно по всіх розрядах заданих двійкових чисел. З цього виходить, що такий суматор повинен мати окремі апаратні засоби для виконання складання в кожному розряді.

Розглянемо типову структуру 4-розрядного суматора, виконаного з використанням трьох однорозрядних суматорів та одного напівсуматора (рисунок 17.5). Розряди кодів складників подаються на відповідні входи суматорів, виходи суми яких приєднуються до перших входів логічних елементів І, що використовуються в якості вихідних ключів, на другі входи яких подається сигнал Z, що визначає момент зчитування результату. Вихід сигналу перенесення суматора нульового розряду подається на вхід перенесення суматора першого розряду і т.д.

Отже, для отримання на виході сигналу, що дорівнює реальній сумі вхідних кодів, необхідно, щоб сигнал перенесення послідовно сформувався на виходах суматорів всіх розрядів. Таким чином, незалежно від того, що для складання в кожному розряді використовується окремий суматор, реальний час виконання операції в даній схемі визначається послідовним перенесенням сигналу Р із розряду в розряд. Тому, результат, що може бути знятий на виході схеми через час, рівний часу складання в одному розряді, не буде реальним значенням потрібної суми.

Для складання багаторозрядних двійкових чисел необхідно послідовно з'єднатипотрібну

кількість суматорів

так, як показано на рис. 9.5. Тут ![]() і

і

![]() - 4-розрядні доданки,

- 4-розрядні доданки,

![]() -

4-розрядна сума

-

4-розрядна сума

Арифметико-логічний пристрій (АЛП) призначений для виконання арифметичних і логічних операцій над числами (словами), що надходять до нього, за сигналами з пристрою керування. Основні операції, що виконує АЛП – це додавання та множення. Має вісім функціональних входів для введення двох чисел A та B, чотири виходи F3-F0 для подання результату дії з числами, чотири входи керування S3-S0 для задання однієї з 16 операцій, вхід V ознаки операцій (1-логічні, 0-арифметичні), вхід переносу Cn, вихід компаратора FA=B та виходи C, G, P для організації паралельного перенесення при нарощуванні розрядності АЛП.

Спрощена блок-схема АЛП

18. D-тригери. Реалізація D-тригерів за допомогою елементів І-НЕ, АБО-НЕ. Режим прозорості D-тригера.

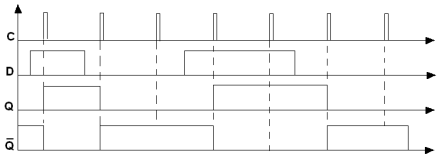

D-тригер має один інформаційний вхід D (data - дані). Інформація з входу D заноситься в тригер по позитивному перепаду імпульсу на рахунковому вході С і зберігається до наступного позитивного перепаду на рахунковому вході тригера. Крім рахункового С і інформаційного D входів, тригер забезпечений асинхронними настановними R і S входами. Настановні входи пріоритетні. Вони встановлюють тригер незалежно від сигналів на входах С і D. Функціонування D-тригера описується таблицею переходів (табл. 2.5), таблицею функцій збудження (табл. 2.6) і діаграмами вхідних і вихідних сигналів (рис. 2.7).

Рис. 2.7.

Характеристичне рівняння D-тригера:

Рівняння показує, що перебування тригера на (t+1) - такті рівне вхідному сигналу в момент, попереднього тактовому перепаду сигналу С. Умовне позначення D-тригера представлене на рис

![]()

Схема на елементах І-НЕ:

Режим прозорості це коли на вхід С подається активний рівень і тригер повторює на виході всю інформацію з входу D.

19. T-тригери. Реалізація Т-тригерів за допомогою елементів І-НЕ, АБО-НЕ.

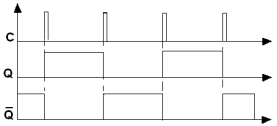

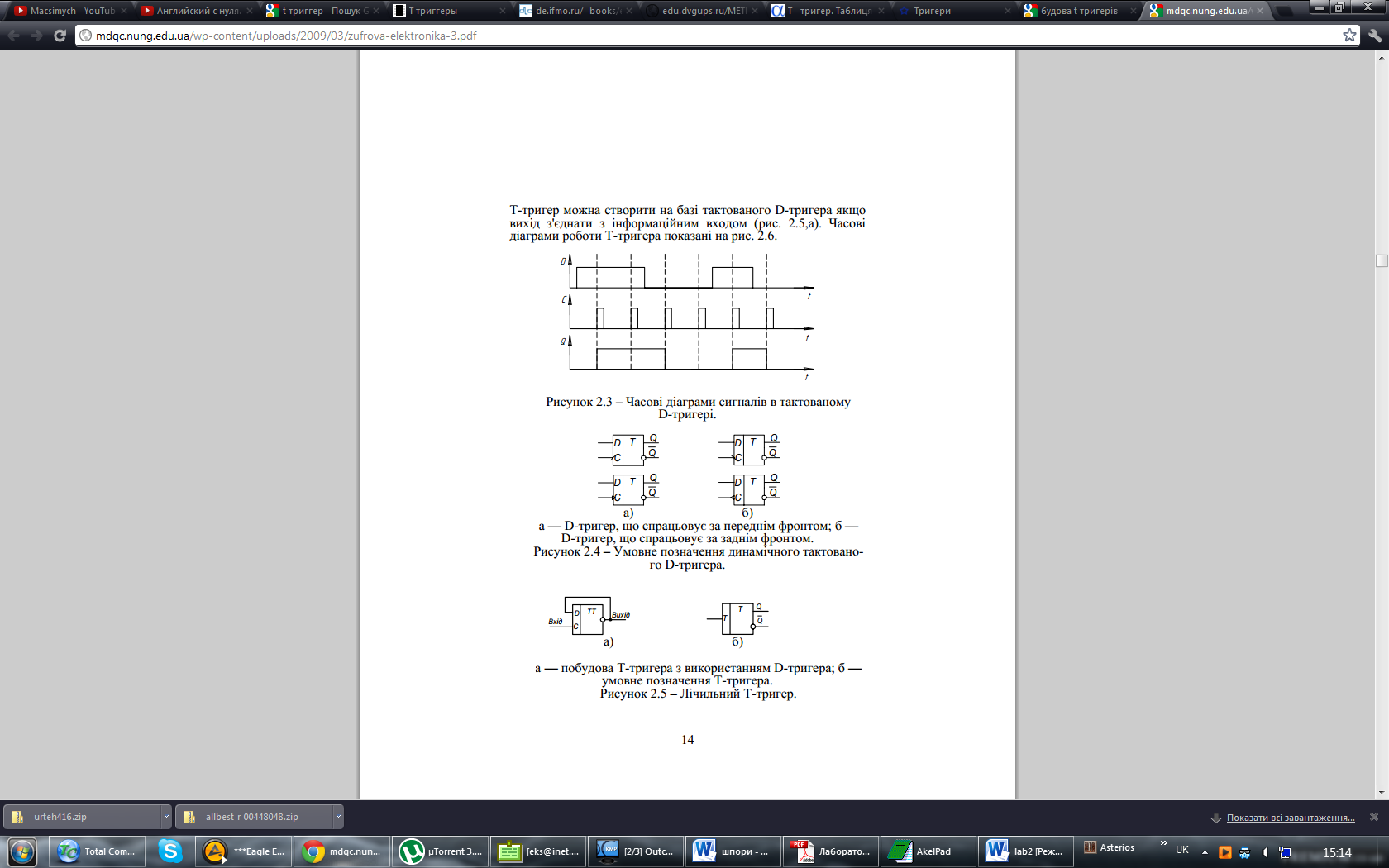

На основі JK-тригерів і D-тригерів можна побудувати схеми, що здійснюють так званий рахунковий режим. Такі схеми називають Т-тригерами або рахунковими тригерами, пов'язуючи з цим спосіб їх функціонування. На рис. 2.9 представлені схеми організації Т-тригера на основі JK і D-тригерів. Рахунковий режим ілюструється часовими діаграмами рис. 2.10

У JK-тригері з входами установки логічним нулем рахунковий режим реалізується шляхом подачі констант J=K=1 і R=S=1 і вхідного сигналу Т на вхід С. Згідно з таблицею функціонування (табл. 2.3 і 2.4) при кожному негативному перепаді вхідного сигналу Т стан тригера змінює своє значення на протилежне.

У D-тригері рахунковий режим реалізується за допомогою зворотного зв’язку (на вхід D подається сигнал з інверсного виходу). Таким чином, завжди існує нерівність сигналу на вході D і сигналу на виході Q: якщо Q=1, D=0. Отже, при кожному позитивному перепаді сигналу на рахунковому вході С, відповідно до принципу дії D-тригера стан виходу змінюватиметься на протилежний.

Вхід D треба подати сигнал з інверсного входу.

JK- як Т тригер:

![]()