Курсовая работа6 / МОЁ_ПУ

.docСанкт-Петербургский Государственный Электротехнический Университет

имени В.И. Ульянова (Ленина) «ЛЭТИ»

Кафедра ВТ

Пояснительная записка

к курсовой работе

по дисциплине

″ Периферийные устройства ЭВМ ″

Вариант 6

Факультет : КТИ

Группа: 2373

Выполнила: Паршина А.В.

Проверил: Фураев И.А.

Санкт-Петербург

2006

Содержание

|

Задание |

3 |

|

Уточнение задания |

3 |

|

Структурная схема устройства |

4 |

|

Выбор элементной базы |

5 |

|

Программная модель устройства |

14 |

|

Заключение |

16 |

|

Список литературы |

17 |

|

Приложение 1 |

18 |

|

18 |

|

18 |

|

3. Пример программы на C для работы с устройством |

18 |

|

Приложение 2 - схема принципиальная электрическая |

|

|

Приложение 3 - перечень элементов |

|

1. Задание

Разработать систему сбора аналоговой информации со следующими характеристиками:

|

Магистраль |

ISA |

|

Диапазон входных напряжений |

2 В |

|

Количество каналов |

1 |

|

Входное сопротивление |

50 Ом |

|

Разрядность АЦП |

12 |

|

Максимальная частота дискретизации |

10 МГц |

|

Гальваническая развязка от магистрали |

нет |

|

Режимы обмена с магистралью |

программный |

|

по заполнению буфера |

|

|

Объем буфера |

128К |

1.1 Уточнение задания

Устройство представляет собой систему сбора аналоговой информации для цифровой ЭВМ. Информация представляет собой напряжение, изменяющееся в диапазоне от -2 до +2 вольт, подаваемое на аналоговый вход устройства. Устройство имеет один 16-разрядный программно-доступный регистр.

При помощи программирования устройства, т.е. записи определенной информации в управляющий регистр, должны быть доступны следующие возможности:

- программный запуск, т.е. запуск после установки определенного бита в регистре управления;

-

программное чтение данных, т.е. чтение считанной и оцифрованной информации из программы путем чтения порта ввода/вывода;

-

выставление запроса на прерывание при переполнении FIFO.

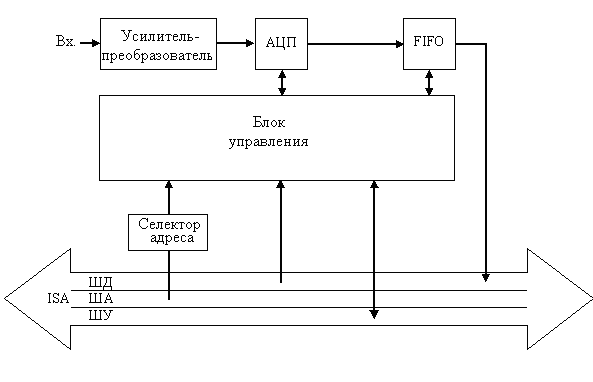

2. Структурная схема устройства

Обозначения:

УП - усилитель-преобразователь; его задача - преобразовать сигнал к диапазону измерения АЦП и обеспечить требуемое входное сопротивление;

АЦП - аналого-цифровой преобразователь; преобразует входной аналоговый сигнал в цифровую форму;

FIFO - последовательная память, организованная по принципу "первый вошёл - первый вышел"; накапливает данные в режимах программного обмена и обмена по прерыванию;

БУ – блок управления; содержит цифровую часть схемы, отвечающую за программное взаимодействие через порты ввода/вывода, обработку ошибок, управление режимами, прерывания и т.д.

СА - селектор адреса; в случае появления адреса устройства на шине адреса СА формирует соответствующие сигналы и передает их в БУ;

ISA - шина ЭВМ, к которой подключено устройство;

ШД - шина данных;

ША - шина адреса;

ШУ - шина управления.

3. Выбор элементной базы

-

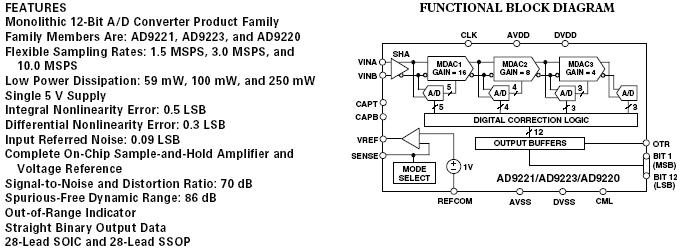

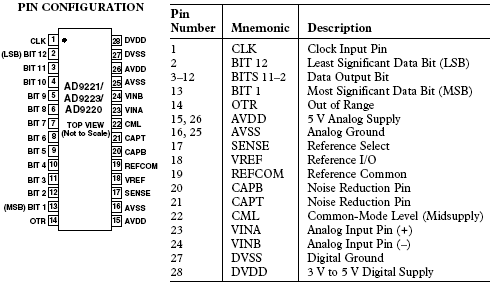

Аналого-цифровой преобразователь

Назначение аналого-цифрового преобразователя (АЦП) -преобразовывать аналоговый сигнал, поступающий с коммутируемых каналов в цифровую форму.

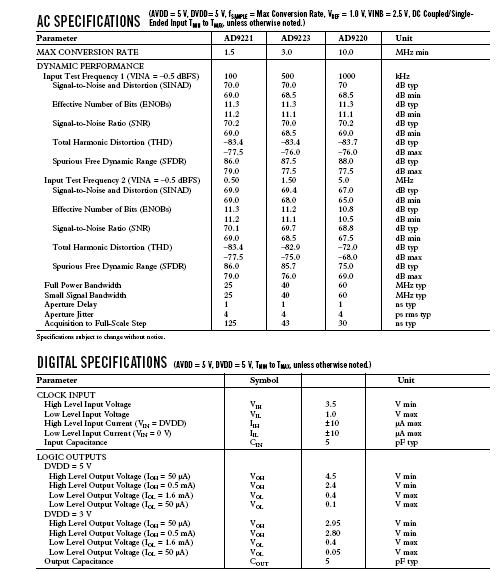

Для реализации задания был выбран 12-разрядный АЦП фирмы Analog Devices AD9220.

Далее приводятся некоторые характеристики выбранного АЦП:

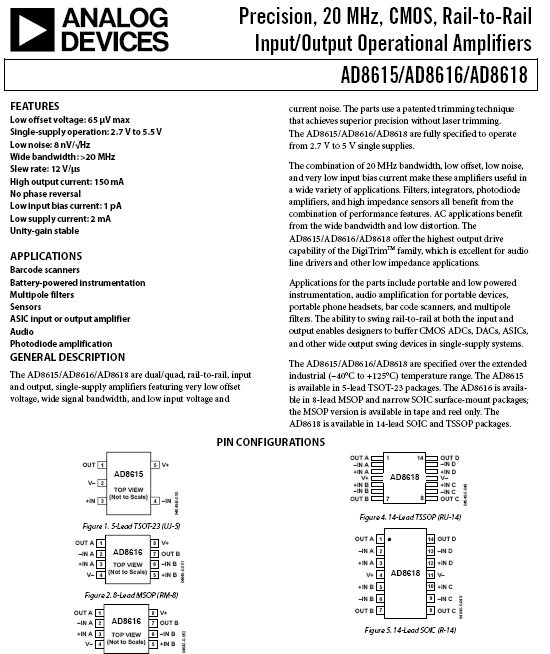

3.2 Усилитель

В данном случае усилитель используется для решения следующих задач:

1) на вход выбранного АЦП подается напряжение в диапазоне 0…5В,а с канала поступает -2..+2В;

2) обеспечение необходимого сопротивления, т.к. с канала поступает 50 Ом.

Выбран усилитель фирмы Analog Devices AD8616:

|

|

|

Схема включения усилителя и АЦП:

причем: R2=R3, R1=R4.

Данная схема включения обеспечивает необходимое напряжение на аналоговом входе АЦП следующим образом: напряжение -2..+2В смещается на 2В, а затем при помощи усилителя с коэффициентом усиления Kу = 1.25 преобразуется к диапазону 0..5В.

Kу = R2/R1=1.25

3.3 Буфер, размером 128К

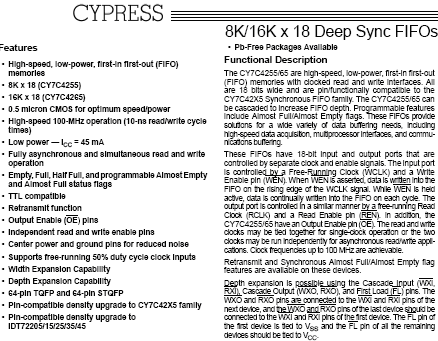

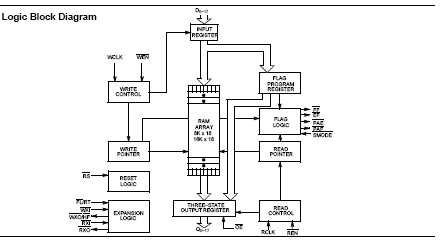

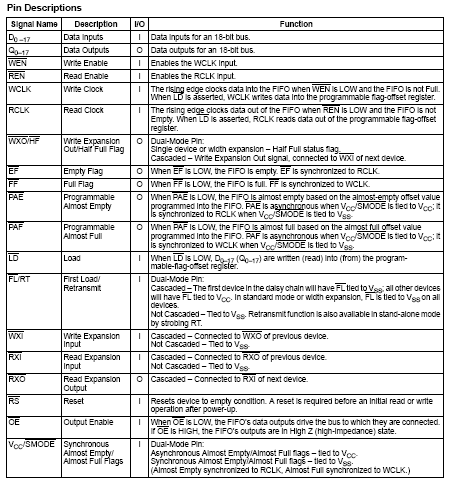

В качестве буфера была выбрана микросхема FIFO CY7C4255 фирмы Cypress, объемом 128К.

.

3.4 Элементы серии 1554.

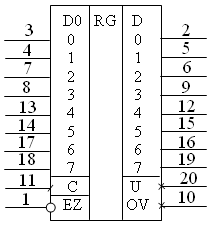

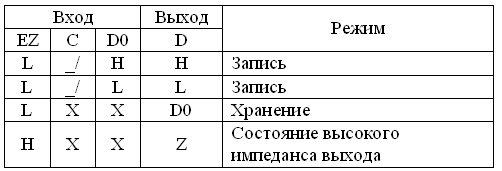

КР1554ИР23:

Микросхема представляет собой 8-разрядный управляемый по фронту регистр с параллельным вводом-выводом данных, с тремя состояниями на выходе. Корпус типа 2140.20-8, масса не более 2,6 г, 4321.20 – В.

Назначение выводов: 1 – вход разрешения состояния высокого импеданса выхода EZ; 2, 5, 6, 9, 12, 15, 16, 19 – выходы данных D0…D7; 3, 4, 7, 8, 13, 14, 17, 18 – входы данных DО0…DО7; 10 – общий; 11 – вход тактового импульса по уровню С; 20 – напряжение питания.

КР1554ЛИ1 – 4 логических элемента 2И

КР1554ЛЛ1 – 4 логических элементов 2ИЛИ

4. Программная модель устройства

Устройство имеет 16-разрядный программно-доступный регистр, которому присвоен условный адрес BASE. Этот регистр доступен как для чтения, так и для записи.

Формат регистра при записи:

содержимое данного регистра определяет команду, передаваемую устройству, при этом регистр имеет следующий формат:

разрешение старта

разрешение прерывания по признаку

"ПЕРЕПОЛНЕНИЕ FIFO"

Не используются

Сброс FIFO

назначения разрядов регистра при записи в него информации:

CSR(0) (разрешение старта), запись 1 в этот разряд разрешает работу АЦП, которое преобразует аналоговое значение в цифровой сигнал;

CSR(1) – (разрешение прерывания по переполнению FIFO), запись 1 в этот разряд разрешает выдачу прерывания на магистраль при переполнении буфера;

CSR(2) – (сброс FIFO), запись 1 в этот разряд приводит к сбросу указателей записи и чтения в буферном ОЗУ типа FIFO;

CSR(3 - 15) – не используется.

Формат регистра при чтении:

содержимое данного регистра определяет состояние устройства

назначение разрядов регистра при чтении:

CSR(0) – (признак переполнения FIFO), единичное значение этого разряда означает возникновение в устройстве переполнения буфера FIFO;

CSR(1 - 3) – не используется;

CSR(4 - 15) – (значащие разряды), двоичный код преобразованного АЦП аналогового входного сигнала.

Заключение

В результате выполнения данного курсового проекта было разработано периферийное устройство для сбора аналоговой информации. Устройство предназначено для подключения к шине ISA. Была разработана программная модель устройства и программа на C, демонстрирующая работу с устройством.

Список литературы:

-

Справочник. Интегральные микросхемы и их зарубежные аналоги (серии КБ1502 – К1563). Нефедов А.В. Москва, РадиоСофт, 2001 г.

-

Аппаратные интерфейсы ПК. Энциклопедия. М.Гук. СПб. Питер, 2003 г.

-

Аппаратные средства IBM PC. Энциклопедия. М.Гук. СПб. Питер, 2002 г.

-

Цифровая схемотехника. Е.П. Угрюмов. СПб. БХВ-Петербург, 2002г.

5. http://www.analog.com/

Приложение 1

1. Описание функционирования схемы

Сигналы с шины ISA приходят на ПЛМ и там дешифруются. Если пришел сигнал старта, то запускается АЦП, которое преобразует аналоговое значение в цифровой сигнал. Далее данные поступают в буфер FIFO. При переполнении буфера происходит прерывание (или пользователь сам отслеживает переполнение буфера по соответствующему флагу в CSR). По прерыванию пользователь считывает данные из буфера, задавая адрес регистра DR(см. регистровую модель).

2. Реализуемые на ПЛМ сигналы

Адрес CSR – 0x00h

Адрес DR – 0x02h

Обозначим:

SCSR = !AEN&!A9&!A8&!A7&!A6&!A5&!A4&!A3&!A2&!A1&!A0

SDR = !AEN&!A9&!A8&!A7&!A6&!A5&!A4&!A3&!A2&!A1&A0

|

Название |

Функция |

|

WRCSR |

!IOW & SCSR |

|

RDCSR |

!IOR & SCSR |

|

RDDR |

!IOR & SDR |

3. Листинг программы работы с устройством

#include<stdio.h>

#include<conio.h>

#include<dos.h>

; Переход к главной подпрограмме.

;--------------------------------------------

CSEG AT 0

LJMP init

; Переход к подпрограмме обработки прерывания.

;---------------------------------------------------------------

CSEG AT 30h

LJMP prog_Int

init:

char answer, temp;

int mark = 0;

FILE *pointer = fopen("c:\rezults", "w");//в файл записывается результат

do

{

clrscr();

_setcursortype(_NOCURSOR);

printf("\n Program example.\n");

printf("\n 1. Start.");

printf("\n 2. Enable IRQ.");

printf("\n 3. Reset FIFO.");

printf("\n 4. Quit.");

fflush(stdin);

answer = getch();

switch (answer)

{

case '1':

clrscr();

outport(0x00, 0x01); break;

case '2':

clrscr();

outport(0x00, 0x02); break;

case '3':

clrscr();

outport(0x00, 0x03);

break;

default: break;

}

} while (answer != '4');

loop:

JMP loop

IntSG SEGMENT CODE

RSEG IntSG

prog_Int:

temp = inport(0x02);

fwrite(&temp, 1, 1, pointer);

RETI

END