Курсовая работа7 / Курсовая

.docМинистерство образования Российской Федерации

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ «ЛЭТИ» ИМЕНИ В.И. УЛЬЯНОВА (ЛЕНИНА)

Факультет компьютерных технологий и информатики

Кафедра вычислительной техники

Пояснительная записка

к курсовой работе по дисциплине:

"Периферийные устройства и интерфейсы"

Преподаватель: Головина Л.К.

Выполнил: 2372 Попов А.А.

С анкт-Петербург

2006

анкт-Петербург

2006

Оглавление:

1. Задание…………………………………………………………………………………………………..3

2. Программная модель устройства …………………………………………………………………….4

2.1. Регистр CSR…………………………………………………………………………………..4

2.2. Регистр DR……………………………………………………………………………………5

2.3 Регистр DR2 ….........................................................................................................................5

3. Структурная схема устройства………………………………………………………………………..6

4. Описание элементной базы…………………………………………………………….……………...7

4.1. Описание используемого АЦП……………………………………………………………...7

4.2. Элементы серии 1554………………………………………………………………………..11

4.3 Описание буфера FIFO…………………………………………………………....…………12

4.4 Описание ЦАП ............………………………………………………………...…………….16

4.5 Описание усилителя....………………………………………………………...…………….18

5. Список использованной литературы…………………………….…………………………………..19

Приложение А Описание функционирования схемы…………………………………………………20

Приложение Б Листинг программы работы с устройством…………………………………………..21

1. Задание.

Вариант 7: « Система сбора аналоговой информации ».

Магистраль: ISA

Диапазон входных напряжений: +-1В

Количество каналов: 1

Входное сопротивление: 50 Ом

Разрядность АЦП: 8

Максимальная частота дискретизации: 20 МГц

Гальваническая развязка от магистрали ISA: нет

Режимы обмена с магистралью: программный, с прерыванием

по заполнению буфера. Объем буфера 128К.

Особые требования: синхронизация запуска по достижении вход-

ным сигналом программируемого уровня.

2. Программная модель устройства.

Устройство имеет два 8-разрядных программно-доступных регистра, которым присвоены следующие условные названия и адреса:

|

Название |

Адрес |

Разрядность |

Семантика |

|

CSR |

0x**0 |

8 |

Регистр команд и состояния |

|

DR |

0x**1 |

8 |

Регистр данных |

|

DR2 |

0x**2 |

8 |

Регистр данных для ЦАП |

2.1. Регистр CSR.

Этот регистр доступен как для чтения, так и для записи. Содержимое устройства при записи трактуется как команда, а при чтении как набор флагов.

Запись:

1 2 3 4 5 6 7 0

сброс FIFO

разрешение прерывания по переполнению FIFO

разрешение старта

Трактовка при записи :

CSR(0) – (разрешение старта), запись 1 в этот разряд вызывает старт ЦАП, которое преобразует цифровое значение из регистра в аналоговый сигнал, этот сигнал сравнивается с внешним, и если внешний сигнал больше устройство включается

CSR(1) – (разрешение прерывания по переполнению FIFO), запись 1 в этот разряд разрешает выдачу прерывания на магистраль при переполнении буфера

CSR(2) – (сброс FIFO), запись 1 в этот разряд приводит к сбросу указателей записи и чтения в буферном ОЗУ типа FIFO.

CSR(3 - 7) – не используется.

Чтение:

1 2 3 4 5 6 7 0

признак переполнения FIFO

Трактовка при чтении:

CSR(0) – (признак переполнения FIFO), единичное значение этого разряда означает возникновение в устройстве переполнения буфера FIFO.

CSR(1 - 7) – не используется.

2.2. Регистр DR.

Основное назначение регистра данных – это считывание из него информации, записанной в буфер FIFO. Является абстракцией, т.к. на самом деле значения считываются из буфера FIFO

Чтение:

1 2 3 4 5 6 7 0

значащие разряды

Трактовка при чтении:

CSR(0-7) – (значащие разряды), двоичный код преобразованного АЦП аналогового входного сигнала.

2.3. Регистр DR2.

Основное назначение регистра данных для ЦАП – это задание уровня сигнала по которому устройство стартует

Запись:

1 2 3 4 5 6 7 0

значащие разряды

Трактовка при записи:

CSR(0-7) – (значащие разряды), двоичный код преобразованного АЦП аналогового входного сигнала.

3. Структурная схема.

4. Описание элементной базы.

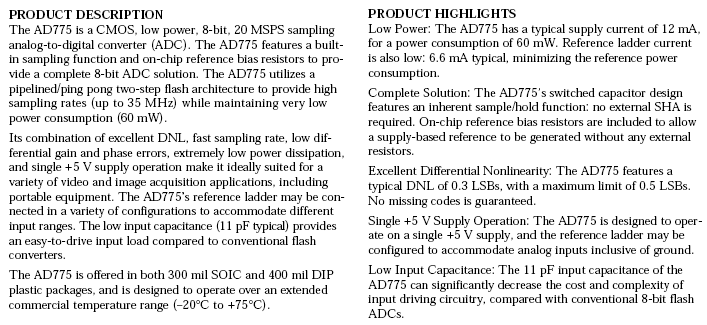

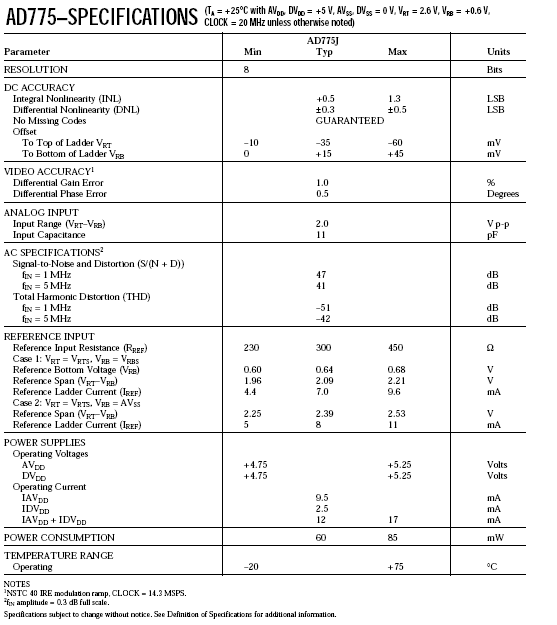

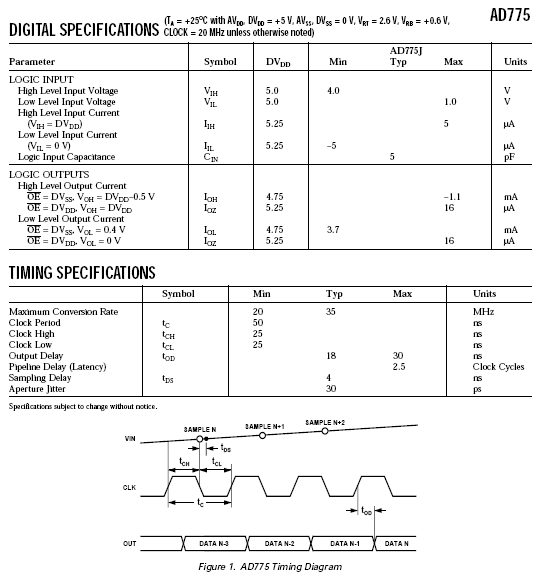

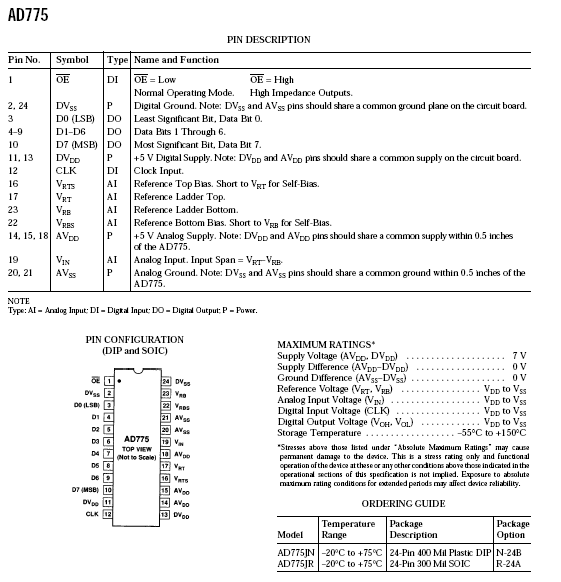

4.1. Описание используемого АЦП.

Из нескольких рассмотренных вариантов аналого-цифровых преобразователей в наибольшей степени поставленному заданию отвечает модель AD775.

Общее описание:

4.2. Элементы серии 1554.

КР1554ИР23:

Микросхема представляет собой 8-разрядный управляемый по фронту регистр с параллельным вводом-выводом данных, с тремя состояниями на выходе. Корпус типа 2140.20-8, масса не более 2,6 г, 4321.20 – В.

Назначение

выводов: 1 – вход разрешения состояния

высокого импеданса выхода EZ;

2, 5, 6, 9, 12, 15, 16, 19 – выходы данных D0…D7;

3, 4, 7, 8, 13, 14, 17, 18 – входы данных DО0…DО7;

10 – общий; 11 – вход тактового импульса

по уровню С; 20 – напряжение питания.

-

Вход

Выход

Режим

EZ

C

D0

D

L

_/

H

H

Запись

L

_/

L

L

З

З

D0 RG D

-

0

-

1

-

2

-

3

-

4

-

5

-

6

-

7

C U

EZ OV

апись

апись

L

X

X

D0

Х

ранение

ранениеH

X

X

Z

Состояние высокого импеданса выхода

-

КР1554ЛИ1 – 4 логических элемента 2И

КР1554ЛН1 – 6 логических элементов НЕ

КР1554ЛЛ1 – 4 логических элементов 2ИЛИ

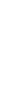

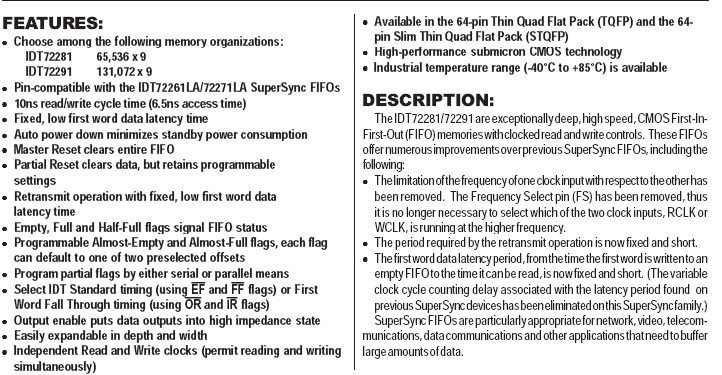

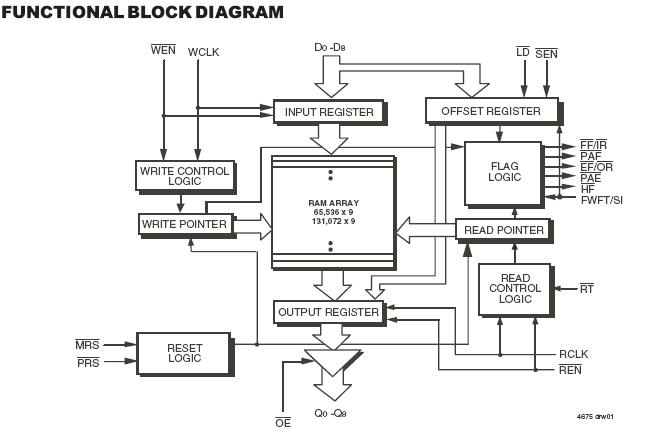

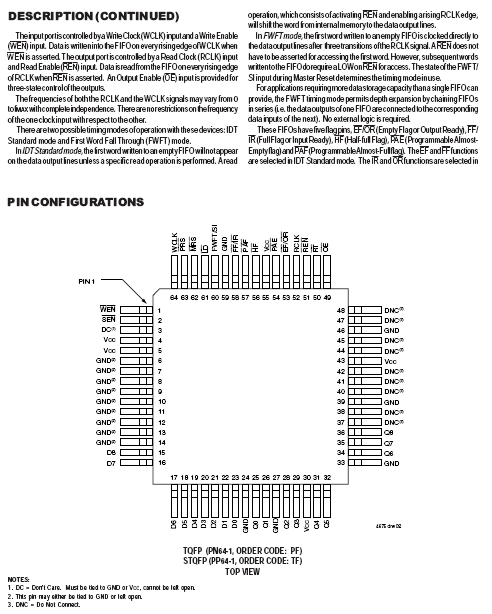

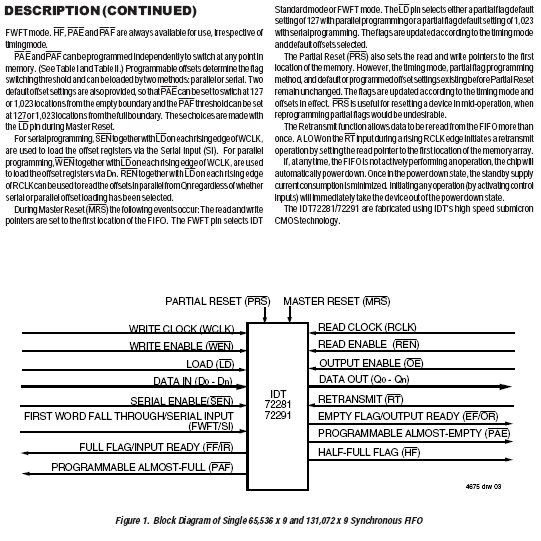

4.3. Описание буфера FIFO.

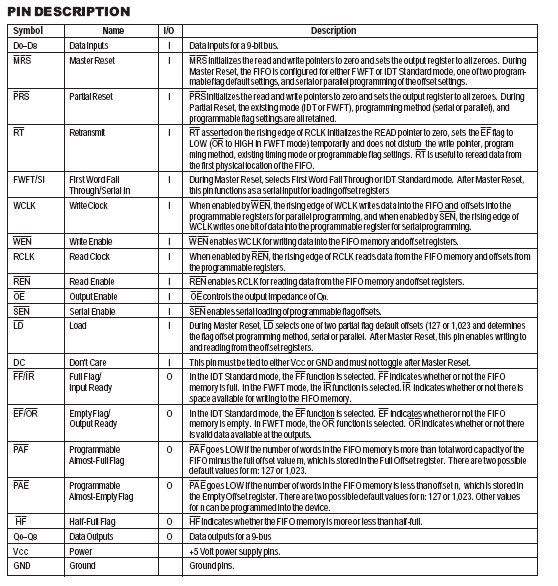

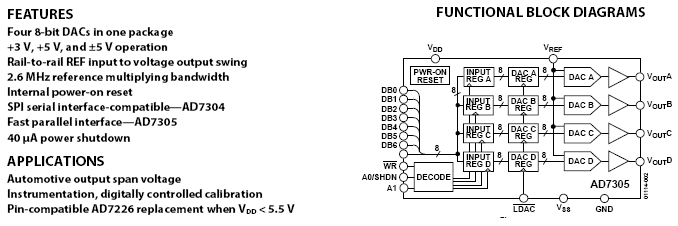

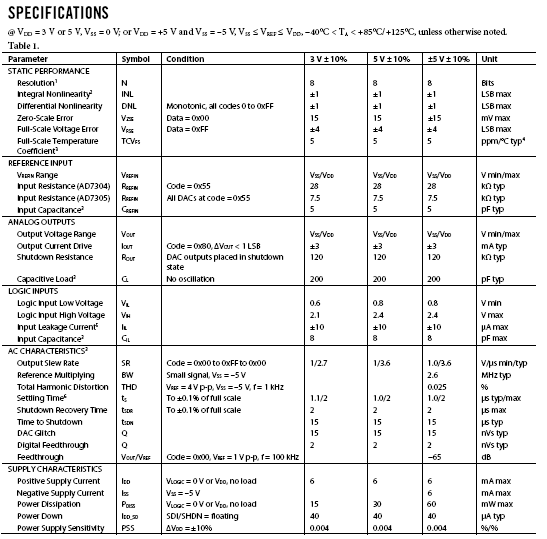

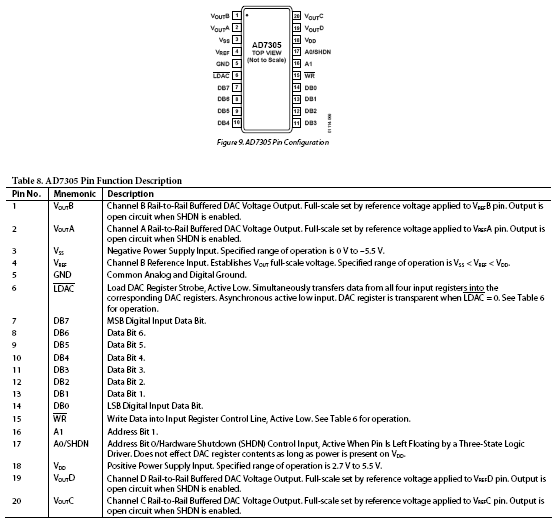

4.4. Описание ЦАП.

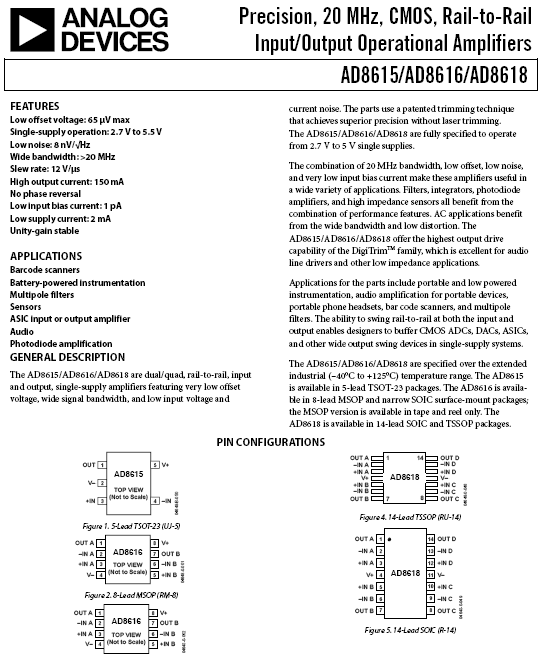

4.5 Описание операционного усилителя

5. Список использованной литературы.

-

Справочник. Интегральные микросхемы и их зарубежные аналоги (серии КБ1502 – К1563). Нефедов А.В. Москва, РадиоСофт, 2001 г.

-

Аппаратные интерфейсы ПК. Энциклопедия. М.Гук. СПб. Питер, 2003 г.

-

Аппаратные средства IBM PC. Энциклопедия. М.Гук. СПб. Питер, 2002 г.

-

Цифровая схемотехника. Е.П. Угрюмов. СПб. БХВ-Петербург, 2002г.

-

Конспект лекций по дисциплине: Периферийные устройства и интерфейсы. Лектор: Молодцов В.О.

Приложение A

Описание функционирования схемы

1. Общий алгоритм работы устройства

Изначально сигналы с шины ISA приходят на ПЛМ и там дешифруются(см. п.2). Если это пришел сигнал старта, то запускается ЦАП, которое преобразует цифровое значение из регистра DR2 в аналоговый сигнал. Этот аналоговый сигнал, сравнивается с внешним сигналом, и если внешний сигнал больше, то запускается АЦП, данные с которого поступают на буфер. При переполнении буфера происходит прерывание (или пользователь сам отслеживает переполнение буфера по соответствующему флагу в CSR). По прерыванию пользователь считывает данные из буфера, задавая адрес регистра DR(см. регистровую модель).

2. Реализуемые на ПЛМ сигналы

Адрес CSR – 0x00h

Адрес DR – 0x01h

Адрес DR2 – 0x02h

Введем обозначения:

SCSR = !AEN&!A9&!A8&!A7&!A6&!A5&!A4&!A3&!A2&!A1&!A0

SDR = !AEN&!A9&!A8&!A7&!A6&!A5&!A4&!A3&!A2&!A1&A0

SDR2 = !AEN&!A9&!A8&!A7&!A6&!A5&!A4&!A3&!A2&A1&!A0

|

Название |

Функция |

|

WRCSR |

!IOW & SCSR |

|

RDCSR |

!IOR & SCSR |

|

RDDR |

!IOR & SDR |

|

WRDR2 |

!IOW & SDR2 |

Приложение Б

Листинг программы работы с устройством

#include<stdio.h>

#include<conio.h>

#include<dos.h>

void main(void)

{

char answer, temp, dr2;

int mark = 0;

FILE *pointer = fopen("c:\rezults", "w");//file for rezults

do

{

clrscr();

_setcursortype(_NOCURSOR);

printf("\n Program example.\n");

printf("\n 1. Start.");

printf("\n 2. Enable IRQ.");

printf("\n 3. Reset FIFO.");

printf("\n 4. Change DR2.");

printf("\n 5. Quit.");

fflush(stdin);

answer = getch();

switch (answer){

case '1':

clrscr();

outportb(0x00, 0x01); break;

case '2':

clrscr();

outportb(0x00, 0x02);

break;

case '3':

clrscr();

outport(0x00, 0x04);

break;

case '4':

scanf(dr2);

clrscr();

outport(0x02, dr2);

break;

default: break;

}

if(irq = IRQ7){ temp = inport(0x01);

fwrite(&temp, 1, 1, pointer);

}

}

}

while (answer != '5');

}