- •Отчёт по курсовой работе.

- •1. Уточнение структуры системы.

- •2. Проектирование структуры внешних выводов.

- •3. Форматы данных

- •4. Организация памяти

- •5. Формат команды

- •6. Система команд

- •7. Внутренняя организация

- •8. Алгоритмы исполнения отдельных операций

- •8.1. Выборка команды

- •8.2. Обработка адресной части команды.

- •8.3. Выполнение арифметических и логических операций

Федеральное агентство по образованию

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ»

Ф акультет

компьютерных технологий и информатики

акультет

компьютерных технологий и информатики

Кафедра ВТ

Отчёт по курсовой работе.

Дисциплина:

Архитектура ЭВМ

Вариант: Г-6

Выполнил: студент гр. 3371

Гречухин М.

Преподаватель: Казак

Александр Филиппович

Санкт-Петербург, 2007 год.

ЗАДАНИЕ НА КУРСОВУЮ РАБОТУ: спроектировать однокристальный RISC-процессор, основанный на Гарвардской архитектуре и предназначенный для встраиваемых применений. Проект должен удовлетворять следующим требованиям:

- разрядность данных: 16 и 32 бита

- адресность команд – 3

- способы адресации: непосредственная, относительная, косвенная

- количество и тип регистров: 16 32-хразрядных регистров общего назначения

- используется совмещённая шина адрес-данные

- данные: память данных – 128 кбайт, шина – 16-тиразрядная

- команды: память команд – 16 кбайт, шина – 32-хразрядная

- ввод-вывод: по аналогии с памятью.

- предусмотрена векторная система прерываний

1. Уточнение структуры системы.

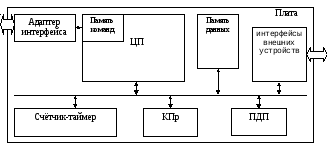

Обобщённая структура системы представлена на рисунке ниже:

Данная структура представляет собой одноплатную ЭВМ, содержащую на себе собственно процессор, память данных, счётчик-таймер и адаптер интерфейса для работы с инструментальной машиной. На плате могут также размещаться дополнительные устройства, в частности, контроллер прерываний (КПр) и контроллер прямого доступа к памяти (ПДП) для организации обмена с памятью данных различных внешних устройств. Касательно разрядности внутренней шины: по ТЗ, объём ОЗУ данных – 128 кбайт = 128*1024 = 131072 байта. Чтобы адресовать такой объём памяти, потребуется 17 разрядов. Однако следует помнить о том, что по заданию организация обмена с внешними устройствами осуществляется по тому же принципу, что и с ячейками памяти, адресное пространство делится между памятью и устройствами ввода-вывода. Следовательно, необходимо предусмотреть также адресное пространство ввода-вывода как часть основного адресного пространства. Поэтому шину нужно расширить. Для обеспечения масштабируемости системы шину адреса и данных расширяем до 24 разрядов. Подробная организация памяти и адресного пространства буде приведена позже.

Так как система проектируется для встраиваемых решений, то логично положить создание программного обеспечения на инструментальной машин с использованием кросс-средств и дальнейшее его (ПО) размещение в энергонезависимой памяти команд (к примеру, flash). С целью минимизации времени выборки очередной команды (нет необходимости в циклах чтения команды из внешней памяти) память программ размещается на кристалле процессора и адресуется отдельно от памяти данных.

2. Проектирование структуры внешних выводов.

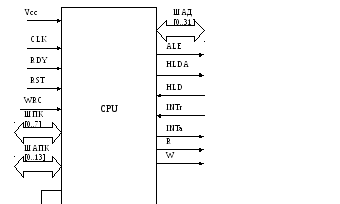

Схема внешних выводов представлена на рисунке ниже:

Пояснение выводов:

ШАД – 24хразрядная шина адреса и данных

ШПК – 8миразрядная шина программирования команд (для прописывания программы в энергонезависимой памяти команд с помощью инструментальной машины)

ШАПК – 14тиразрядная шина адреса программируемой команды (16 кбайт = 16 * 1024 = 16384. Для адресации этого объёма памяти требуется log2(16384)-1 бит, т. е. 14). Используется для задания адреса ячейки памяти команд для записи

WRC (WRite Command) – сигнал, разрешающий запись очередного байта команды в ячейку памяти.

ALE (Address Latch Enable) – разрешает запись адреса во внешний регистр-защёлку

HLD (HoLD) – запрос на захват шины (например, при ПДП)

HLDA (HoLD Acknowledge) – подтверждение захвата шины (например, КПДП)

INTr (INTerrupt request) – запрос на прерывание от КПр

INTa (INTerrupt acknowledge) – подтверждение прерывания от процессора

R (Read) – определение операции чтения на шине

W (Write) – определение операции записи на шине

RST (ReSeT) – аппаратный сброс ЦП

CLK (CLocK) – внешний clock

RDY (ReaDY) – сигнал готовности (для внешних медленных устройств)

Vcc (Voltage) – напряжение питания

GND – земля

Всего получается 59 выводов. Ориентируясь на 68мивыводной корпус, получаем 9 незадействованных выводов, которые можно использовать для увеличения разрядности совмещённой шины адреса и данных. Получим в итоге 32хразрядную совмещённую шину адреса и данных. Последний незадействованный вывод дублирует питание.