- •Элементы и схемы компьютерных систем

- •Классификация элементов и схем эвм

- •Системы элементов компьютерных систем

- •Основные характеристики и электрические параметры элементов и схем эвм

- •Способы представления двоичных чисел

- •Основы алгебры-логики и выполнение логических операций

- •Дизъюнктор

- •Конъюнктор

- •Инвертор

- •Синтез комбинационных схем

- •Минимизация переключательных функций.

- •Диаграммы Вейча

- •Минимизация неполностью опред.Функции

- •Порядок комбин. Схемы

- •Регистры

- •Регистры хранения

- •Сдвиговые регистры

- •Реверсивный регистр

- •Счетчики

- •Суммирующие двоичные счетчики с последовательным переносом(асинхр)

- •Реверсивный счетчик с последовательным переносом

- •Счетчик со сквозным переносом

- •Счетчик с параллельным переносом

- •Построение счетчика с модулем(периодом) 2n

- •Сумматоры

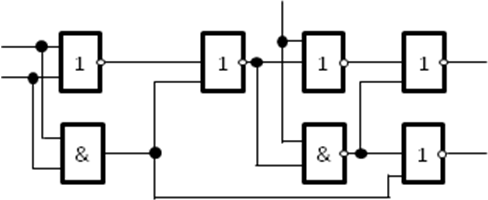

- •Одноразрядный сумматор со сквозным переходом

- •Сумматор со схемой параллельного переноса

- •Дешифраторы

- •Коммутаторы и мультиплeксоры

- •Шифраторы

- •Сдвигатели

- •Компараторы

Одноразрядный сумматор со сквозным переходом

Bi |

Di |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

Для двух отрезков таблица истинности :

тогда

![]() ,

,

![]() .

(**)

.

(**)

Bi |

Di |

qi |

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

еренос

в i+1-й разряд формируется по правилу

еренос

в i+1-й разряд формируется по правилу

В

этой схеме задержка сигнала переноса

в одном разряде = 2t и отсутствует

необходимость формировать интервальные

значения сигналов ![]() .

.

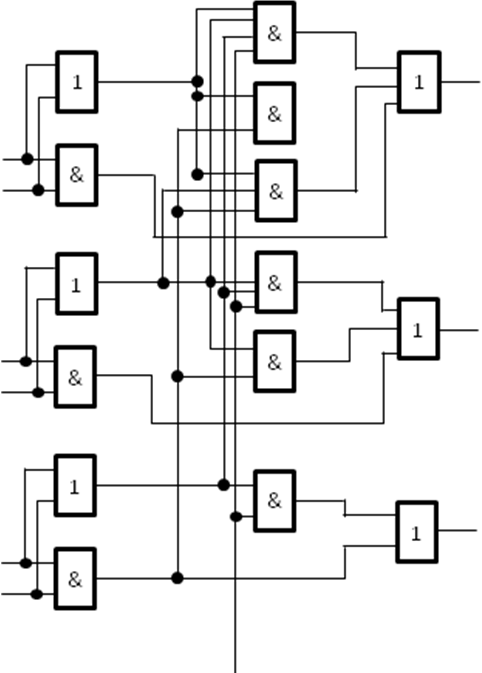

Сумматор со схемой параллельного переноса

Если

исходя из формулы (*) ввести 2 числа,

получаемых из исходных путем поразрядной

конъюнкции и дизъюнкции ![]() ,

,

![]() ,

то соотношение между

и

,

то соотношение между

и ![]() преобразуется

к виду

преобразуется

к виду ![]() .

.

Тогда последовательно получаем:

![]()

![]()

![]()

Д

Д ля

больших разрядностей суммароторов

из-за ограничености входох ЛЭи сложности

схемы параллельного переноса схему

сумматора рбивают на модули ( части ),

например по 4 или 8 разрядов.

ля

больших разрядностей суммароторов

из-за ограничености входох ЛЭи сложности

схемы параллельного переноса схему

сумматора рбивают на модули ( части ),

например по 4 или 8 разрядов.

Внутри модуляреализуется параллельнный перенос; между модулями – м.б. последовательный, а для больших количеств модулей – примеяют внешние схемы ускоренноного параллельного переноса.

1500 ИМ 180 |

||

B0 |

SM |

Q |

B5 |

|

Q5 |

D0 |

|

|

D5 |

|

CP |

CI |

|

CG |

Примеры УГО Sm и LSM

1 |

||

B |

SM |

Q

6 |

D |

|

C D |

C I |

<2> |

|

1533 ИП 3 |

||

CI |

LCM |

CO |

B0 |

|

Q0 |

B3 |

|

Q3 |

D0 |

|

CP |

D5 |

|

C6 |

F0 |

|

C8 |

F3 |

|

|

Mo |

|

|

CO и CI – выход и вход сигнала переноса;

Fi и Mo – управляющие входы Q8 – признак результата.

При Мо = 1 – реализуются поразрядные операции, при Мо = 0 арифметические. Сигналы Fi – задают тип выполненной операции.

0

0 500

ИМ 5

500

ИМ 5