- •Билет №1

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Неинвертирующее включение оу.

- •2. Определение триггера.Rst-триггер.

- •Билет №2

- •1. Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Инвертирующее включение оу.

- •2. Регистры. Параллельные регистры и параллельно-последовательные.

- •Билет №3

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Дифференциальное включение оу.

- •2. Определение триггера. D и dt-триггер.

- •Билет №4

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Дифференциальное включение оу.

- •2. Определение триггера. Счетный триггер. Двоичные счетчики.

- •Билет № 5

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчёта схем. Неинвертирующий сумматор на оу.

- •2. Определение булевой функции. Полные наборы булевых функций.

- •Билет№6

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчёта схем. Схема суммирования и вычитания на оу.

- •2. Определение булевой функции. Булевы функции одной и двух переменных. Теоремы булевой алгебры.

- •Билет №7

- •1. Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Интегратор на оу.

- •Интегратор

- •2. Счетчики. Двоичный счетчик и двоично-десятичный.

- •Билет №8

- •1. Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Дифференциатор на оу.

- •Дифференциатор

- •2. Определение булевой функции. Способы определения булевых функций. Булевы функции одной и двух переменных.

- •Билет №9

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Инвертирующий сумматор на оу.

- •2. Определение триггера. Rs-триггер.

- •Билет №10

- •1. Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Интегратор на оу.

- •Интегратор

- •2. Определение триггера.Rst-триггер на элементах и-не.

- •Билет№11

- •1. Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Пассивные и активные фильтры низкой частоты на оу.

- •2. Определение триггера.Rst-триггер на элементах или-не.

- •Билет № 12

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Активные фильтры высокой частоты на оу.

- •2.Цап, ацп. Определение и примеры использования. Ацп преобразованием а-ткод (амплитудаинтервал временни код)

- •Билет № 13

- •1.Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Источник тока в незаземленную нагрузку на оу.

- •2. Определение комбинационной схемы. Синтез дешифраторов.

- •Билет № 14

- •1. Понятие обратной связи. Идеальный операционный усилитель: свойства и правила расчета схем. Компаратор напряжения на оу.

- •2.Цап, ацп. Определение и примеры использования. Алгоритм работы и структурная схема ацп двойного интегрирования.

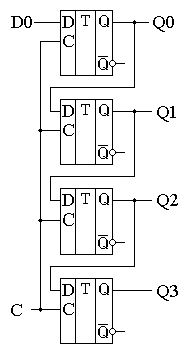

2. Регистры. Параллельные регистры и параллельно-последовательные.

Регистром называется последовательное или параллельное соединение триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические D триггеры, так и статические триггеры.( Регистром называется устройство, осуществляющее прием, хранение преобразование и выдачу чисел в двоичном коде. Информация в регистре хранится в виде числа. Он включает в себя отдельные триггеры, количество которых соответствует числу разрядов двоичного кода и логические элементы. )

Регистры выполняют ряд микроопераций над словами:

1.Прием слова в регистр в прямом и обратном коде, данные хранятся в регистре пока не появится команда на их смену.

2.Выдача слова из регистра в прямом и обратном коде.

3.Выполнение поразрядных логических операций над несколькими словами.

4.Сдвиг кода вправо или влево на требуемое число разрядов, преобразование параллельного кода в последовательный и наоборот.

По способу записи и считывания кода числа в регистре следует различать параллельные и последовательные регистры:

Параллельный регистр. В параллельных регистрах операции записи и считывания информации осуществляются во всех разрядах одновременно. в виде параллельного кода, т.е. все разряда одновременно по n проводам. Таким образом информация в параллельном регистре хранится в параллельном коде, поэтому параллельный регистр называют регистром памяти.

Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. В параллельном регистре цифры кода подаются на D-вход соответствующих триггеров. Запись осуществляется при подаче логической единицы на вход С. Код снимается с выходов Q. Параллельные регистры служат только для хранения информации в виде параллельного двоичного кода и для преобразования прямого кода в обратный и наоборот. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение - на рисунке 2. В параллельном регистре цифры кода подаются на D-вход соответствующих триггеров. Запись осуществляется при подаче логической единицы на вход С. Код снимается с выходов Q. Параллельные регистры служат только для хранения информации в виде параллельного двоичного кода и для преобразования прямого кода в обратный и наоборот.

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем). Последовательные регистры, помимо хранения информации, способны преобразовывать последовательный код в параллельный и наоборот. При построении последовательных регистров триггеры соединяются последовательно путем подключения выхода Q i-го триггера ко входу D i-го триггера

Принципиальная схема последовательного регистра, собранного на основе D‑триггеров и позволяющего осуществить преобразование последовательного кода в параллельный

В параллельно – последовательном регистре запись информации происходит в параллельном коде, а считывание в последовательном

В приведенной схеме JK – триггеры дважды превращены в D – триггеры. Одно превращение осуществлено для организации записи с использованием вспомогательных инверсных входов S и R и, добавлением двух элементов И –НЕ. Этот способ построения триггера показан на рис 1.14.5. Запись числа в регистр в параллельном коде происходит при подаче числа на входы х1, х2, х3 и сигнала «1» на вход «зап». Для считывания информации из регистр в последовательном коде JK – триггеры второй раз превращены в D – триггеры у которых выходы каждого триггера соединены со входом D следующего, как это делается в последовательном регистре. Во втором случае JK – триггеры превращены в D – триггеры способом показанном на рис 1.14.8, но вместо дополнительного инвертора используется инверсный выход предыдущего триггера. Исключение составляет первый триггер, у которого входы J и K объединены и соединены с основным входом этого же триггера. Благодаря такой схеме после подачи импульсов считывания первый триггер оказывается в состоянии «0».