- •4 .Память.

- •4.1 Память. Назначение. Классификация.

- •4.2. Внутренняя память. Классификация. Назначение

- •4.4 Rom. Назначение технологии (Колесниченко гл. 7,9). Bois.

- •1)Bios базовый набор программ для организации ввода-вывода.

- •3)Setup gmos - содержит в себе настройки.

- •4.3. Dram. Организация. Назначение ras, cas. Понятие «тайминга»

- •4.5 Cmos. Назначение. Основные функции (Колесниченко гл.31). Настройки cmos Setup.

- •4.6. Sram. Назначение. Организация. Режим работы.

- •4.7. Логическое распределение оп ( основная, расширенная, дополнительная).

- •4.8. Назначение драйверов emm386. Exe и himm.Sys.

- •5Ввод/ Вывод

- •5.2. Системные ресурсы. Понятие интерфейса. Назначение контролера

- •Шаги которые выполн.Привыполнение прерыв.

- •Приоритеты бывают 2 вида:

- •5.4. Алгоритм выполнения команды int Шаги которые выполн.Привыполнение прерыв.

- •5.5. Контролер прерываний. Структурная схема.

- •5.6 Алгоритм выполнения аппаратных прерываний. Работа контролера 8259.

- •Шаги которые выполн.Привыполнение прерыв.

- •5.7. Dma. Назначение. Структурная схема контролера

- •6.1. Отказоустойчивые системы. Принципы построения.

- •Контроль и диагностика pc. Назначение. Классификация.

- •Система контроля и диагностики

- •6.3. Аппаратные средства контроля. Контроль по чету нечету.

- •6.4.Аппаратные средства контроля. Код Хемминга.

- •6.5. Аппаратные средства контроля. Crt.

- •6.6. Аппаратно-программные средства контроля. Post

Приоритеты бывают 2 вида:

1)Фиксируемый приоритет-(каждое прерывания строго определенный приоритет 0-наивышим 7-низший)

Недостаток-прерывания с наименьшим приоритетом может быть необработаная

2)Циклический приоритет-(приоритет сдвигается после выполнения очередного прерывания)

5.4. Алгоритм выполнения команды int Шаги которые выполн.Привыполнение прерыв.

1)Появления на шине управления сигналов NMI (не маскир),INTK (маскир) для аппаратных.Для программных INT XX

2)В стеке по адресу SS:SP сохраняется текущее состояние процессора (точка возврата)

3)По номеру XX команды INT-XX определяет элемент (адреса 0000.XX.4) таблицы векторов прерывания в котором находится (4б) программы обрабатывающее данное прерывание.

4)Логический адрес программы загруж в регистры процессора CS:IP и начинается выполняется программа обработки прерывания до появления команды RET.

Таблицы векторов прерывания-В. Оп в начале 0400:0000.Адрес элемент прерывания номера умножить 4 (2h*4=8)

5)По команде RETI из стека в по адресу SS:SP в регистры процессора возвращаются прерванной программы ( точка возврата) и продолжает выполнятся основная программа

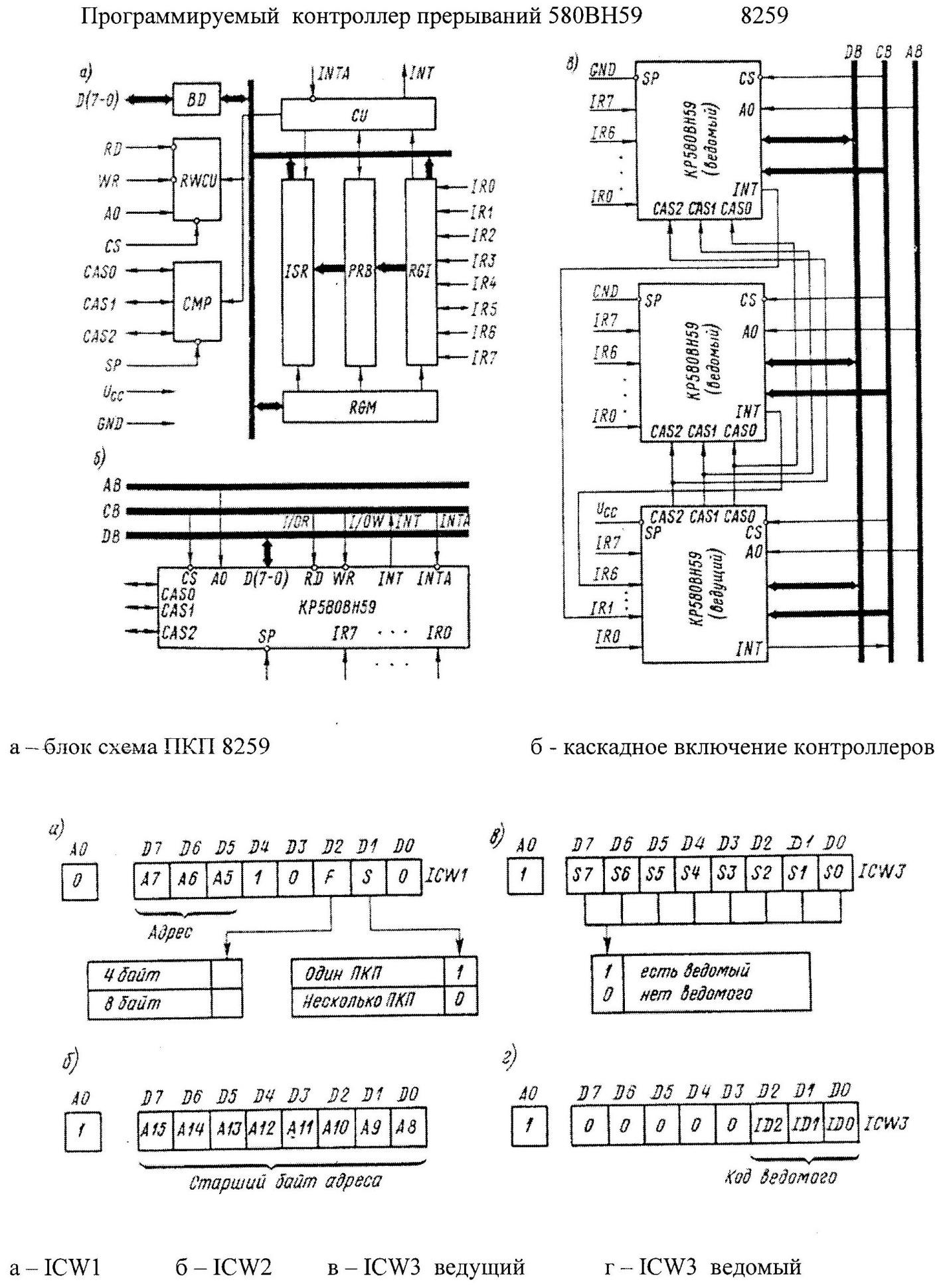

5.5. Контролер прерываний. Структурная схема.

5.6 Алгоритм выполнения аппаратных прерываний. Работа контролера 8259.

Регистр RGI (СОСТАВ 8259) программирования контролера прерывания.

Предназначен для фикс Вход прерывания от контроллеров внешних устройств.

Регистр маски

(8-бит)для хранения маски

0-запрещенно 1-разрешенно

PRB (блок приоритета)-определяет приоритет прерывания.

BD (буфер данных)-согласование микросхемы с общей шиной данных

RWCU (блок управления чтения \записи)

CMP (блок каскадирования)

CU (блок управления) предназначенный для управления микросхемой-8259(уст.сигнал INTR и принимает сигнал INTA)

Программирование контроллера сводится к вводу упр.слов.

1)ICW-номер прерывания

ICW1-каскадирование\не каскадирования и часть номера

ICW2-адрес (номер) прерывания

OCW-задаёт маску данного прерывания

1)Прерывания от контролера внешних устройств поступают на регистр RGI предназначенный для фиксации входящих прерываний.

2)По маске в регистре RGM определяется разрешено данное прерывания или нет.

3)Разрешенные прерывания поступает на блок PRB предназначен для определения прерывания с наивысшим приоритетом.PRB работает в одном из двух режимов фиксированный и цикличный

4)После выбора прерывания с наивысшим приоритетом CU (блок упр.) выставляет сигнал INT который в процессор сигнализируя о поступление прерывания, но которому процессор выполн. Стандартную процедуру сохранения точки возврата после этого процесс выставляет сигнал INTA (подтверждения прерывания по некоторому из регистра TSR выставляется номер прерывания и выполняется стандартная процедура)

5)Оброщается к таблице прерывания и

умножается на 4 из которого берётся

адрес прерывания (4 байта)

2CS 2IP

6)Программа обработки прерываний заканчивается R.E.T.I. и программа удаляется из очереди

Шаги которые выполн.Привыполнение прерыв.

1)Появления на шине управления сигналов NMI (не маскир),INTK (маскир) для аппаратных.Для программных INT XX

2)В стеке по адресу SS:SP сохраняется текущее состояние процессора (точка возврата)

3)По номеру XX команды INT-XX определяет элемент (адреса 0000.XX.4) таблицы векторов прерывания в котором находится (4б) программы обрабатывающее данное прерывание.

4)Логический адрес программы загруж в регистры процессора CS:IP и начинается выполняется программа обработки прерывания до появления команды RET.

Таблицы векторов прерывания-В. Оп в начале 0400:0000.Адрес элемент прерывания номера умножить 4 (2h*4=8)

5)По команде RETI из стека в по адресу SS:SP в регистры процессора возвращаются прерванной программы ( точка возврата) и продолжает выполнятся основная программа