- •Серия «учебники и учебные пособия» Эрл д. Гейтс введение в электронику

- •Раздел 1 за 34

- •Глава 2 36

- •Техника безопасности

- •Меры предосторожности при работе с высоким напряжением

- •Раздел 1.

- •Глава 1. Основы электричества

- •3. Вопросы

- •4. Напряжение

- •4. Вопросы

- •5. Сопротивление

- •5. Вопросы

- •Глава 1. Самопроверка

- •Глава 2. Ток

- •1. Электрический заряд

- •V у заряд

- •1. Вопросы

- •2. Протекание тока

- •Шарики от л -

- •Пинг-понга V

- •Электронов.

- •3. Степенное представление чисел

- •Раздел 1 за

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 2

- •Глава 2. Самопроверка

- •Глава 3. Напряжение

- •2. Элементы и батареи

- •4. Приложенное напряжение и падение напряжения

- •4. Вопросы

- •5. Заземление как уровень отсчета напряжения

- •5. Вопросы

- •Глава 3. Самопроверка

- •Глава 4. Сопротивление

- •1. Сопротивления

- •6. Вопрос

- •Глава 4. Самопроверка

- •2. Вопросы

- •93 Глава 5 . Шь

- •Глава 5. Самопроверка

- •Глава 6. Электрические измерения - измерительные приборы

- •6. Отсчет показаний измерительного прибора

- •7. Вопросы

- •Глава 6. Самопроверка

- •1. Вопросы

- •2. Применение мощности (анализ цепей)

- •Раздел 1 за 34

- •Глава 2 36

- •2. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 7. Самопроверка

- •2. Параллельные цепи

- •3. Вопрос

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 8. Самопроверка

- •1. Вопросы

- •2. Вопросы

- •3. Вопросы

- •4. Применения магнетизма и электромагнетизма

- •157 Глава 9

- •4. Вопросы

- •Глава 9. Самопроверка

- •1. Вопросы

- •2. Катушки индуктивности

- •2. Вопросы

- •3. Постоянная времени l/r

- •3. Вопросы

- •Глава 10. Самопроверка

- •1. Вопросы

- •2. Конденсаторы

- •2. Вопросы

- •3. Вопросы

- •Глава 11. Самопроверка

- •Специальность — электрик

- •1. Получение переменного тока

- •Раздел 1 за 34

- •Глава 2 36

- •3. Вопросы

- •Глава 12. Самопроверка

- •1. Вопросы

- •2. Осциллографы

- •2. Вопросы

- •3. Частотомеры

- •3. Вопросы

- •Глава 13. Самопроверка

- •Раздел 1 за 34

- •Глава 2 36

- •3. Параллельные цепи переменного тока

- •4. Вопросы

- •Глава 14. Самопроверка

- •Раздел 1 за 34

- •Глава 2 36

- •2. Вопросы

- •Глава 15. Самопроверка

- •180 Градусов.

- •1. Вопросы

- •2. Вопросы

- •Глава 16. Самопроверка

- •1. Реактивное сопротивление

- •X 1114 Ом (индуктивное).

- •1. Вопросы

- •2. Вопросы

- •4. Вопрос

- •Глава 17. Самопроверка

- •Глава 18. Трансформаторы

- •1. Вопросы

- •3. Коэффициент трансформации

- •3. Вопросы

- •4. Вопросы

- •Глава 18. Самопроверка

- •Специальность — техник по электронике

- •Глава 19. Основы полупроводников

- •1. Полупроводниковые свойства германия и кремния

- •14 Электронов на орбитах

- •1. Вопросы

- •2. Вопросы

- •3. Проводимость в легированном германии и кремнии

- •3. Вопросы

- •Глава 19. Самопроверка

- •Глава 20. Диоды на основе р-n перехода

- •1. Вопросы

- •2. Смещение диода

- •3. Вопросы

- •5. Вопросы

- •Глава 20. Самопроверка

- •Глава 2 1 Як _________

- •Глава 21. Самопроверка

- •2. Вопросы

- •3. Основы работы транзистора

- •Щенный п-р-п транзистор. Щенный р-п-р транзистор.

- •4. Проверка транзисторов

- •5. Замена транзисторов

- •5. Вопросы

- •Глава 22. Самопроверка

- •1. Вопросы

- •2. Полевые транзисторы с изолированным затвором обедненного типа

- •I Подложка (п)

- •4. Вопросы

- •5. Проверка полевых транзисторов

- •5. Вопросы

- •Раздел 3

- •Глава 23. Самопроверка

- •120 Вольт

- •1. Вопросы

- •I, Управляющий электрод Рис. 24-10. Упрощенная схема конструкции триака.

- •1 120 В диак триак

- •Глава 24. Самопроверка

- •1. Введение в интегральные микросхемы

- •Шлифовка и полировка Установка для эпитаксиального

- •3. Корпуса интегральных микросхем

- •Глава 25. Самопроверка

- •3. Светоизлучающие устройства

- •Глава 26. Самопроверка

- •2. Вопросы

- •4. Вопросы

- •5. Умножители напряжения

- •5. Вопросы

- •6. Устройства защиты цепей

- •Глава 27. Самопроверка

- •Глава 28 Як

- •6. Вопросы

- •I j частоты

- •7. Вопросы

- •Выход Рис. 28-42. Блок-схема операционного усилителя.

- •8. Вопросы

- •Глава 28. Самопроверка

- •1. Основы генераторов

- •1. Вопросы

- •2. Генераторы синусоидальных колебаний

- •2. Вопросы

- •3. Генераторы несинусоидальных колебаний

- •3. Вопросы

- •Глава 29. Самопроверка

- •Глава 30. Цепи формирования сигнала

- •2. Цепи формирования сигнала

- •Диодныи ограничитель со смещением.

- •Перемене полярности диода и источника смещения в смещенном последовательном диодном ограничителе.

- •2. Вопросы

- •3. Цепи специального назначения

- •Глава 30. Самопроверка

- •Цифровые электронные цепи

- •2. Преобразование двоичных чисел в десятичные и наоборот

- •Раздел 1 за 34

- •Глава 2 36

- •2. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Раздел 1 за 34

- •Глава 2 36

- •3. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 31. Самопроверка

- •3. Вопросы

- •4. Элемент не-и

- •4. Вопросы

- •5. Элемент не-или

- •5. Вопросы

- •6. Элементы исключающее или и исключающее не-или

- •6. Вопросы

- •Гпава 32. Самопроверка

- •Глава 33. Простые логические цепи

- •1. Вопросы

- •Глава 33. Самопроверка

- •Глава 34. Последовательные логические цепи

- •1. Триггеры

- •2. Счетчики

- •2. Вопросы

- •0 0 0 0 Потеря данных

- •3. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 34. Самопроверка

- •4. Вопросы

- •Глава 35. Самопроверка

- •1. Основы устройства компьютера

- •В память или ввод/вывод

- •Выбор ячейки памяти

- •1. Вопросы

- •2. Архитектура микропроцессора

- •Дешифратор команд

- •Манд • Указатель

- •2. Вопросы

- •Глава 36. Самопроверка

- •IPjNlPj”

- •Глава 1. Основы электричества

- •Глава 3. Напряжение

- •Глава 4. Сопротивление

- •Глава 5. Закон ома

- •Глава 6. Электрические измерения — измерительные приборы

- •Глава 7. Мощность

- •Глава 8. Цепи постоянного тока

- •Глава 9. Магнетизм

- •Глава 10. Индуктивность

- •Глава 11. Емкость

- •Глава 12. Переменный ток

- •Глава 13. Измерения переменного тока

- •Глава 14. Резистивные цепи переменного тока

- •Глава 15. Емкостные цепи

- •Глава 1c. Индуктивные цепи переменного тока

- •Глава 17. Резонансные цепи

- •Глава 18. Трансформаторы

- •Глава 19. Основы полупроводников

- •Глава 20. Диоды на основе р-п-перехода

- •Глава 21. Стабилитроны

- •Глава 22. Биполярные транзисторы

- •Глава 23. Полевые транзисторы

- •Глава 24. Тиристоры

- •Глава 25. Интегральные микросхемы

- •Глава 26. Оптоэлектронные устройства

- •Глава 27. Источники питания

- •Глава 28. Усилители

- •Глава 29. Генераторы

- •Глава 30. Цепи формирования сигнала

- •Глава 31. Двоичная система счисления

- •Глава 32. Основные логические элементы

- •Глава 33. Простые логические цепи

- •Глава 34. Последовательные логические цепи

- •Глава 35. Комбинационные логические схемы

- •Глава 36. Основы микрокомпьютеров

- •344007, Г. Ростов-на-Дону, пер. Соборный, 17 Тел.: (8632) 62-51-94

- •3. Вопросы

- •5. Вопросы

- •6. Вопросы

- •7. Мультиметры

- •1. Вопросы

- •2. Вопросы

- •2. Вопросы

- •2. Последовательные цепи переменного тока

- •1. Вопросы

- •2. Вопросы

- •4. Меры предосторожности при работе с моп транзисторами

- •2. Вопросы

- •3. Двунаправленные диодные тиристоры

- •3. Вопросы

- •4. Проверка тиристоров

- •4. Вопросы

- •1. Вопросы

- •3. Вопросы

- •1. Вопросы

- •2. Светочувствительные устройства

- •3. Вопросы

- •3. Вопросы

- •4. Регуляторы и стабилизаторы напряжения

- •1. Вопросы

- •3. Вопросы

- •4. Арифметические схемы Сумматор

- •I3. Вопросы

- •4. Цепи rlc

Раздел 1 за 34

Глава 2 36

Г 109

t* 85

R 85

Г 93

Е„ 107

' 0 / % 165

,Л. 201

Г? 347

га 364

-

Триггеры используются в цифровых цепях в качестве счетчиков.

-

Защелка — это временный буфер памяти.

-

Счетчик — это логическая цепь, которая может считать последовательность чисел или состояний.

-

Один триггер может сосчитать последовательность из двух чисел, 0 и 1.

-

Максимальное число двоичных состояний счетчика может зависеть от количества триггеров, содержащихся в счетчике.

-

Счетчики могут быть либо синхронными, либо асинхронными.

-

Асинхронные счетчики называют счетчиками пульсаций.

-

Синхронные счетчики тактируют все каскады одновременно.

-

Сдвиговые регистры используются для временного хранения данных.

-

Сдвиговые регистры состоят из соединенных вместе триггеров.

-

Сдвиговые регистры могут перемещать данные влево или вправо.

-

Сдвиговые регистры используются для преобразования данных из последовательной формы представления в параллельную, и наоборот.

-

Сдвиговые регистры могут выполнять умножение и деление.

Глава 34. Самопроверка

-

Опишите, как RS-триггер изменяет состояния с высокого на выходе Q на высокое на выходе Q .

-

В чем главное отличие D-триггера от тактируемого RS- триггера?

-

Из каких компонентов состоит счетчик, и как он сконструирован?

-

Нарисуйте схему счетчика, который считает до 10 и после этого повторяет счет.

-

Чем сдвиговый регистр отличается от счетчика?

-

Какие функции выполняет и для чего может использоваться сдвиговый регистр?

ЦЕЛИ

После изучения этой главы студент должен быть в состоянии:

-

Описать функции шифраторов, дешифраторов, мультиплексоров, сумматоров, вычитающих устройств и компараторов.

-

Различать схематические обозначения шифраторов, дешифраторов, мультиплексоров, сумматоров, вычитающих устройств и компараторов.

-

Перечислить применения комбинационных логических схем.

-

Начертить таблицы истинности для различных комбинационных логических схем.

Комбинационные логические схемы — это схемы, состоящие из комбинаций элементов И, ИЛИ, инверторов и образующие более сложные схемы. Выход комбинационных логических схем является функцией состояний их входов, типов использованных элементов и их соединений между собой. Наиболее часто встречающимися комбинационными логическими схемами являются шифраторы, дешифраторы, мультиплексоры и арифметические схемы.

35-1. ШИФРАТОРЫ

Шифратор — это комбинационная логическая схема, имеющая один или более входов и создающая многоразрядный двоичный выход. Шифрование — это процесс преобразования любого символа клавиатуры или числа, поданного на вход в кодированный выход в двоичном или дво- ично-десятичном коде.

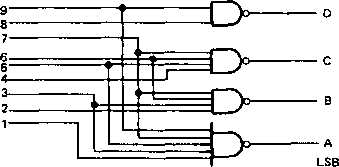

На рис. 35-1 изображен десятично-двоичный шифратор, называемый шифратором на «4». Его функция состоит в

Рис.

35-1. Десятичнодвоичный шифратор.

Рис.

35-3. Логическое обозначение

десятично-двоичного шифратора с

приоритетом.

преобразовании отдельной цифры (от 0 до 9), поданной на вход, в четырехразрядный двоичный код на выходе. Это означает, что если на клавиатуре нажата цифра 4, то на вход 4 будет подан высокий уровень, или 1, а на выходе появится 4-разрядный код 0100.

На рис. 35-2 изображен десятично-двоичный приоритетный шифратор. Функция приоритета означает, что если две клавиши нажаты одновременно, то шифратор выдаст дво- ично-десятичный код, соответствующий большей десятичной цифре. Например, если на шифратор подать одновременно цифры 2 и 5, то он выдаст двоично-десятичный код 0101, соответствующий цифре 5. Шифраторы этого типа встроены в одну интегральную микросхему и состоят примерно из 30 логических элементов. На рис. 35-3 изображено логическое обозначение шифратора с приоритетом.

Шифраторы этого типа используются для преобразования десятичных чисел с клавиатуры в двоично-десятичный код 8421. Десятично-двоичный шифратор и десятичнодвоичный приоритетный шифратор всегда можно найти там, где есть ввод с клавиатуры. Это калькуляторы, клавиатуры компьютеров, электронные пишущие машинки и телетайпы.

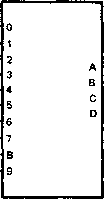

Например, он может дешифровать число в двоично-деся- тичном коде в одну из десяти возможных десятичных цифр. Выход такого дешифратора используется для работы цифрового отсчета или дисплея. Дешифратор этого типа называется дешифратор 1на 10 или дешифратор 4 линии- на-10-линий.

Рис.

35-5. Логическое обозначение двоично-де-

сятичного дешифратора.

ч>°-

ч>-

—^о—

ч>-

ч>°-

Рис. 35-4 Двоично-десятичный дешифратор.

На рис. 35-4 изображены десять элементов НЕ-И, требующихся для дешифрации 4-разрядного числа в двоичнодесятичном коде в десятичную цифру. Когда на всех входах элемента НЕ-И высокий уровень, на его выходе 0. На всех других выходах элементов НЕ-И дешифратора — высокие уровни. Для того, чтобы каждый раз не рисовать все логические элементы цепи, используется обозначение, показанное на рис. 35-5.

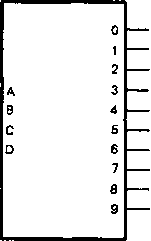

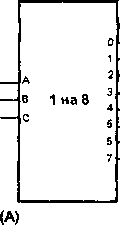

Два других типа дешифраторов — это дешифратор с восемью выходами и дешифратор с шестнадцатью выходами (рис. 35-6). Дешифратор с восемью выходами преобразует входное трехразрядное слово в напряжение на одном

Рис. 35-6. Логические обозначения дешифраторов 1 на 8 (А) и 1 на 16 (Б).

0

2

3

4

—

А

5

В

6

с

1на16 ^

в

о

9

то

и

12

13

14

Т5

(Б)

из

восьми выходов. Дешифратор с шестнадцатью

выходами преобразует входное

четырехразрядное слово в напряжение

на одном из шестнадцати выходов. Его

также называют дешифратор 4

линии-на-10-линий.

из

восьми выходов. Дешифратор с шестнадцатью

выходами преобразует входное

четырехразрядное слово в напряжение

на одном из шестнадцати выходов. Его

также называют дешифратор 4

линии-на-10-линий.

Рис.

35-7. Конфигурация семисегментного

индикатора.

Ill

I

J

It

II

Рис. 35-8. Использование семисегментного индикатора для отображения десятичных цифр.

■v

—и-

4*-

ь о-

d О-

-х—-*ь-

-V

ч*.

—н-

—м- —м-

-н—

f

о-

~^г

-W—

Рис. 35-9. Два различных типа светодиодных индикаторов.

Работа каждого из этих индикаторов основана на одном принципе. Сегмент активируется либо высоким, либо низким уровнем напряжения. На рис. 35-9 изображены два типа светодиодных индикаторов: с общим анодом и с общим катодом. В каждом случае светодиодный сегмент должен быть смещен в прямом направлении для того, чтобы

d.p.

о-

■tffO

щу

Рис.

35-10. Дешифратор двоичного кода в код

семисегментного индикатора.

он излучал свет. В случае с общим катодом, при высоком уровне (1) сегмент светится, а при низком (0) — нет.

а

b

—

—

А

с

—

—

В

d

Р

й

—

—

и

в D

f

9

—

d.p.

Рис.

35-11. Логическое обозначение дешифратора

двоич- но-десятичного кода в код

семисегментного индикатора.

-

8 и 9 и т. д. Для определения логической схемы, необходимой для зажигания каждого сегмента дисплея, могут быть записаны выражения Булевых функций. Логическое обозначение дешифратора двоично-десятично- го кода в код семисегментного индикатора изображено на рис. 35-11, — это цепь, содержащая в интегральной микросхеме.

-О

О

-о

■о![]()

Механическое переключение не может удовлетворительно выполнить эту задачу. Следовательно, мультиплексоры, используемые для выполнения высокоскоростного переключения, должны состоять из электронных компонентов.

Мультиплексоры имеют дело с данными двух типов: аналоговыми и цифровыми. Мультиплексоры для аналоговых сигналов состоят из реле и транзисторных ключей. Мультиплексоры для цифровых сигналов состоят из стандартных логических элементов.

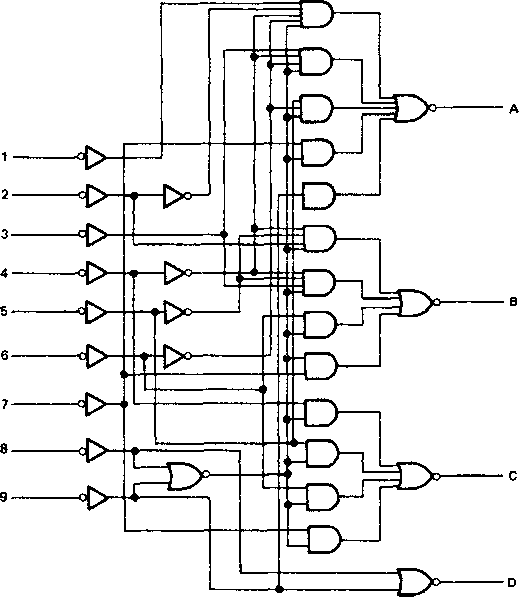

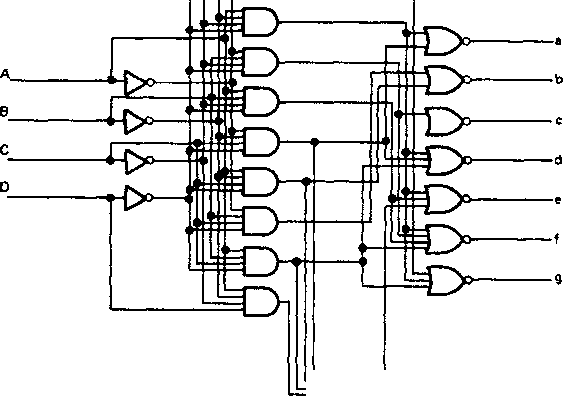

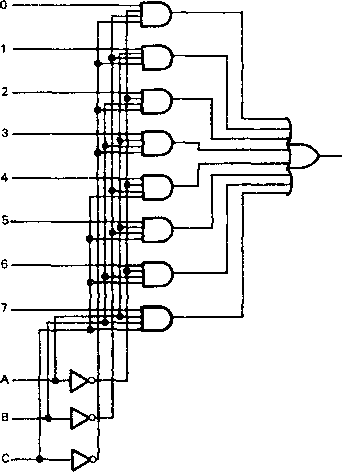

Цифровые мультиплексоры позволяют направлять цифровые данные от отдельных источников в общую линию для передачи по назначению. Типичный мультиплексор имеет несколько входов и один выход. Входы мультиплексора активируются входом выбора данных, определяющих вход, по которому данные будут приниматься. На рис. 35-13 изображена логическая схема восьмивходового мультиплексора. Заметим, что мультиплексор имеет три линии управления входами, обозначенные А, В и С. Путем подачи соответствующего двоичного кода на линии управления, может быть выбран любой из восьми входов. Обозначение цифрового мультиплексора показано на рис. 35-14.

На рис. 35-15 изображено обозначение 16-входового мультиплексора. Заметим, что мультиплексор имеет четыре линии управления для активации шестнадцати входов данных.

Кроме селекции потоков данных, мультиплексоры широко используются для преобразования данных из параллельного кода в последовательный. Двоичное слово, представленное параллельным кодом, подается на вход мультиплексора, Подавая на управляющие входы последовательность разрешающих кодов, можно получить на выходе

|

0 |

|

|

|

2 |

|

|

|

3 |

|

|

|

4 |

|

|

|

5 |

|

|

|

6 |

|

|

|

7 |

|

|

|

8 |

|

|

|

9 |

1 на 16 |

Y |

|

to |

|

|

|

11 |

|

|

|

12 |

|

|

|

13 |

|

|

|

14 |

|

|

|

15 |

|

|

|

|

А В С D |

|

Рис.

35-13. Логическая схема восьмивходового

мультиплексора.

Рис.

35-16. Использование мульти- Рис. 35-14.

Логическое плексора для преобразования

дан-

обозначение

восьмивхо- ных, представленных параллель-

дового

мультиплексора. ным кодом, в

последовательный.

![]()

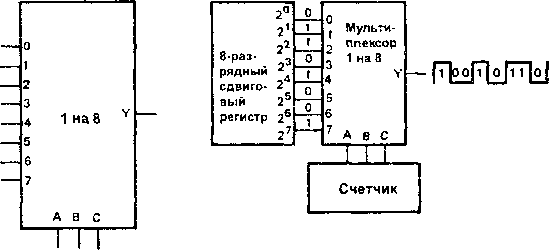

последовательное представление параллельного двоичного слова, поданного на вход.

На рис. 35-16 изображена схема преобразования данных из параллельного кода в последовательный с помощью мультиплексора. Трехразрядное двоичное слово со счетчика используется для выбора нужного входа. Параллельное восьмиразрядное слово подается на вход мультиплексора. При увеличении двоичного числа на выходе счетчика последовательно выбираются входы мультиплексора. На выходе мультиплексора появляется последовательное двоичное слово, равное параллельному, поданному на вход.

О

0 1 +0 +1 +0

1

+1

На рис. 35-17 изображена таблица истинности, основанная на этих правилах. Заметим, что греческая буква сигма (I) используется для обозначения суммы столбца. Столбец переноса обозначен С0. Эти обозначения используются в промышленности при описании сумматора.

Входы

Выходы

А

в

2

С„

0

0

0

0

1

0

1

0

0

1

1

0

1

1

0

1

Рис.

35-17. Таблица истинности, составленная

с помощью правил сложения.

А

в

Y

0

0

0

1

0

0

0

1

0

1

1

1

Рис.

35-19. Таблица истинности для элемента

И.

А

в

Y

0

0

0

1

0

1

0

1

1

1

1

0

Рис.

35-18. Таблица истинности для элемента

исключающее ИЛИ.

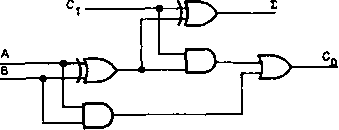

Рис. 35-20. Схема полусумматора.

о-

Сумматор, учитывающий перенос, называется полным сумматором. Полный сумматор имеет три входа и выходы для суммы и переноса. На рис. 35-21 приведена таблица истинности для полного сумматора. Вход Сх — это вход переноса. Выход С0 — это выход переноса.

Входы

Выходы

А

в

С,

X

С„

0

0

0

0

0

1

0

0

1

0

0

1

0

1

0

1

1

0

0

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

1

1

1

1

1

1

Рис.

35-21. Таблица истинности для полного

сумматора,

Отдельный полный сумматор способен сложить два одноразрядных числа и вход переноса. Для сложения двоичных чисел, имеющих более одного разряда, необходимо использовать дополнительные сумматоры. Вспомним, что

Рис.

35-22. Логическая схема полного

сумматора, использующая два

полусумматора.

Рис.

35-23. Логические обозначения

полусумматора (А) и полного сумматора

(Б).

А

Г

С1

г

НА

—

A

FA

(А)

В

с0

—

(Б)“

В

с0

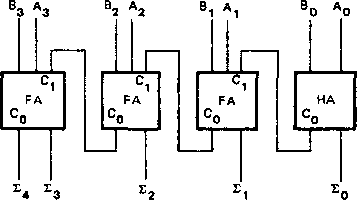

На

рис. 35-24 изображен 4-разрядный параллельный

сумматор. Входные биты младшего разряда

обозначены А0

и BQ.

Биты

следующего разряда обозначены Ах

и Вх

и т. д. Биты выходной суммы обозначены

XQ,

Ei;

12

и т.д. Заметим, что выход переноса

каждого сумматора соединен со входом

переноса сумматора следующего разряда.

Выход переноса последнего сумматора

является старшим разрядом результата.

На

рис. 35-24 изображен 4-разрядный параллельный

сумматор. Входные биты младшего разряда

обозначены А0

и BQ.

Биты

следующего разряда обозначены Ах

и Вх

и т. д. Биты выходной суммы обозначены

XQ,

Ei;

12

и т.д. Заметим, что выход переноса

каждого сумматора соединен со входом

переноса сумматора следующего разряда.

Выход переноса последнего сумматора

является старшим разрядом результата.

Рис. 35-24. Четырехразрядный параллельный сумматор.

Вычитающее устройство

Вычитающее устройство позволяет вычитать два двоичных числа. Для того чтобы, понять, как работает вычитающее устройство, необходимо вспомнить правила вычитания.

О Заем 10 1 1 -О -1 -0 -1

О I Т О

На рис. 35-25 приведена таблица истинности, основанная на этих правилах. Буква D обозначает столбец разности. Столбец заема обозначен буквой В0.

Входы

Выходы

А

В

D

Во

0

0

0

0

1

0

1

0

0

1

1

1

1

1

0

0

Рис.

35-25. Таблица истинности, составленная

с помощью правил вычитания.

Следовательно, разность может быть выражена как исключающее ИЛИ входных переменных.

Заем выхода появляется только тогда, когда на А подан 0, а на В подана 1. Следовательно, выход заема является дополнительным к элементу А ИЛИ В.

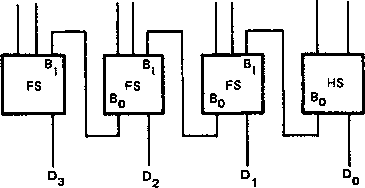

На рис. 35-26 изображена логическая схема полувычи- тателя. Она имеет два входа и выдает разность и выход заема. Разность создается элементом исключающее ИЛИ, а выход заема создается элементом И со входами А и В. Вход А получен путем включения инвертора перед входом А элемента И.

Рис. 35-26. Логическая схема полувычитателя.

—О 0 ^

Однако полувычитатель не имеет входа заема. Вход заема имеет полный вычитатель. Он имеет три входа и создает разность и выход заема. Логическая схема и таблица истинности полного вычитателя изображены на рис. 35-27. На рис. 35-28 изображены обозначения полувычитателя и полного вычитателя.

Рис.

35-27. Логическая схема (А) и таблица

истинности (Б) для полного вычитателя.

Входы

Выходы

А

в

В,

D

Во

0

0

0

0

0

1

0

0

1

0

0

1

0

1

1

1

1

0

0

0

0

0

1

1

1

1

0

1

0

0

0

1

1

0

1

1

1

1

1

1

(Б)

Рис.

35-28. Логические обозначения

полувычитателя (А) и полного вычитателя

(Б).

A

D

—

—

В1

D

—

HS

—

A

FS

В

В0

—

(Б)

В

в0

-

(А)

На рис. 35-29 изображена блок-схема 4-разрядного вычитателя. В младшем разряде используется полувычита- тель, поскольку там не нужен вход заема.

S9A0 B«Ai Bn А0

Рис.

35-29. Четырехразрядный вычитатель.

Компаратор

Компаратор используется для сравнения величин двух двоичных чисел. Схема определяет, равны два числа или нет. Компаратор не только сравнивает два двоичных числа, но также определяет какое из них больше, а какое меньше.

Вход

Выход

А

в

Y

0

0

1

1

0

0

0

1

0

1

1

1

Рис.

35-30. Таблица истинности для компаратора.

Когда оба сравниваемых бита одинаковы на выходе компаратора появляется высокий уровень. Столбец выхода представляет собой выход элемента исключающее ИЛИ с инверсией, также известное, как исключающее ИЛИ-НЕ. Элемент исключающее ИЛИ-НЕ по существу является компаратором, так как на его выходе появляется 1 только тогда, когда на оба входа поданы 1. Для сравнения чисел, имеющих 2 разряда и более необходимы дополнительные элементы исключающее ИЛИ-НЕ. На рис.

-

31 изображена логическая схема компаратора для сравнения двух 2-разрядных чисел. Если числа равны, на выходе элемента исключающее ИЛИ-НЕ появляется 1. Эта 1 подается на элемент И, как указательный уровень. Если оба элемента исключающее ИЛИ-НЕ выдают 1 на входы элемента И, то, следовательно, числа равны, и на выходе элемента И также появляется 1. Если же на входах элемента исключающее ИЛИ-НЕ различные уровни, то элемент исключающее ИЛИ-НЕ выдает на выходе 0, и на входе элемента И также будет 0. На рис. 35-32 изображена логическая схема компаратора для сравнения двух

*0.

Во

:£>

![]()

£>

I"

—''

I

Раздел 5 =й>-

А

< В

А

= В

А

> В

Рис.

35-33. Обозначение 4-разрядного компаратора.

А

= В

Рис. 35-32. Сравнение двух 4-разрядных чисел.

4-разрядных чисел. На рис. 35-33 показано обозначение 4-разрядного компаратора.