- •Системы автоматического управления (сау)

- •Карты карно

- •Сумматоры

- •Системы обработки информации

- •Шифраторы и кодеры

- •Сравнительная оценка цифровых и аналоговых устройствмикроэлектронной техники

- •Достоинства технических средств цифровой техники

- •Возможность проектирования формальными логическими методами, что позволяет сокращать сроки проектирования дискр цифр устройств

- •Мультиплексоры Демультиплексоры

- •Классификация микроэлектронных устройств.

- •Компараторы

- •Классификация интегральных схем (плис)

Классификация микроэлектронных устройств.

Микроэлектроника - основное направление электроники, которое изучает проблемы конструирования, исследования, создания и применения электронных устройств с высокой степенью функциональной и конструктивнойинтеграции.

Микроэлектронное изделие, реализованное средствами интегральной технологии и выполняющее определённую функцию по преобразованию и обработке сигналов, называется интегральной микросхемой (ИМС).

Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения.

Всё многообразие микроэлектронных устройств (МЭУ) можно классифицировать по различным признакам:

-

·по принципу и характеру действия:

Цифровые(АЛУ, лог. Элементы,цифр. Шифраторы и дешифраторы, Арифметико-логические устройства, Цифровые компараторы, коммутаторы дискретных сигналов, регистры)

аналоговые(ЗУ, усилители, счетчики, Модуляторы и демодуляторы, фильтры, смесители и генераторы гармонических колебаний)

-

·по функциональному назначению и выполняемым функциям:

В зависимости от количества реализуемых функций различают однофункциональные (простые) и многофункциональные (сложные) МЭУ. В многофункциональных устройствах функции могут выполняться одновременно либо последовательно во времени. В зависимости от этого, в первом случае, устройства называют устройствами «параллельного» действия, а во втором случае - устройствами последовательного действия

-

·по технологии изготовления:

Полупроводниковые;Плёночные; Гибридные.

-

по области применения:

-

по конструктивному исполнению и техническим характеристикам:

простые микросхемы (ИМС); микросборки; микроблоки.

В качестве классификационных технических характеристик обычно используются потребляемая мощность (одной микросхемой) и быстродействие.

По потребляемой мощности все ИМС можно разделить на:

а) микромощные (менее 10 мВт);

б) маломощные (не более 100 мВт);

в) средней мощности (до 500 мВт) и г) мощные (более или = 0,5 Вт).

По быстродействию (максимальным задержкам времени распространения сигналов через ИС) микросхемы делятся условно на:

а) сверхбыстродействующие с граничной частотой fгр переключений свыше 100 МГц;

б) быстродействующие (fгрот 50 МГц до 100 МГц);

в) нормального быстродействия (fгр от 10 МГц до 50 МГц).

Компараторы

Цифровой компаратор или компаратор амплитуд является электронным устройством берущим два числа в двоичном виде и определяющим является ли первое число меньшим, большим или равным второму числу. Рассмотрим два 4-х битных числа A A = A3A2A1A0 и B = B3B2B1B0

Так как числа являются двоичными, то цифры являются или 0 или 1. Булева функция для равенства любых двух цифр Ai и Bi может быть выражена как

![]() .

.

xi равна 1только еслиAi и Bi равны.

Неравенство (неэквивалентность)

Чтобы определить наибольшее из двух двоичных чисел, мы рассмотрим отношение величин пар значащих цифр, начиная с наиболее значащих битов, последовательно продвигаясь к младшим значащим битам до нахождения неравенства. Если соответствующий бит A равен 1 и такой же бит B равен 0, то мы считаем, что A>B.Это последовательное сравнение может быть выражено логически как:

![]()

![]()

Действие однобитного цифрового компаратора может быть выражено таблицей истинности: (далее двухцифрового)

|

Входы |

Выходы |

||||||||||

|

A |

B |

A<B |

A = B |

A>B |

|||||||

|

0 |

0 |

0 |

1 |

0 |

|||||||

|

0 |

1 |

1 |

0 |

0 |

|||||||

|

1 |

0 |

0 |

0 |

1 |

|||||||

|

1 |

1 |

0 |

1 |

0 |

|||||||

|

Входы |

Выходы |

||||||||||

|

A1 |

A0 |

B1 |

B0 |

A<B |

A = B |

A>B |

|||||

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|||||

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|||||

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|||||

|

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|||||

|

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|||||

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|||||

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|||||

|

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|||||

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|||||

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|||||

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|||||

|

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|||||

|

1 |

1 |

0 |

0 |

0 |

0 |

1 |

|||||

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|||||

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|||||

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|||||

RS – триггеры.

RS-триггер получил название по названию своих входов. Вход S (Set – установить англ.) позволяет устанавливать выход триггера Q в единичное состояние. Вход R (Reset – сбросить англ.) позволяет сбрасывать выход триггера Q (Quit – выход англ.) в нулевое состояние.

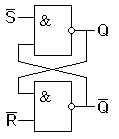

Для реализации RS-триггера воспользуемся логическими элементами “2И-НЕ”. Его принципиальная схема приведена на рисунке 2.

<- Схема простейшего триггера на схемах "И". Входы R и S инверсные (активный уровень'0').

Рассмотрим работу изображенной на рисунке 2 схемы подробнее. Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента “2И-НЕ” Q присутствует логический ноль, то на выходе нижнего логического элемента “2И-НЕ” появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента “2И-НЕ” Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента “2И-НЕ” появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS-триггера работает точно так же как и схема на инверторах.

Подадим на вход S нулевой потенциал. Согласно таблице истинности логического элемента “И-НЕ” на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу.

Точно так же можно записать в триггер и логический ноль. Для этого следует воспользоваться входом R. Так как активный уровень на входах оказался нулевым, то эти входы - инверсные. Составим таблицу истинности RS-триггера. Входы R и S в этой таблице будем использовать прямые, то есть запись нуля, и запись единицы будут осуществляться единичными потенциалами (таблица 1). Таблица истинности RS.

|

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

0 |

0 |

0 |

Режим хранения информации R=S=0 |

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

* |

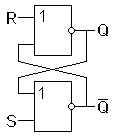

RS-триггер можно построить и на логических элементах "ИЛИ". Схема RS-триггера, построенного на логических элементах "ИЛИ" приведена на рисунке 3. Единственное отличие в работе этой схемы будет заключаться в том, что сброс и установка триггера будет производиться единичными логическими уровнями. Эти особенности связаны с принципами работы инверсной логики, которые рассматривались ранее.

Рисунок 3. Схема простейшего триггера на схемах "ИЛИ". Входы R и S прямые (активный уровень '1').

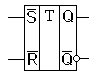

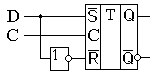

Так как RS-триггер при построении его на логических элементах “И” и “ИЛИ” работает одинаково, то его изображение на принципиальных схемах тоже одинаково. Условно-графическое изображение RS-триггера на принципиальных схемах приведено на рисунке 4.

Рисунок 4. Условно-графическое обозначение RS-триггера.

Синхронные RS-триггеры.

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется опасные гонки), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RS-триггер и триггер Шмитта) эти триггеры получили название асинхронных.

Формировать синхронизирующие сигналы с различной частотой и скважностью при помощи генераторов и одновибраторов мы уже научились в предыдущих главах. Теперь научимся записывать в триггеры входные логические сигналы только при наличии разрешающего сигнала.

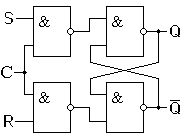

Для этого нам потребуется схема, пропускающая входные сигналы только при наличии синхронизирующего сигнала. Такую схему мы уже использовали при построении схем мультиплексоров и демультиплексоров. Это логический элемент “И”. Триггеры, записывающие сигналы только при наличии синхронизирующего сигнала называются синхронными. Принципиальная схема синхронного RS-триггера приведена на рисунке 5.

Для таких цифровых схем требуются синхронные триггеры. Схема синхронного триггера приведена на рисунке 4, а обозначение на принципиальных схемах на рисунке 5.

Рисунок 5. Схема синхронного RS-триггера, построенного на элементах "И".

В таблице 2 приведена таблица истинности синхронного RS-триггера. В этой таблице символ x означает, что значения логических уровней на данном входе не важны. Они не влияют на работу триггера.

Таблица 2. Таблица истинности синхронного RS-триггера.

|

С |

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

x |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

1 |

* |

Как мы уже показали в предыдущей главе, RS-триггеры могут быть реализованы на различных элементах. При этом логика их работы не изменяется.

ПЛИС

Программируемые логические интегральные схемы – ПЛИС являются одними из самых перспективных элементов цифровой схемотехники. ПЛИС представляет собой кристалл, на котором расположено большое количество простых логических элементов. Изначально эти элементы не соединены между собой. Соединение элементов (превращение разрозненных элементов в электрическую схему) осуществляется с помощью электронных ключей, расположенных в этом же кристалле. Электронные ключи управляются специальной памятью, в ячейки которой заносится код конфигурации цифровой схемы. Таким образом, записав в память ПЛИС определенные коды, можно собрать цифровое устройство любой степени сложности (это зависит от количества элементов на кристалле и параметров ПЛИС). В отличие от микропроцессоров, в ПЛИС можно организовать алгоритмы цифровой обработки на аппаратном (схемном) уровне. При этом быстродействие цифровой обработки резко возрастает.

Отличительными системными особенностями являются:

-

внутренние буфера с возможностью переключения в высокоомное состояние и тем самым позволяющие организовать системные двунаправленные шины

-

индивидуальный контроль высокоомного состояния и времени нарастания фронта выходного сигнала по каждому внешнему выводу

-

наличие общего сброса/установки всех триггеров ПЛИС

-

множество глобальных линий с низкими задержками распространения сигнала

-

наличие внутреннего распределённого ОЗУ Xilinx, реализующегося посредством тех же LUT – таблиц (серии Spartan, Virtex, XC4000).

-

наличие внутреннего блочного ОЗУ, один блок имеет ёмкость 4 кбит (семейства Virtex, Virtex-E, Spartan-II, Spartan-IIE) или 18 кбит (семейства Virtex-II и Virtex-IIPro), всего блоков до 556 на кристалл

-

наличие встроенных блоков умножителей 18х18 (семейства Virtex-II и Virtex-IIPro), всего блоков до 556 на кристалл

-

наличие встроенных блоков процессоров PowerPC-405 (семейство Virtex-IIPro), до 4 процессоров на кристалл

-

наличие высокоскоростных трансиверов(семейство Virtex-IIPro), до 24 со скоростью передачи данных 3.125 ГБит/с каждый Достоинствами технологии проектирования устройств на основе ПЛИС являются:

-

минимальное время разработки схемы (нужно лишь занести в память ПЛИС конфигурационный код);

-

в отличие от обычных элементов цифровой схемотехники здесь отпадает необходимость в разработке и изготовлении сложных печатных плат;

-

быстрое преобразование одной конфигурации цифровой схемы в другую (замена кода конфигурации схемы в памяти);

-

для создания устройств на основе ПЛИС не требуется сложное технологическое производство. ПЛИС конфигурируется с помощью персонального компьютера на столе разработчика. Потому иногда эту технологию называют «фабрикой на столе». Типичные области применения ПЛИС: цифровая обработка сигналов, пользовательская электроника, системы сбора данных, системы управления, телекоммуникационное оборудование, оборудование для систем беспроводной связи, компьютерное оборудование общего назначения.

D-триггеры.

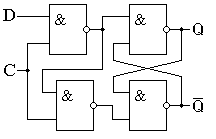

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 7.

Рисунок 7. Схема D-триггера (защелки)

Такой триггер получил название D-триггер. Название происходит от английского слова delay - задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D-триггера на принципиальных схемах приведено на рисунке 8.

Рисунок 8. Условно-графическое обозначение D-триггера (защелки)

Таблица истинности D-триггера достаточно проста, она приведена в таблице 3. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

Таблица 3. Таблица истинности D-триггера

|

С |

D |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

1 |

1 |

|

|

1 |

0 |

x |

0 |

Режим записи информации |

|

1 |

1 |

x |

1 |

Нужно отметить, что отдельный инвертор при реализации триггера на ТТЛ элементах не нужен, так как самый распространённый элемент ТТЛ логики - это “2И-НЕ”. Принципиальная схема D-триггера на элементах 2И-НЕ” приведена на рисунке 9.

Рисунок 9. Схема D-триггера, реализованная на ТТЛ элементах

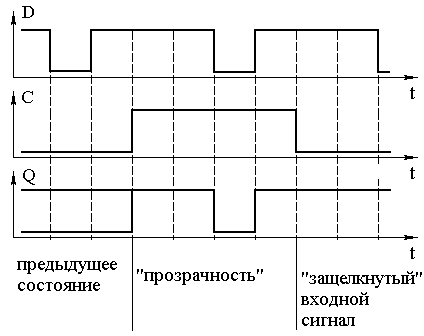

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название – триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

D-триггеры, работающие по фронту.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала.

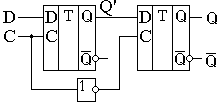

Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу. Сигнал синхронизации будем подавать на эти триггеры в противофазе. Схема такого триггера приведена на рисунке 12.

Рисунок 12. Схема D-триггера, работающего по фронту

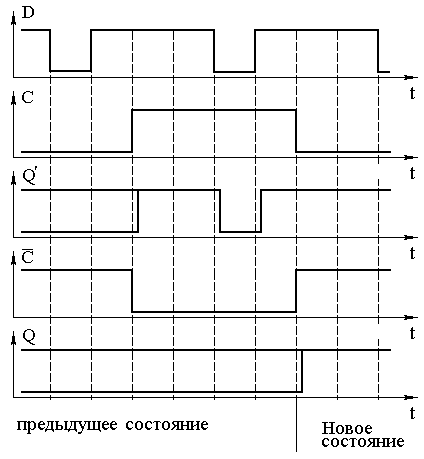

Рассмотрим работу схемы триггера, приведенной на рисунке 12 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 13. На этих временных диаграммах обозначение Q΄ соответствует сигналу на выходе первого триггера. Так как на вход синхронизации второго триггера тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме хранения.

Рисунок 13. Временные диаграммы D-триггера.

Обратите внимание, что сигнал на выходе всей схемы в целом не зависит от сигнала на входе "D" схемы. Если первый триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 12 запоминается только в момент изменения сигнала на синхронизирующем входе "C" с единичного потенциала на нулевой.

Динамические D-триггеры выпускаются в виде готовых микросхем или входят в виде готовых блоков в составе больших интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС).