- •Введение

- •1.2 Технические характеристики системы

- •2.2 Выбор умзч

- •2.3 Выбор микропроцессора

- •2.4 Выбор предварительного усилителя

- •2.5 Выбор микрофона

- •3 Расчет датчика обратной связи

- •4 Расчет передаточной функции системы. Определеие устойчивости

- •5 Построение и анализ лачх, лфчх, жлачх, жлфчх системы

- •6 Построение и анализ лачх корректирующего устройства

- •7 Подбор корректирующего устройства

- •Заключение

- •Список литературы

6 Построение и анализ лачх корректирующего устройства

Для того чтобы синтезировать корректирующее устройство необходимо выбрать тип корректирующего устройства. Для коррекции исходной системы автоматического регулирования выбираем последовательное корректирующее устройство.

Преимущество последовательных корректирующих устройств заключается в том, что они могут быть осуществлены в виде простых пассивных RC-контуров, и обеспечивают наиболее простую схему включения, не требует сложных элементов для согласования, передает значения величин управляющих сигналов (тока, напряжения), кроме того, расширяет полосу пропускания частот при наличии дифференцирующих звеньев в цепи регулирования, что позволяет передавать большую мощность сигнала.

Параллельное корректирующее устройство в исходной системе автоматического управления применить сложно. Параллельные корректирующие устройства требуют высоких коэффициентов усиления. Применение параллельного корректирующего устройства приведет к ослаблению коэффициента усиления всей системы в целом, что недопустимо в заданной системе, ибо исходная система не может имеет слишком низкий коэффициент усиления.

Синтез последовательного корректирующего устройства основан на использовании соотношения:

(96)

(96)

Поэтому для построения ЛАЧХ корректирующего устройства, необходимо из ЖЛАЧХ вычесть ЛАЧХ неизменяемой части.

Логарифмическая амплитудно-частотная характеристика последовательного корректирующего устройства описывается следующим выражением:

(97)

(97)

где

- желаемая ЛАЧХ,

- желаемая ЛАЧХ,

-

ЛАЧХ неизменяемой части.

-

ЛАЧХ неизменяемой части.

ЛАЧХ корректирующего устройства имеет вид в соответствии с рисунком 16.

+20 дБ/дек

-20 дБ/дек

0 дБ/дек

-40 дБ/дек

-20 дБ/дек

0 дБ/дек

0 дБ/дек

-60 дБ/дек

-40 дБ/дек

L (λ), дБ

λ, рад/с

1

2

3

1 – ЖЛАЧХ 2 – ЛАЧХ корректирующего устройства

3 – Исходная ЛАЧХ

Рисунок 16 – Построение ЛАЧХ корректирующего устройства

Из рисунка 16, следует что, ЛАЧХ корректирующего устройства имеет наклон минус 60 дБ/дек до частоты λ=10 рад/с, затем наклон меняется и до частоты λ=21 рад/с он становится равным минус 40 дБ/дек, и после частоты λ=21 рад/с, наклон ЛАЧХ корректирующего устройства становится неизменным и составляет 0 дБ/дек.

Таким образом, была построена ЛАЧХ корректирующего устройства, при введении которого, САУ громкостью звука соответствует заданным в техническом задании характеристикам. Определим передаточную функцию и проведем расчет корректирующего устройства.

7 Подбор корректирующего устройства

Для коррекции в системе применяется корректирующее устройство последовательного типа. КУ можно включать между различными элементами исходной системы. При выборе места включения руководствуются минимумом вносимой устройством погрешности. Наиболее предпочтительным вариантом является включение КУ между микропроцессором и делителем напряжения, так как RLC – цепочка корректирующего звена легко согласуется с электрическими параметрами ЦАП микропроцессора и делителем напряжения, а также на выходе ЦАП микропроцессора имеется сигнал высокого уровня, который ослабляется делителем напряжения, поэтому ослабление сигнала корректирующим устройством, не вызовет сбой в работе всей системы.

Передаточная функция корректирующего устройства имеет следующий вид:

(98)

(98)

где Т1 = 1\1 = 0,1 с;

Т2 = 1\2 = 0,048 с,

20lg kку = 35 дБ.

Тогда:

(99)

(99)

Для подбора корректирующего устройства разбиваем передаточную функцию на множители:

(100)

(100)

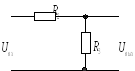

Первый множитель корректирующего устройства представляет собой корректирующую RC – цепочку [14]. Корректирующая RC – цепочка представлена в соответствии с рисунком 17:

Рисунок 17 – Корректирующая RC цепочка

Параметры RC цепочки:

(с)

(101)

(с)

(101)

Задавая R1=1 МОм, определяем емкость С1:

(102)

(102)

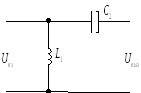

Второй множитель корректирующего устройства представляет собой корректирующую LC – цепочку представленную в соответствии с рисунком 18:

Рисунок 18 – Корректирующая LC цепочка

Параметры RC цепочки:

(с)

(103)

(с)

(103)

Задавая С2=5 мФ, определяем индуктивность L1:

(104)

(104)

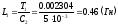

Третий множитель корректирующего устройства представляет собой корректирующую цепочку представленную в соответствии с рисунком 19:

Рисунок 19 – Корректирующая цепочка

Параметры цепочки:

(105)

(105)

Задавая R3=1 кОм, определяем сопротивление R2:

(106)

(106)

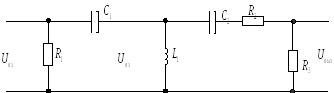

Корректирующее устройство примет вид:

Рисунок 20 – Корректирующая RC цепочка

Тогда структурная схема скорректированной САУ будет иметь вид:

Рисунок 20 – Структурная схема скорректированной САУ громкостью звука

Коррекцию системы можно произвести при помощи программы для микропроцессора, которая будет реализовывать передаточную функцию корректирующего устройства. Чтобы составить программу необходимо найти разностное уравнение в реальном масштабе времени.

После

замены

,

,

,

передаточная функция корректирующего

устройства примет вид:

,

передаточная функция корректирующего

устройства примет вид:

(106)

(106)

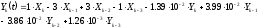

Разностное уравнение системы выглядит следующим образом:

(107)

(107)

Где Y – выходная функция;

X – входная функция.

Микропроцессор выявляет отклонение полученного сигнала от желаемого и выдает команду на устранение этого отклонения. Значения желаемого сигнала задаются в микропроцессоре в цифровом виде, вычисления осуществляются в машинном коде.

Реализация разностного уравнения на языке Assembler имеет вид:

;РАСЧЕТ РАЗНОСТНОГО УРАВНЕНИЯ

;Y(k) = 1*X(k) – 3*X(k-1) + 3*X(k-2) – 1*X(k-3) - 1,39Е-2*Y(k) + 3,99Е-2*Y(k-1) – 3,86Е-2*Y(k-2) + 1,26Е-3*Y(k-3)

;X – входной сигнал

;Y – выходной сигнал

A1 EQU 1; задаем постоянные коэффициенты

А2 EQU 3; задаем постоянные коэффициенты

A3 EQU 3; задаем постоянные коэффициенты

А4 EQU 1; задаем постоянные коэффициенты

А5 EQU 1,39Е-2; задаем постоянные коэффициенты

А6 EQU 3,99Е-2; задаем постоянные коэффициенты

А7 EQU 3,86Е-2; задаем постоянные коэффициенты

А8 EQU 1,26Е-3; задаем постоянные коэффициенты

X0 DB 0; выделение места под Х(k)

X1 DB 0; выделение места под X(k-l)

X2 DB 0; выделение места под X(k-2)

X3 DB 0; выделение места под X(k-3)

Y0 DB 0; выделение места под Y(k)

Y1 DB 0; выделение места под Y(k-1)

Y2 DB 0; выделение места под Y(k-2)

Y3 DB 0; выделение места под Y(k-3)

i port EQU 11h; номер порта для чтения

o port EQU 12h; номер порта для записи

start: метка начала цикла коррекции

in al, i port; читаем из порта данные

MOV X0,al;

MUL a1,A1; вычисление слагаемого А1*X(k)

MOV b1,a1; сохранение результата в b1

MOV a1,X1;

MUL a1,A2; вычисление слагаемого А2*X(k-1)

SUB b1,a1; вычисление слагаемого 1*X(k) – 3*X(k-1), результат в регистре b1

MOV a1,X2;

MUL a1,A3; вычисление слагаемого А3*X(k-2)

ADD b1,a1; вычисление слагаемого 1*X(k) – 3*X(k-1) + 3*X(k-2), результат в регистре b1

MOV a1,X3;

MUL a1,A4; вычисление слагаемого А4*X(k-3)

SUB b1,a1; вычисление слагаемого 1*X(k) – 3*X(k-1) + 3*X(k-2) – 1*X(k-3), результат в регистре b1

MOV a1,Y0;

MUL a1,A5; вычисление слагаемого А5*Y(k)

SUB b1, a1; вычисление слагаемого 1*X(k) – 3*X(k-1) + 3*X(k-2) – 1*X(k-3) - 1,39Е-2*Y(k), результат в регистре b1

MOV a1,Y1;

MUL a1,A6; вычисление слагаемого А6*Y(k-1)

ADD b1, a1; вычисление слагаемого 1*X(k) – 3*X(k-1) + 3*X(k-2) –1*X(k-3) - 1,39Е-2*Y(k) + 3,99Е-2*Y(k-1), результат в регистре b1

MOV a1,Y2;

MUL a1,A7; вычисление слагаемого А7*Y(k-2)

SUB b1, a1; вычисление слагаемого 1*X(k) – 3*X(k-1) + 3*X(k-2) – 1*X(k-3) - 1,39Е-2*Y(k) + 3,99Е-2*Y(k-1) – 3,86Е-2*Y(k-2), результат в регистре b1

MOV a1,Y3;

MUL a1,A8; вычисление слагаемого А8*Y(k-3)

ADD b1, a1; вычисление значения всего выражения 1*X(k) – 3*X(k-1) + 3*X(k-2) – 1*X(k-3) - 1,39Е-2*Y(k) + 3,99Е-2*Y(k-1) – 3,86Е-2*Y(k-2) +1,26Е-3 *Y(k-3), результат в регистре b1

MOV Y3,Y2; сохранение значений для следующего такта

MOV Y2,Y1; сохранение значений для следующего такта

MOV Y1,Y0; сохранение значений для следующего такта

MOV Y0,b1; сохранение значений для следующего такта

MOV X3,X2; сохранение значений для следующего такта

MOV X2,X1; сохранение значений для следующего такта

MOV X1,X0; сохранение значений для следующего такта

MOV X0,a1; сохранение значений для следующего такта

out о port,b1; вывод управляющего сигнала из b1

JMP start; замыкание цикла.

Блок-схема программы коррекции представлена в соответствии с рисунком 22.

Рисунок 22 – Блок схема программы коррекции

Из анализа программы следует, что для ее реализации требуются следующие операции: логические (переадресации), короткие (сложение, вычитание) и длинные (умножение). Для используемого микропроцессора время переадресации п = 5.0 мкс, коротких операций к = 9.2 мкс, а длинных операций д = 120 мкс. В результате можно найти время выполнения всей программы:

в. пр. = 20·5·10-6 + 7·9,2·10-6 + 8·120·10-6 = 1.12410-3 c.

Время срабатывания RCL – цепочки равна сумме срабатывания отдельных ее элементов.

ср = с1+с2+L1 =10-7+5·10-3+0,46=0,47 с.

Вывод: была разработана программа коррекции для микропроцессора на языке Assembler и рассчитано корректирующее устройство на RLC цепочках.