- •1 Расшифровка и анализ задания

- •2.2 Генератор тактовых импульсов к1810гф84

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.7 Программируемый параллельный интерфейс кр580вв55

- •4.2 Программируемый контроллер прерываний кр580вн59

- •4.3 Программируемый контроллер клавиатуры и индикации кр580вв79

2.7 Программируемый параллельный интерфейс кр580вв55

БИС программируемого параллельного интерфейса КР58ОВВ55 предназначена для организации ввода/вывода параллельной информации различного формата и позволяет реализовать большинство известных протоколов обмена по параллельным каналам. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием (дисплеем, телетайпом, накопителем).

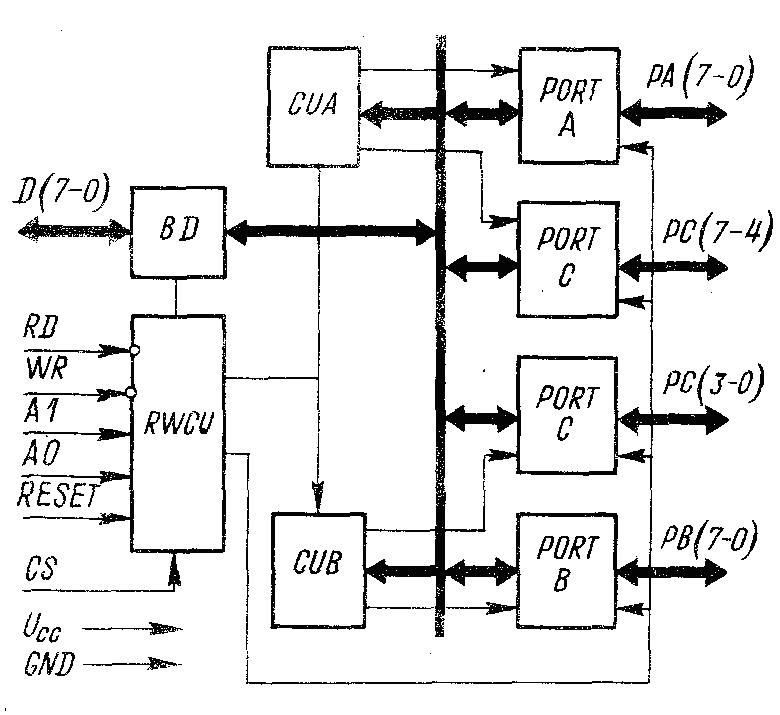

Структурная схема ППИ приведена на рисунке 9.

Рисунок 9 — Структурная схема программируемого параллельного интерфейса КР580ВВ55

В состав БИС входят: двунаправленный 8-разрядный буфер данных (ВD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (РОRТ А, В и С) для обмена информацией с внешними устройствами; схема управления группой А (СUA), вырабатывающая сигналы управления каналом А и старшими разрядами канала С[РС(7-4)]; схема управления группой В (СUВ), вырабатывающая сигналы управления каналом В и младшими разрядами канала С[РС(3-0)].

Таблица 9 — Описание выводов программируемого параллельного интерфейса КР580ВВ55.

-

Обозначение вывода

Номер контакта

Назначение вывода

1

2

3

D(7-0)

27; 28; 29; 30;

31; 32; 33; 34

Вход/выход данных

RD

5

Чтение; L-уровень сигнала разрешает считывание информации из регистра, адресуемого по входам А0, А1 на шину D(7-0)

WR

36

Запись; L-уровень сигнала разрешает запись информации с шипы D(7—0) в регистр ППИ, адресуемый по входам А0, А1

АО, А1

9; 8

Входы для адресации внутренних регистров ППИ

RESET

35

Сброс; H-уровень сигнала обнуляет регистр управляющего слова и уста-навливает все порты в режим ввода

CS

6

Выбор микросхемы; L-уровень сигнала подключает ППИ к системной шине

РА(7-0)

37; 38; 39; 40;

1; 2; 3; 4

Вход/выход канала А

РВ(7-0)

15; 24; 23; 22;

21; 20;19; 18

Вход/выход канала В

РС(7-0)

10; 11; 12; 13:

17; 16; 15; 14

Вход/выход канала С

Ucc

26

Напряжение питания ( + 5 В)

GND

7

Напряжение питания (0 В)

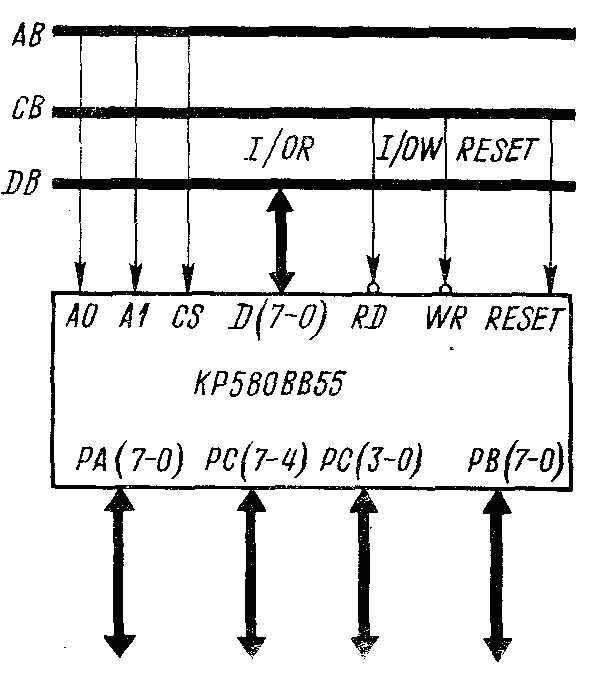

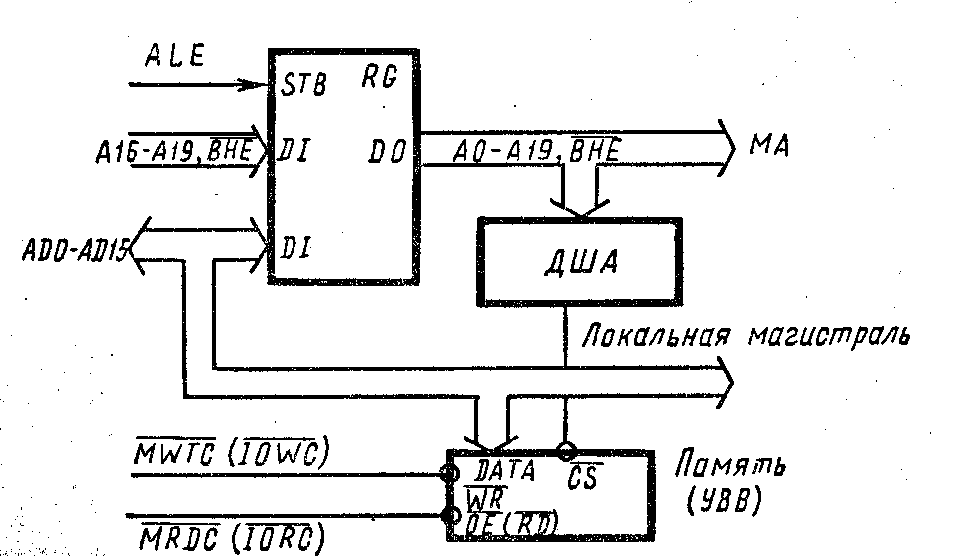

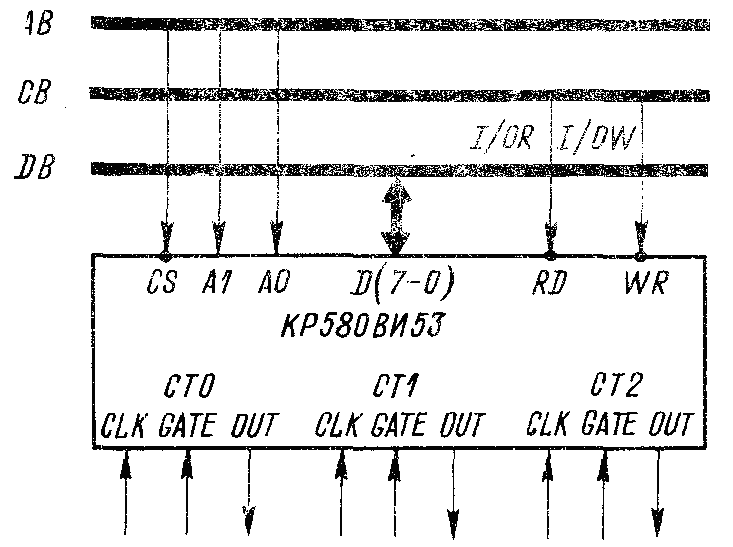

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в таблице 9. Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рисунке 10. Сигналы управления работой ППИ подаются на блок К\УС11 и вместе с адресными входами АО, А1 задают вид операции, выполняемой БИС.

Рисунок 10 — Схема сопряжения программируемого параллельного интерфейса КР580ВВ55 со стандартной системной шиной

Основные электрические параметры микросхемы КР580ВВ55 следующие:

Выходное напряжение логического нуля UOL, В < 0,4

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления от источника питания ICC, мА < 60

Ток утечки каналов А, В, С, D

при невыбранном режиме IIOZ, мкА >100,...,100

Ток утечки на управляющих входах IIL, мкА —10,...,10

2.8 Разработка уточненной структурной схемы

Микропроцессорный комплект серии К1810 включает в себя 8- и 16-разрядные МП, позволяющие производить высокоскоростные вычисления и обмен данными; устройства формирования магистралей и арбитража многопроцессорных взаимодействий и универсальные интерфейсные БИС, предназначенные для выполнения широкого набора функций ускоренной передачи информации, счета временных интервалов и обработки прерываний от УВВ

В составе микроЭВМ, построенной на основе МПК серии К1810, можно использовать все интерфейсные БИС 8-разряд-ного МПК серии КР580.

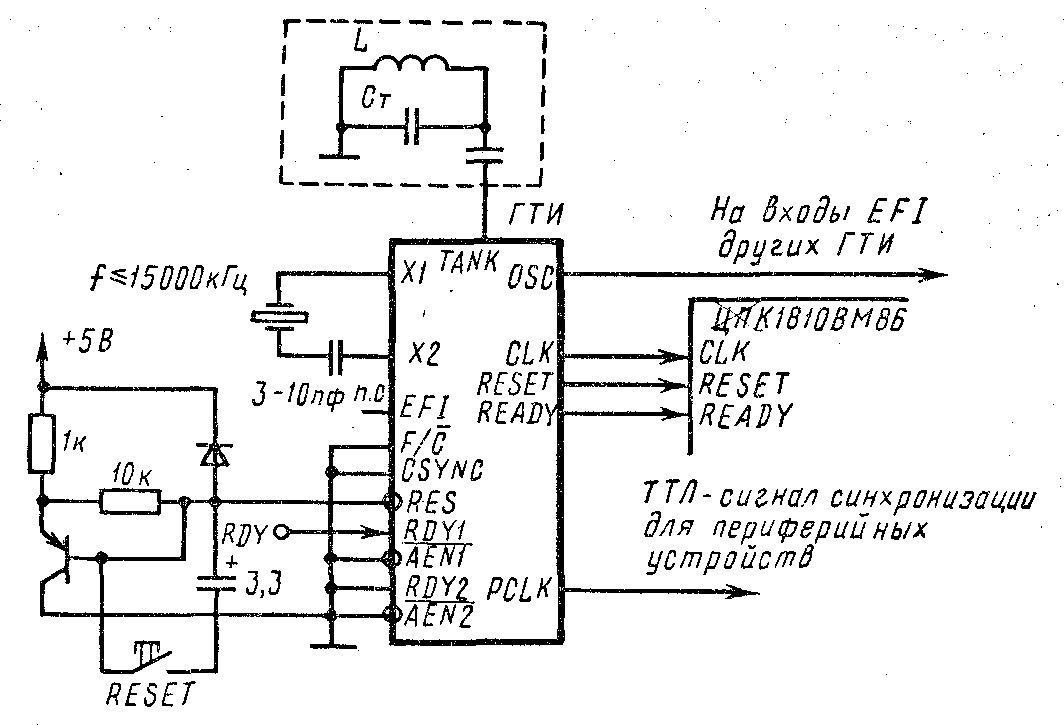

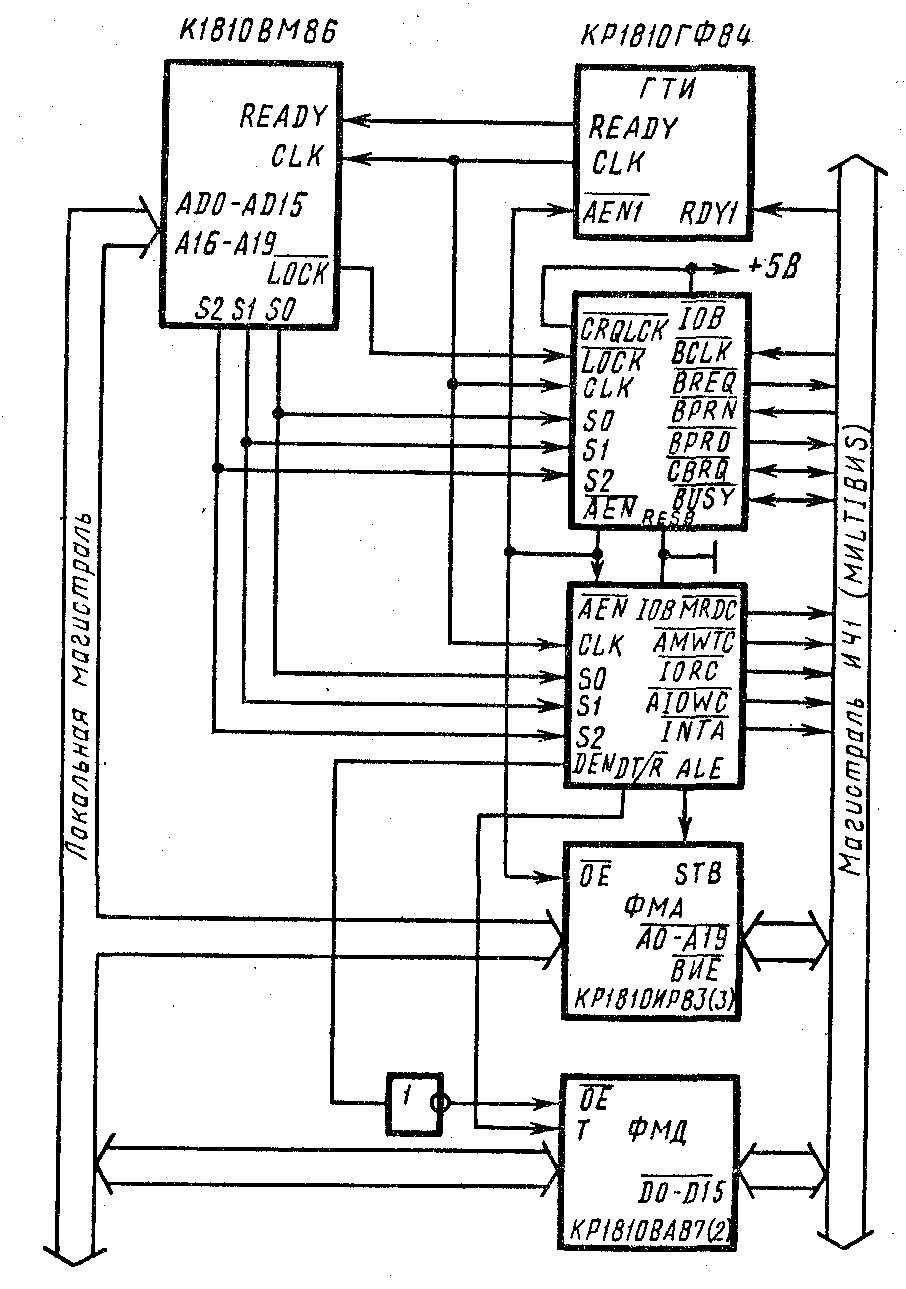

2.8.1 Синхронизация работы МП БИС К1810ВМ86. Для синхронизации работы МП БИС используется микросхема тактового генератора 1810ГФ84. Схема подключения тактового генератора к МП БИС показаны на рисунке 11.

Основной сигнал синхронизации МП частотой до 5 МГц формируется делением на 3 опорной частоты ОSС кварцевого генератора (вход F/С = 0) или внешнего задающего сигнала, подключенного ко входу ЕР1 (вход F/С = 1), что позволяет использовать один кварцевый резонатор для задания частоты нескольким тактовым генераторам. Их полную синхронизацию можно обеспечить одновременной подачей внешнего сигнала синхронизации СSYNC на вход микросхем КР1810ГФ84.

Рисунок 11 — Схема подключения тактового генератора к МП БИС

Кварцевый резонатор можно возбудить и на более высокой гармонике, для чего ко входу ТANК через разделительный конденсатор подключается LС-контур, настроенный на частоту верхней гармоники генератора.

Сигнал синхронизации периферийного оборудования РСLК для работы с более медленными УВВ вырабатывается путем деления частоты тактового сигнала СLК на 2.

Микросхема К1810ГФ84 вырабатывает также сигнал RESET начальной установки и стробирует внешние сигналы готовности периферийного оборудования READY.

Наличие

двух сигналов готовности RDY1,

RDY2

и разрешения

![]() ;

;

![]() необходимо для построения систем с

несколькими магистралями, к которым

подключены медленные устройства памяти

и ввода-вывода, а также для синхронизации

многопроцессорных взаимодействий.

необходимо для построения систем с

несколькими магистралями, к которым

подключены медленные устройства памяти

и ввода-вывода, а также для синхронизации

многопроцессорных взаимодействий.

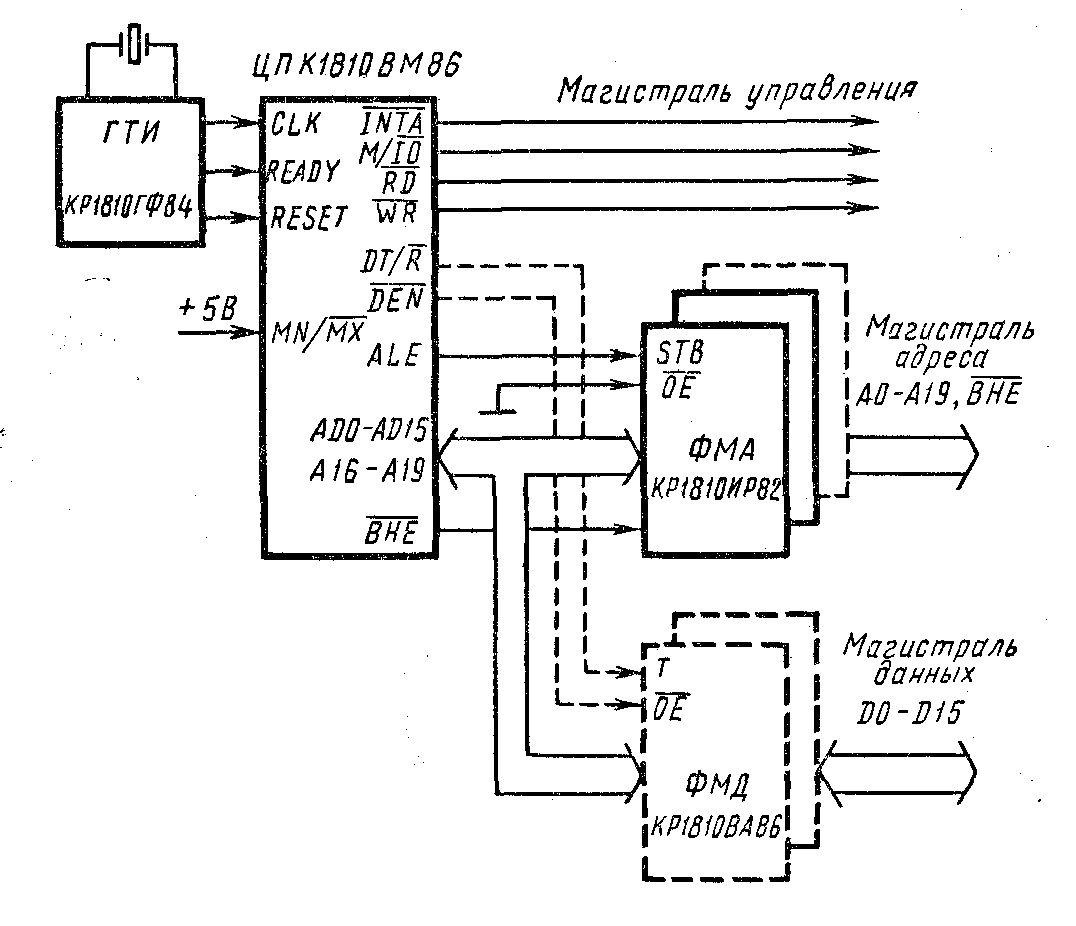

2.8.2 Формирование магистралей адреса, данных и управления микроЭВМ. Схемы формирования магистралей адреса, данных и управления различны при включении МП К1810ВМ86 в минимальном или максимальном режиме.

Рисунок 12 — Формирование магистралей адреса и данных при работе БИС ЦП К1810ВМ86 в минимальном режиме

В

минимальном режиме магистраль управления

образуется сигналами:

![]() — обращение к памяти или к УВВ,

— обращение к памяти или к УВВ,

![]() - строб чтения данных,

- строб чтения данных,

![]() — строб записи данных,

— строб записи данных,

![]() — строб чтения вектора прерываний, а

для управления регистрами магистрали

адреса и формирователями магистрали

данных используются сигналы приема-передачи

—

— строб чтения вектора прерываний, а

для управления регистрами магистрали

адреса и формирователями магистрали

данных используются сигналы приема-передачи

—

![]() и разрешения обмена данными —

и разрешения обмена данными —

![]() (рисунок 12).

(рисунок 12).

В максимальном режиме для формирования управляющих сигналов применяют системный контроллер КР1810ВГ88, обрабатывающий сигналы SO, SI, S2 состояния МП.

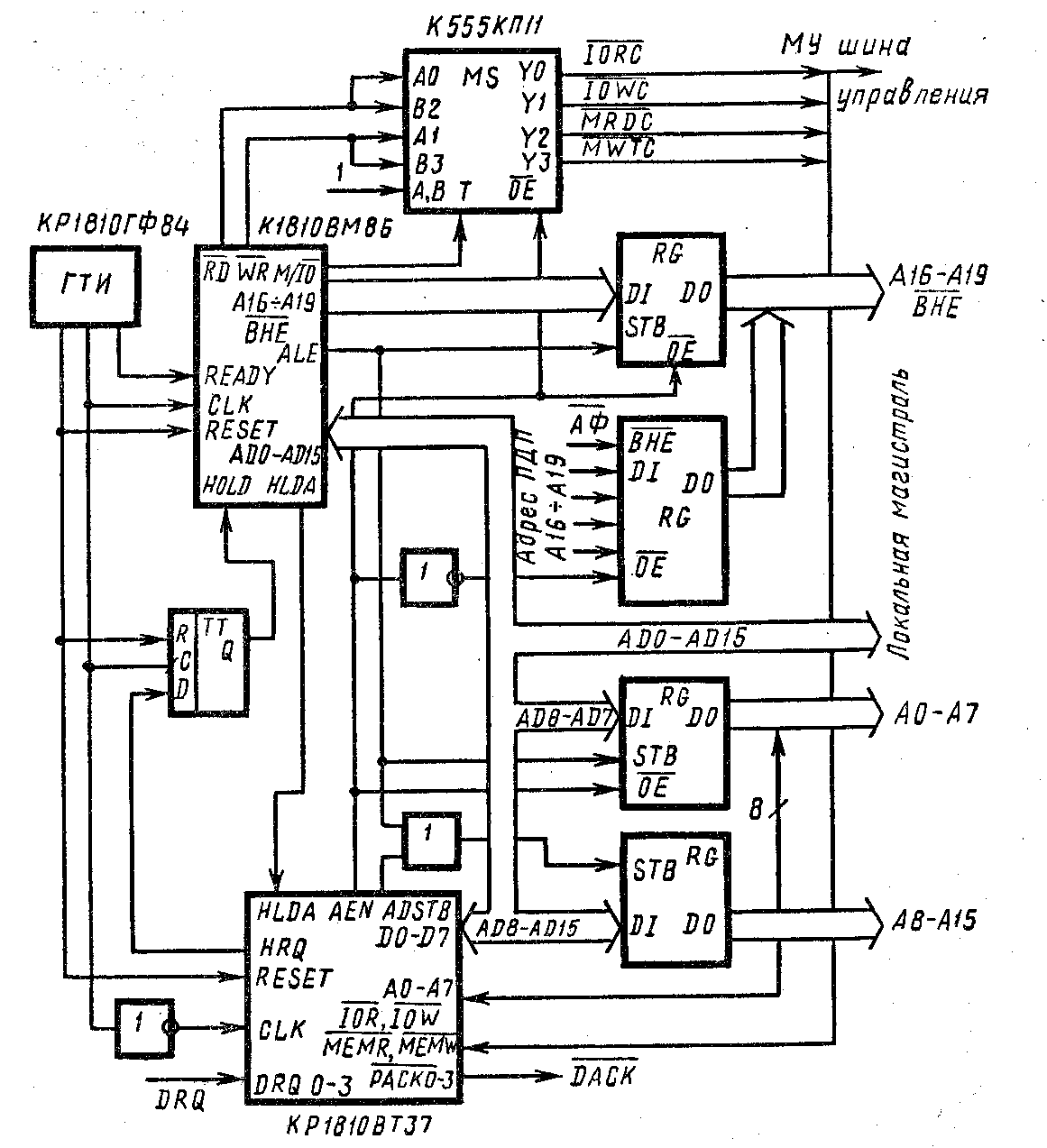

МП К1810ВМ86 можно подключать к общей многопроцессорной магистрали ИЧ1 (MULTIBUS); при этом для арбитража доступа МП БИС к магистрали необходимо использовать арбитр магистрали БИС К1810ВБ89 (рисунок 13).

Рисунок 13 — Подключение МП БИС К1810ВМ86 в максимальном режиме к мультиплексорной магистрали ИЧ1 (MULTIBUS)

При

необходимости захвата магистрали

процессором арбитр вырабатывает сигналы

запроса захвата магистрали

![]() и всеобщего запроса

и всеобщего запроса

![]() .

Если магистраль свободна (

.

Если магистраль свободна (![]() равно 1) и есть разрешение

равно 1) и есть разрешение

![]() с внешнего арбитра распределения

приоритетов (при параллельной обработке

приоритетов), то формируется сигнал

захвата магистрали

с внешнего арбитра распределения

приоритетов (при параллельной обработке

приоритетов), то формируется сигнал

захвата магистрали

![]() и по сигналу

и по сигналу

![]() информация с внутренней магистрали

адреса выдается на магистраль ИЧ1.

Этот же сигнал разрешает системному

контроллеру К1810ВГ88 выдать на магистраль

сигналы управления

информация с внутренней магистрали

адреса выдается на магистраль ИЧ1.

Этот же сигнал разрешает системному

контроллеру К1810ВГ88 выдать на магистраль

сигналы управления

![]() ,

MWTC,

,

MWTC,

![]() ,

IOWC.

,

IOWC.

Сигнал

![]() используется в схемах с последовательным

заданием приоритетов для трансляции

сигнала разрешения доступа

используется в схемах с последовательным

заданием приоритетов для трансляции

сигнала разрешения доступа

![]() (в том случае, когда процессор не требует

доступа к магистрали) арбитру с более

низким приоритетом (приоритет задается

последовательностью соединения арбитров)

на его вход

(в том случае, когда процессор не требует

доступа к магистрали) арбитру с более

низким приоритетом (приоритет задается

последовательностью соединения арбитров)

на его вход

![]() для дальнейшей обработки.

для дальнейшей обработки.

Для

монопольного захвата магистрали на

время выполнения одной команды (с

префиксом

![]() )

процессор может вырабатывать сигнал

)

процессор может вырабатывать сигнал

![]() .

.

3 РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

3.1 Контроллер прямого доступа к памяти КР580ВТ57

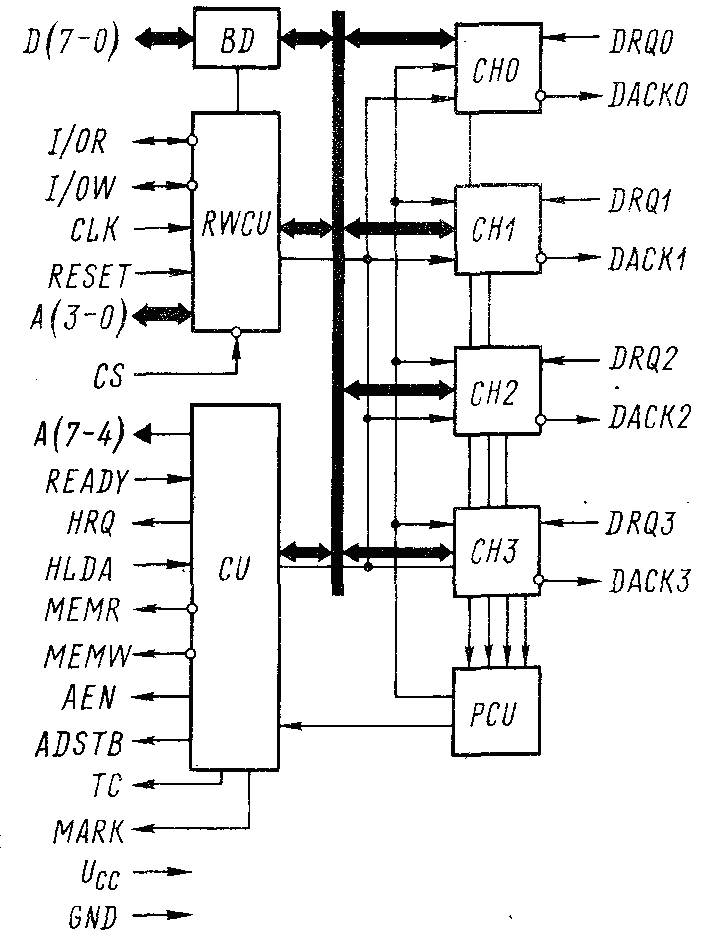

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначена для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства. Контроллер прямого доступа к памяти (КПДП) генерирует управляющие сигналы, необходимые для организации обмена. КПДП содержит четыре канала прямого доступа, каждый из которых обеспечивает передачу блока данных размером до 16 Кбайт с произвольным начальным адресом в диапазоне от 0 до 64 Кбайт.

Рисунок 14 — Структурная схема контроллера прямого доступа к памяти КР580ВТ57

Упрощенная структурная схема КПДП приведена на рисунке 14. В состав БИС входят: двунаправленный двустабильный буфер данных (ВD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (СU), содержащий регистры режима и состояния КПДП и обеспечивающий последовательность операций, необходимую для организации режима прямого доступа к памяти; блок управления приоритетами (РСU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа (СН0 — СН3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

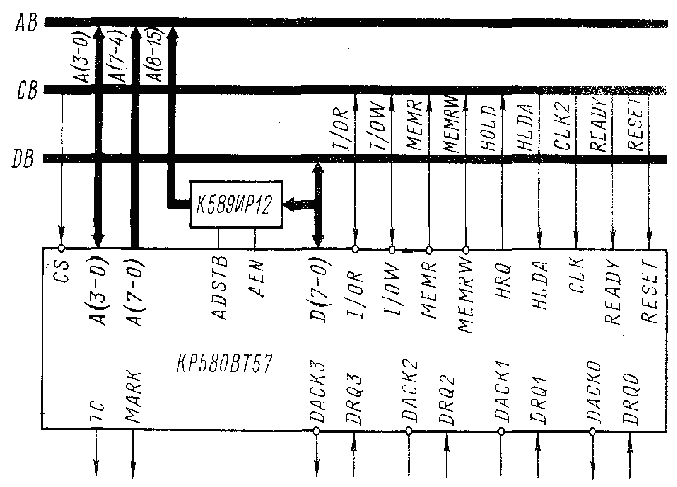

Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12 показана на рисунке 15.

Рисунок 15 — Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12

Назначение входных, выходных и управляющих сигналов КПДП приведено при описании выводов микросхемы в таблице 10.

Таблица 10 — Описание выводов контроллера прямого доступа к памяти КР580ВТ57

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

D(7-0) |

21;22;23;26; 27;28;29;30 |

Входы/выходы данных для обмена с МП |

Продолжение таблицы 10

|

1 |

2 |

3 |

|

I/OR |

1 |

Чтение ввода/вывода — двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает чтение информации из КПДП в МП; выходной сигнал L-уровня разрешает чтение из ВУ |

|

I/OW |

2 |

Запись ввода/вывода — двунаправленный тристабильный вход/выход; входной сигнал L-уровня разрешает программирование КПДП: выходной сигнал L-уровня разрешает запись в ВУ |

|

CLK |

12 |

Вход тактовых импульсов |

|

RESET |

13 |

Вход установки 0 |

|

A(3-0) |

35;34;33;32 |

Двунаправленные тристабильные адресные выводы |

|

CS |

11 |

Выбор микросхемы |

|

A(7-4) |

40;39;38;37 |

Тристабильные адресные выходы |

|

READY |

6 |

Готовность — входной сигнал Н-уровня указывает на готовность к обмену |

|

HRQ |

10 |

Запрос захвата — выходной сигнал Н-уровня указывает на запрос о доступе КПДП к системным шинам |

|

HLDA |

7 |

Подтверждение захвата — входной сигнал Н-уровня указывает на возможность доступа к системным шинам |

|

MEMR |

3 |

Чтение из памяти — тристабильный выход; выходной сигнал L-уровня разрешает чтение из ячейки памяти, адресуемой КПДП |

|

MEMW |

4 |

Запись в память — тристабильный выход; выходной сигнал L-уровня разрешает запись в ячейку, адресуемую КПДП |

|

AEN |

9 |

Разрешение адреса — сигнал Н-уровня используется для блокировки некоторых шин адреса и данных |

|

ADSTB |

8 |

Строб адреса — сигнал Н-уровня указывает на нахождение на шине D(7—0) старшего байта адреса ЗУ |

|

TC |

36 |

Конец счета — сигнал Н-уровня определяет выполнение последнего цикла передачи блока данных |

|

MARK |

5 |

Маркер — сигнал Н-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена, кратное 128 |

Продолжение таблицы 10

|

1 |

2 |

3 |

|

DRQ3-DRQ0 |

16;17;18;19 |

Запросы прямого доступа к памяти каналов СН3-СН0; сигнал Н-уровня указывает на запрос от ВУ |

|

DACK3-DACK0 |

15;14;24;25 |

Подтверждение запросов прямого доступа к памяти каналов СН3-СН0; сигнал L-уровня указывает на разрешение обмена |

|

UСС |

31 |

Напряжение питания ( + 5 В) |

|

GND |

20 |

Напряжение питания (0 В) |

Основные электрические параметры микросхемы КР580ВТ57 при температуре окружающей среды + 25 + 10°С приведены ниже:

Выходное напряжение логического нуля UOL, В < 0,45

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления IСС, мА < 100

Ток утечки на входах IIL, мкА < 1,5

Ток утечки на управляемых выводах IОL, мкА —1,5,...,1,5

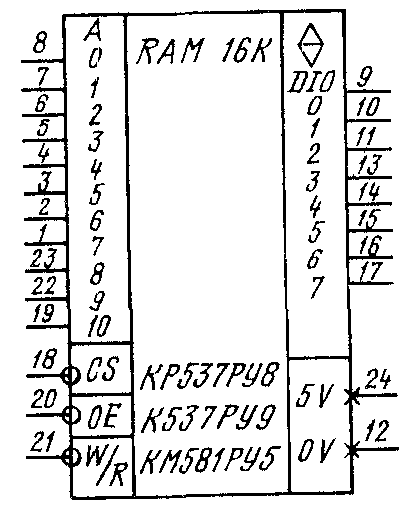

3.2 БИС ОЗУ К537РУ8

Наиболее развитым функциональным составом из серий КМДП микросхем обладает серия К537. Функциональный ряд серии включает более 15 типов микросхем, отличающихся информационной емкостью (от 1024 до 16 384 бит), организацией (одноразрядная и байтовая), быстродействием (более чем в 5 раз), уровнем потребляемой мощности. Назначение выводов корпусов микросхем серии К537 указано на рисунке 16.

Динамические параметры микросхем серии К537 в диапазоне температур —10...+ 70° С:

tц.эп не менее 350

tв. ВМ не более 200

tус. ВМ не менее 70

![]() не менее

220

не менее

220

![]() не менее 30

не менее 30

tсх.А ВМ не менее 60

Рисунок 16 — Микросхема памяти К537РУ8

Общими свойствами микросхем серии К537 являются: единое напряжение питания 5В, ТТЛ-уровни входных и выходных сигналов, выход с тремя состояниями, высокая помехоустойчивость, допустимая значительная емкость нагрузки (200 пФ и более), небольшое энергопотребление, причем при хранении почти на три порядка меньше, чем при обращении, способность сохранять записанную информацию при пониженном до 2...3 В напряжении питания.

Эту способность КМДП-микросхем всех серий широко используют для придания устройствам памяти свойства энергонезависимости, т.е. свойства сохранять информацию при сбоях и отключении питания. С этой целью в блоке статического ОЗУ к выводам питания микросхем через ключ, например полупроводниковый диод, подключают низковольтный буферный источник питания с напряжением 2 ... 3 В. При нормальном режиме питания диод закрыт, а при выключении основного питания диод открывается и подключает к микросхемам буферный источник напряжения. В это время следует обеспечить изоляцию накопителя по информационным цепям, запрещающим значением уровня на входе CS, чтобы не повредить хранящуюся информацию. Для увеличения времени сохранения информации в аварийном режиме необходимо снижать ток потребления микросхем, повышать емкость низковольтных малогабаритных элементов питания и уменьшать ток их саморазряда.

В устройствах памяти на микросхемах серии К537 для снижения потребляемой мощности следует предусмотреть возможность автоматического переключения питания микросхем в режиме хранения с основного источника 5 В на маломощный буферный источник напряжения, который обеспечивает питание только микросхем ОЗУ на уровне, достаточном для сохранения информации. Для микросхемы КР537РУ8 допускается снижать напряжение до 3 В.

Микросхемы на МДП-транзисторах любого типа чувствительны к воздействию статического электричества из-за высокого входного сопротивления. Даже кратковременное повышение входного напряжения с недопустимо высоким уровнем может вызвать электрический пробой тонкого слоя подзатворного диэлектрика. Для защиты от вредного воздействия перенапряжения все входы микросхем защищают диодно-резистивными цепями, встроенными внутрь кристалла. Защитные цепи построены по схеме последовательного соединения двух диодов VD1, VD2 и токоограничивающего резистора R. От воздействия высокого положительного потенциала на входе защищает диод VD1, который при открывании фиксирует входное напряжение на уровне напряжения питания. Высокий отрицательный потенциал открывает диод VD2, который ограничивает его безопасным для микросхемы уровнем.

Для многих типов КМДП-микросхем, и в частности для микросхем серии К537, существует опасность теплового пробоя р-п переходов в кристалле из-за «тиристорного эффекта».

Сущность этого явления заключается в том, что при повышении напряжения в шине питания до 11-12 В из-за бросков тока при включении и влияния индуктивностей шин, а также при превышении входным сигналом напряжения питания внутри кристалла активизируются паразитные биполярные р-п-р-п структуры и из-за наличия положительной обратной связи по цепям токов утечки может появиться эффект неуправляемого нарастания тока стока, близкий по механизму к аналогичному явлению в тиристорах в момент их переключения. Поскольку в КМДП-структурах отсутствуют токоограничивающие резисторы нагрузки, то нарастание тока приводит к развитию теплового пробоя в кристалле и, как следствие, к неисправности микросхемы.

При применении микросхем памяти, изготовленных по КМДП-технологии, в частности микросхем серии К537, необходимо соблюдать порядок включения питания и подачи входных сигналов: вначале должно быть включено напряжение питания. При выключении блока ОЗУ следует снять входные сигналы (адресные, управляющие и информационные) и затем отключить источник напряжения питания. Необходимо обеспечить также выполнение условия, по которому напряжение сигналов не должно превышать напряжения питания микросхемы.

Микросхемы

серии К537 работают в режимах записи,

считывания и хранения. Также эти

микросхемы являются тактируемыми: в

режимах записи и считывания необходимо

сигнал

![]() подавать импульсом, а сигнал

подавать импульсом, а сигнал

![]() может иметь форму уровня напряжения

или импульса.

может иметь форму уровня напряжения

или импульса.

Микросхема

КР537РУ8 имеет дополнительный управляющий

сигнал

![]() (разрешение по выходу): при подаче этого

сигнала одновременно с сигналом

(разрешение по выходу): при подаче этого

сигнала одновременно с сигналом

![]() отсчет времени появления сигнала

ведется от отрицательного перепада

сигнала

отсчет времени появления сигнала

ведется от отрицательного перепада

сигнала

![]() .

Существует возможность стробирования

выходной информации сигналом

.

Существует возможность стробирования

выходной информации сигналом

![]() ,

подаваемым с некоторой задержкой

относительно сигнала

,

подаваемым с некоторой задержкой

относительно сигнала

![]() .

В этом случае при

.

В этом случае при

![]() =1,

т.е. до момента подачи этого сигнала,

выхо-ды находятся в третьем состоянии

даже при

=1,

т.е. до момента подачи этого сигнала,

выхо-ды находятся в третьем состоянии

даже при

![]() = 0. Только в момент Поступления сигнала

ОЕ выходы переходят в функциональное

состояние.

= 0. Только в момент Поступления сигнала

ОЕ выходы переходят в функциональное

состояние.

3.3 БИС ПЗУ К541РТ2

Микросхемы программируемых ПЗУ по принципу построения и функционирования аналогичны масочным ПЗУ, но имеют существенное отличие в том, что допускают программирование на месте своего применения пользователем. Операция программирования заключается в разрушении (пережигании) части плавких перемычек на поверхности кристалла импульсами тока амплитудой 30 ... 50 мА. Технические средства для выполнения этой операции достаточно просты и могут быть построены самим пользователем. Это обстоятельство в сочетании с низкой стоимостью и доступностью микросхем ППЗУ обусловило их широкое распространение в радиолюбительской практике.

В данном курсовом проекте рассматривается применение микросхемы ПЗУ К541РТ2, представленной на рисунке 17.

Микросхемы ППЗУ серии К541 выполнены по технологии ИИЛ.

Рисунок 17 — Микросхема ПЗУ К541РТ2

Матрица до программирования, т. е. в исходном состоянии, содержит однородный массив проводящих перемычек, соединяющих строки и столбцы во всех точках их пересечений. Перемычки устанавливают из поликристаллического кремния. Перемычка в матрице выполняет роль ЭП. Наличие перемычки кодируют логической 1, если усилитель считывания является повторителем, и логическим 0, если усилитель считывания — инвертор. Следовательно, микросхема ППЗУ в исходном состоянии перед программированием в зависимости от характеристики выходного усилителя может иметь заполнение матрицы либо логическим 0, либо логической 1.

Программирование микросхемы, матрица которой в исходном состоянии заполнена 0, заключается в пережигании перемычек в тех ЭП, где должны храниться 1. Если матрица в исходном состоянии заполнена 1, то пережигают перемычки в ЭП, где должны храниться 0.

Микросхемы ППЗУ потребляют большую мощность от источника питания. Поэтому представляется целесообразным использовать их свойство работать в режиме импульсного питания, когда питание на микросхему подают только при обращении к ней для считывания информации. Особенности применения микросхем ППЗУ в этом режиме состоят; в следующем: во-первых, на управляющие входы должны быть поданы уровни, разрешающие доступ к микросхеме: если необходим 0, то данный вывод соединяют с общим выводом, если 1, то с шиной через резистор с сопротивлением 1 кОм; в этом случае функции сигнала выбора микросхемы выполняет импульс напряжения питания Ucc; во-вторых, для обеспечения1 режима импульсного питания применяют транзисторные ключи, на переходах которых падает часть напряжений, поэтому напряжение, подаваемое к внешним ключам, должно быть выбрано с учетом требования иметь на выводе питания микросхемы номинальное напряжение 5 В; в-третьих, из-за инерционности процессов коммутации цепи питания время выборки адреса микросхемы увеличивается в 2—3 раза.

При использовании импульсного режима питания среднее значение потребляемого тока и, следовательно, уровень потребляемой мощности существенно уменьшаются.

3.4 Разработка уточненной структурной схемы

3.4.1 Подключение устройств памяти и ввода—вывода к магистралям микроЭВМ. В микропроцессорных системах, построенных на основе МП БИС К1810ВМ86, могут быть использованы 8-и 16-разрядные устройства ввода—вывода и 16-разрядные устройства памяти. С МП К1810ВМ88 используются только 8-разрядные устройства или 16-разрядные с применением специальной схемы преобразования разрядности магистрали.

Вариант подключения устройств памяти и ввода—вывода к магистралям МП К1810ВМ86 показаны на рисунок 18.

Рисунок 18 — Подключение к магистралям микроЭВМ устройств памяти и ввода-вывода

При

подключении 8-разрядных УВВ к старшему

или младшему байту магистрали данных

на дешифратор адреса подаются также

сигналы АО и

![]() ,

указывающие на обращение процессора

соответственно к младшему и старшему

байтам.

,

указывающие на обращение процессора

соответственно к младшему и старшему

байтам.

Если

МП БИС работает в минимальном режиме и

для обращения к устройствам используются

управляющие сигналы

![]() и

и

![]() ,

то дешифратор адреса памяти и УВВ должен

распознавать сигнал

,

то дешифратор адреса памяти и УВВ должен

распознавать сигнал

![]() и в зависимости от его состояния

формировать сигналы выбора устройств

памяти или ввода—вывода.

и в зависимости от его состояния

формировать сигналы выбора устройств

памяти или ввода—вывода.

Для упрощения в дальнейших схемах сигналы, участвующие в выборке устройств, не будут показываться.

3.4.2 Подключение программируемого контроллера приоритетных прерываний KI810BH59A. Микросхема К1810ВН59А является расширенным функциональным аналогом БИС КР580ВН59 и может использоваться в блоках приоритетных прерываний (БПП) микроЭВМ, построенных на основе МПК серий КР580 и К1810.

При

работе с процессором К1810ВМ86 БПП

программируется на формирование

однобайтового вектора прерываний в

ответ на поступление 2-го сигнала

![]() с шины управления микроЭВМ. Схема имеет

8 уровней запросов прерывания

IRQ0—IRQ7, однако возможно расширение

уровней до 64 за счет подключения

дополнительных 8 ведомых микросхем

К1810ВН59А.

с шины управления микроЭВМ. Схема имеет

8 уровней запросов прерывания

IRQ0—IRQ7, однако возможно расширение

уровней до 64 за счет подключения

дополнительных 8 ведомых микросхем

К1810ВН59А.

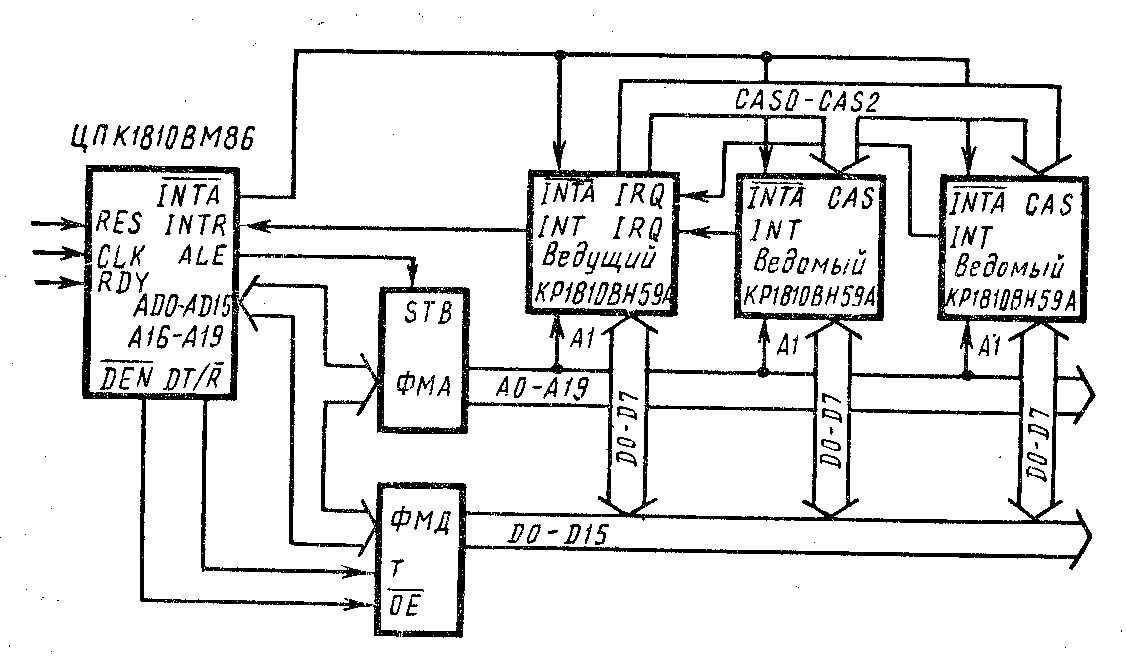

На рисунок 19 показан наиболее простой способ подключения ведущей и ведомых микросхем К1810ВН59А к МП К1810ВМ86, работающему в минимальном режиме. Недостаток этого способа подключения — низкая нагрузочная способность магистрали данных из-за непосредственного подключения к ней выводов данных всех контроллеров прерываний.

Рисунок 19 — Первый вариант подключения ведущей и ведомых БИС контроллеров прерываний К1810ВН59А к ЦП К1810ВМ86, включенному в минимальный режим

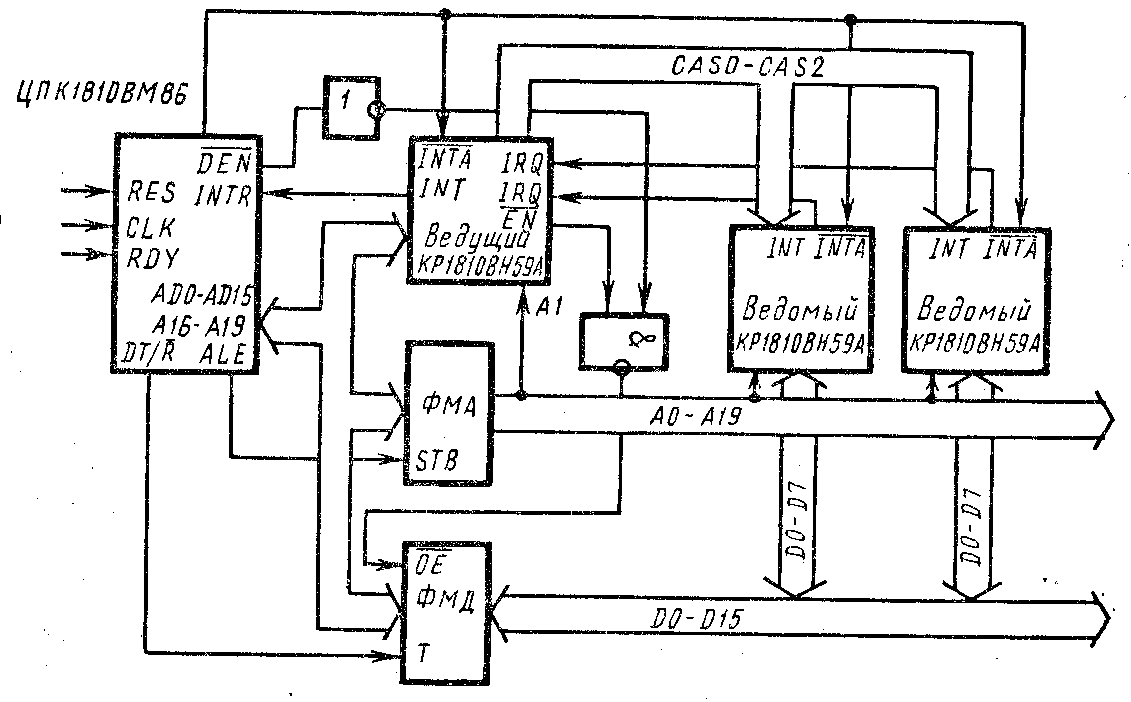

Более

предпочтительный способ подключения,

особенно при использовании только одной

БИС К1810ВН59А, показан на рисунок 20. Здесь

шина данных ведущего контроллера

прерываний включена на локальную

магистраль микропроцессора. При этом,

когда ведущий контроллер выдает на

локальную магистраль вектор

прерывания, формирователь внешней

магистрали данных отключается сигналом

с выхода

![]() БИС К1810ВН59А. Если же вектор прерывания

выдают ведомые контроллеры прерываний,

подключенные к внешней магистрали

данных, то формирователь магистрали

данных переключается обычным образом.

БИС К1810ВН59А. Если же вектор прерывания

выдают ведомые контроллеры прерываний,

подключенные к внешней магистрали

данных, то формирователь магистрали

данных переключается обычным образом.

Рисунок 20 — Второй вариант подключения ведущей и ведомых БИС контроллеров прерываний К1810ВН59А к ЦП К1810ВМ86, включенному в минимальный режим

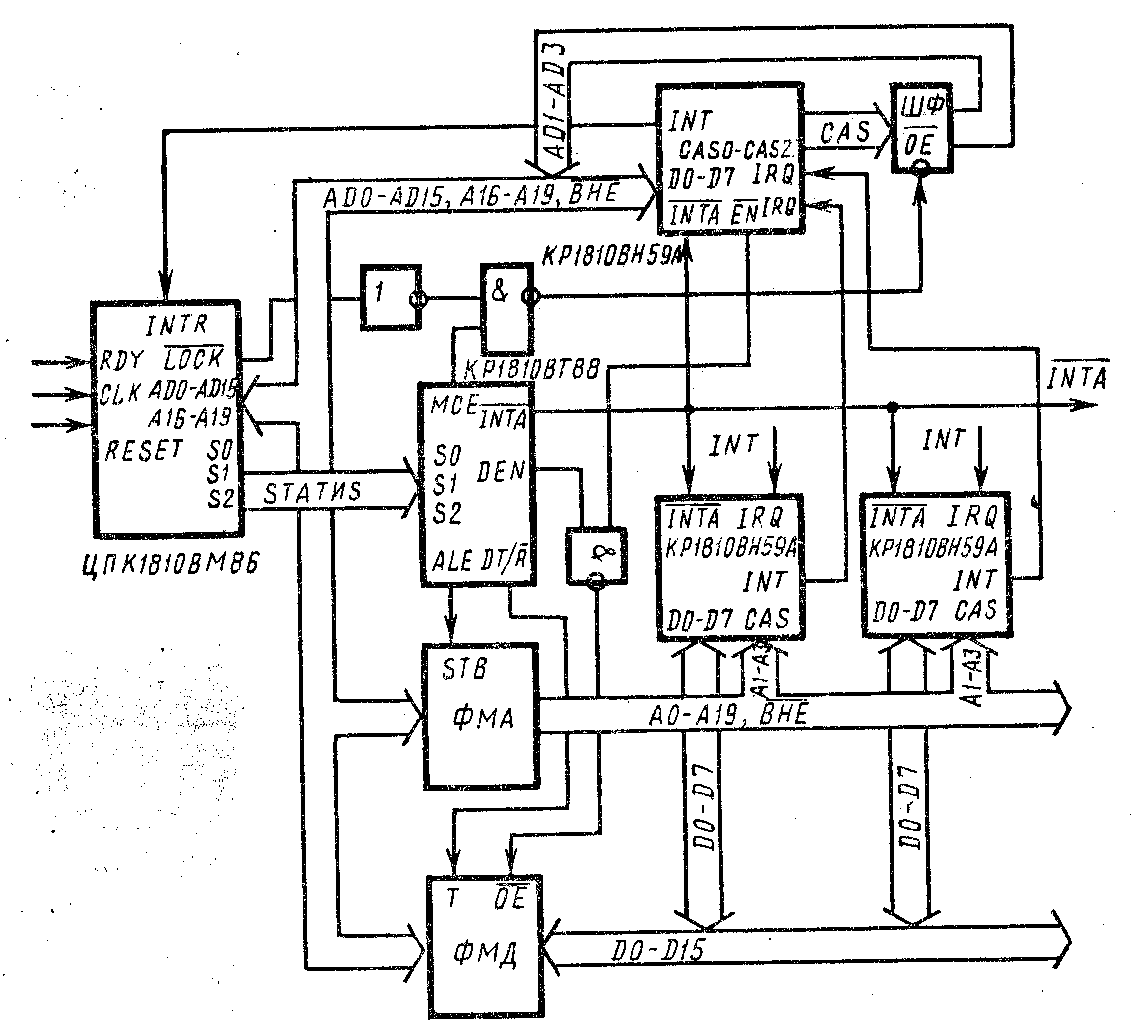

Подключение контроллера прерываний к локальной магистрали МП, работающего в максимальном режиме (рисунок 21), имеет некоторые особенности. Использование сигнала МСЕ системного контроллера (в режиме, когда вход IOВ = 0), активного на первом такте двух циклов подтверждения прерывания, позволяет выставлять на локальную магистраль МП код выбора ведомых контроллеров прерываний и запоминать его по сигналу ALE в регистрах-формирователях внешней магистрали адреса на протяжении всего цикла чтения вектора прерывания. Такой способ передачи сигналов каскадирования внешним контроллерам прерываний избавляет от необходимости введения трех дополнительных линий каскадирования CAS0—CAS2.

Рисунок 21 — Подключение ведущего и ведомого контроллеров прерываний К1810ВН59А к ЦП КР1810ВМ86, включенному в минимальный режим

2.9.5 Организация обмена данными по каналу прямого доступа к памяти (ПДП) микроЭВМ. В МПК серии К1810 для организации обмена данными по каналу ПДП применяют программируемый 4-канальный контроллер прямого доступа КПДП БИС К1810ВТ37. Эта микросхема является расширенным функциональным аналогом БИС КПДП КР58ОВТ57 и отличается более широкими возможностями программирования режимов работы всех четырех каналов ПДП.

При работе в минимальном режиме МП К1810ВМ86, аналогично МП БИС КР580ВМ80А, обрабатывает сигнал запроса захвата магистралей HOLD и вырабатывает ответный сигнал подтверждения и захвата HLDA, переводя локальную магистраль в третье состояние. Поэтому подключение КПДП К1810ВТ37 к МП К1810ВМ86, работающему в минимальном режиме, незначительно отличается от подключения БИС КПДП КР580ВТ57 к процессору КР580ВМ80А. Вариант включения БИС КПДП К1810ВТ37 показан на рисунке 22.

Рисунок 22 — Подключение контроллера прямого доступа к памяти БИС К1810ВТ37

Магистраль данных DB0—DB7 контроллера ПДП подключена непосредственно к разрядам AD8—AD15 локальной магистрали МП БИС К1810ВМ86. Такое включение позволяет использовать регистр магистрали адреса для фиксации разрядов А8—А15 адреса ПДП, выдаваемых БИС КПДП на шину данных на первом такте циклов ПДП. Разряды адреса А16—А19 в циклах обмена по каналу ПДП выдаются с дополнительного регистра с тремя состояниями на выходе. Информация в него может быть задана как программно, так и схемотехнически.

Для формирования шины управления МП БИС К1810ВМ86 используют мультиплексор К555КШ1 с тремя состояниями на выходе, позволяющий отключать сигналы управления МП в циклах ПДП, когда управление микропроцессорной системой берет на себя КПДП К1810ВТ37.

В данной схеме по каналу ПДП можно передавать информацию только побайтно, поэтому сигнал ВНЕ можно получить инверсией сигнала адреса А0. Для передачи по КПДП 16-разрядных слов за один цикл необходимо подключить разряды А0—А7 БИС КПДП к разрядам А0—А7 магистрали адреса соответственно и использовать отдельный регистр фиксации разрядов А8—А15 адреса ПДП, подключенный выходом к шине адреса А9-А16 также со смещением. При этом сигналы А0 и ВНЕ должны быть равны 0.

В

максимальном режиме захват магистралей

МП БИС К1810ВМ86 производится под управлением

двунаправленных сигналов запроса

—подтверждения захвата

![]() и

и

![]() .

Поэтому для подключения КПДП к МП,

работающему в максимальном режиме,

необходимо использование спе-циальной

схемы, преобразующей сигналы HOLD/HLDA

в

.

Поэтому для подключения КПДП к МП,

работающему в максимальном режиме,

необходимо использование спе-циальной

схемы, преобразующей сигналы HOLD/HLDA

в

![]() .

.

4 РАЗРБОТКА ПОДСИСТЕМЫ ВВОДА/ВЫВОДА, ПРЕРЫВАНИЙ, ПДП

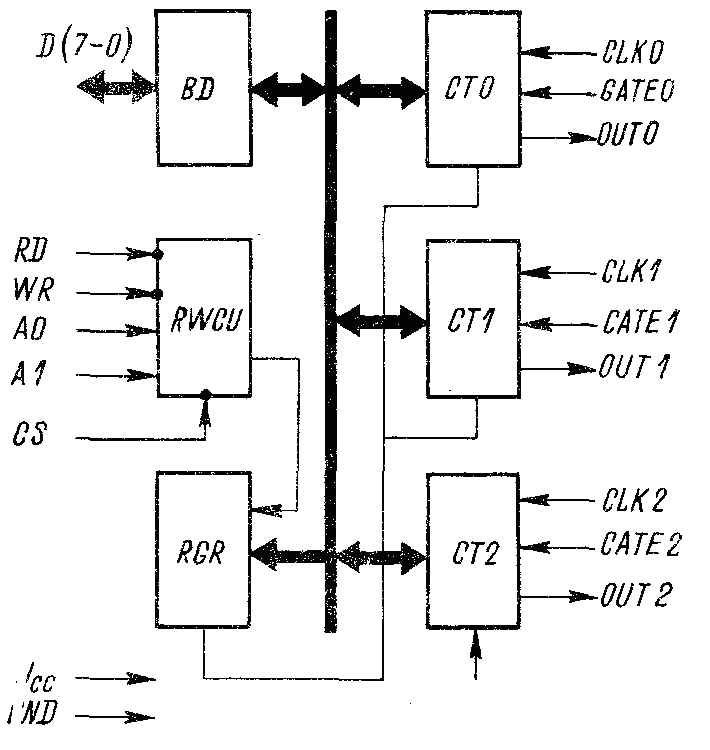

4.1 Программируемый таймер КР580ВИ53

БИС программируемого таймера КР58ОВИ53 предназначена для организации работы микропроцессорных систем в режиме реального времени и позволяет формировать сигналы с различными временными и частотными характеристи-ками.

Программируемый таймер (ПТ) имеет три независимых канала, каждый из которых содержит 16-разрядный вычитающий счетчик. Счетчики могут работать в двоичном или двоично-десятичном коде, с однобайтными или двухбайтными числами. Скорость счета программно изменяется от 0 до 2 МГц.

Упрощенная структурная схема ПТ приведена на рисунке 23. В состав БИС входят: буфер данных (ВD), предназначенный для обмена данными и управляющими словами между МП и ПТ; схема управления чтением-записью (RWCU), обеспечивающая выполнение операций ввода-вывода информации в ПТ; регистр управляющего слова (RGR), предназначенный для записи управляющих слов, задающих режимы работы счетчиков; счетчик каналов (СТ0 — СТ2).

Рисунок 23 — Структурная схема программируемого таймера КР580ВИ53

Назначение входных, управляющих сигналов ПТ указано при описании выводов микросхемы в таблице 11.

Таблица 11 — Описание выводов программируемого таймера.

-

Обозначение вывода

Номер контакта

Назначение вывода

D(7-0)

1; 2: 3:

4.5;6;7;8

Канал данных

RD

22

Сигнал «чтение»

WR

23

Сигнал «запись»

А0, A1

19; 20

Адресные входы, выбирающие один из каналов ПТ или управляющий регистр

CS

21

Выбор микросхемы

CLK0 - CLK2

9; 15; 18

Входы синхронизации счетчиков

САТЕ0-СЛТЕ2

11; 14; 16

Входы управлениясчетчиков

OUT0-OUT2

10; 13: 17

Выходные сигналы

UСС

24

Напряжение питания ( + 5В)

GND

12

Напряжения питания (0 В)

Подключение ПТ к шинам микропроцессора показано на рисунке 24. Установка режима работы каждого канала ПТ производится программно путем записи управляющего слова и начального значения содержимого счетчика (N) с помощью команд вывода (OUT).

Рисунок 24 — Схема подключение ПТ к шинам микропроцессора

Основные электрические параметры микросхемы КР58ОВИ53 при температуре окружающей среды (+25 … +10)°С приведены ниже:

Выходное напряжение логического нуля UOL, В < 0,4

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления IСС, мА < 115

Ток утечки на входах IIL, мкА —1,...,1

Ток утечки на выходах IOL, мкА —1,5,...,1,5