курсовой проект / Ключ-таблетка / Курсач 2 часть / 7

.doc7. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

По функциональному признаку различают постоянные запоминающие устройства (ПЗУ), хранящие информацию, предназначенную только для чтения, и оперативные запоминающие устройства (ОЗУ), предназначенные для записи, хранения и считывания цифровой информации.

ПЗУ относятся к комбинационным цифровым устройствам, ОЗУ относятся к цифровым устройствам последовательностного типа. ПЗУ сохраняют информацию при отключенном питании, т.е. обладают свойством энергонезависимости, в ОЗУ информация теряется при отключении питания.

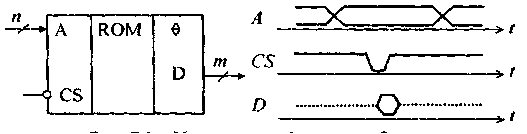

Постоянные запоминающие устройства (ПЗУ). ПЗУ по принципу работы являются преобразователями и-разрядного кода адреса ячейки А в »/- разрядный код хранящегося в ней слова D (рис. 7.1). Дан ные считы- ваютсяпри по даче разреша-Рис. 7.1 — Условное графическое обозначение ющего уровня ПЗУ и временные диаграммы его работы на вход CS.

Микросхемы ПЗУ по способу записи в них информации делятся на масочные (ROM — Read Only Memory), программируемые на заводе-изготовителе интегральных микросхем; однократно-программируемые (PROM — Programmable ROM) и .многократно-программируемые пользователем (репрограммируемые ПЗУ),

Для обеспечения возможности объединения по выходу при наращивании памяти все ПЗУ (также как и ОЗУ) имеют выходы с тремя состояниями ($) или открытый коллекторный выход (£).

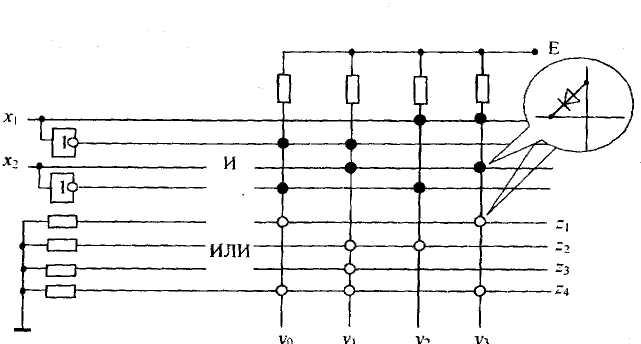

Схемотехническую реализацию ПЗУ масочного типа иллюстрирует рис.7.2. Схема имеет адресные входы х\, Х2, выходы содержимого ячеек памяти Г[-Г4, вывод для подключения источника питания Е и общий вывод. Верхняя часть схемы представляет собой полный дешифратор. Если разрядность адреса равна п, то в дешифраторе имеем 2« горизонтальных входных линий, на которых формируются входные переменные и их инверсии. Число вертикальных линий в полном дешифраторе равно 2". С помощью специальных масок программируется наличие или отсутствие ^-«-перехода в цепи связи вертикальных и горизонтальных шин матрицы. Размещение диодов матрицы И показано на рисунке жирными точками. Диоды ориентированы так, как показано на вынесенной в кружок части рисунка.

На вертикальных шинах матрицы реализуются логические функции уо= х\ лч }'] = xi хт, уг~ X] ж?, yi~ х, х% Каждому набору входных переменных, т.е. адресу ПЗУ, соответствует уровень логической единицы на одной из

Рис. 7.2 - ПЗУ масочного типа

вертикальных линий и логического 0 на всех остальных. Диоды дешифратора реализуют матрицу И.

В нижней части рисунка диоды реализуют матрицу ИЛИ. Количество горизонтальных линий соответствует разрядности слова, записанного по каждому адресу. Наличие диода формирует 1 в соответствующем бите выходного слова, отсутствие диода - 0. В ПЗУ схема дешифратора неизменна, а программируется матрица связей ИЛИ (они удобны для реализации преобразователей кода).

В ПЛМ (программируемых логических матрицах, подробнее см. главу 14) программируются обе матрицы (И и ИЛИ). ПЛМ удобны для реализации сложных логических функций, их преимущества особенно заметны при большом числе входных переменных.

В данном примере реализовано ПЗУ, карта прошивки которого представлена ниже в таблице.

Один из принципов построения однократно программируемого ПЗУ с организацией 32x8 (микросхема KI55PE3) показан на рис. 7.3. К каждому из 52 выходов дешифратора подключен восьмиэмиттерный транзистор. До программирования по любому адресу А считываете» байт нулей (А, - £>7). По-