- •Введение

- •1 АналиЗтехнического задания

- •2 Разработка процессорного модуля

- •2.2 Вспомогательные интерфейсные микросхемы

- •3 Разработка подсистемы памяти

- •3.2 Постоянное запоминающее устройство к541ре1

- •4.1 Подбор подсистемы ввода/вывода

- •4.2 Контролер прерываний

- •4.3 Контроллер прямого доступа к памяти

- •4.4 Программируемый таймер

- •4.5 Аналогово-цифровой преобразователь к572вп1

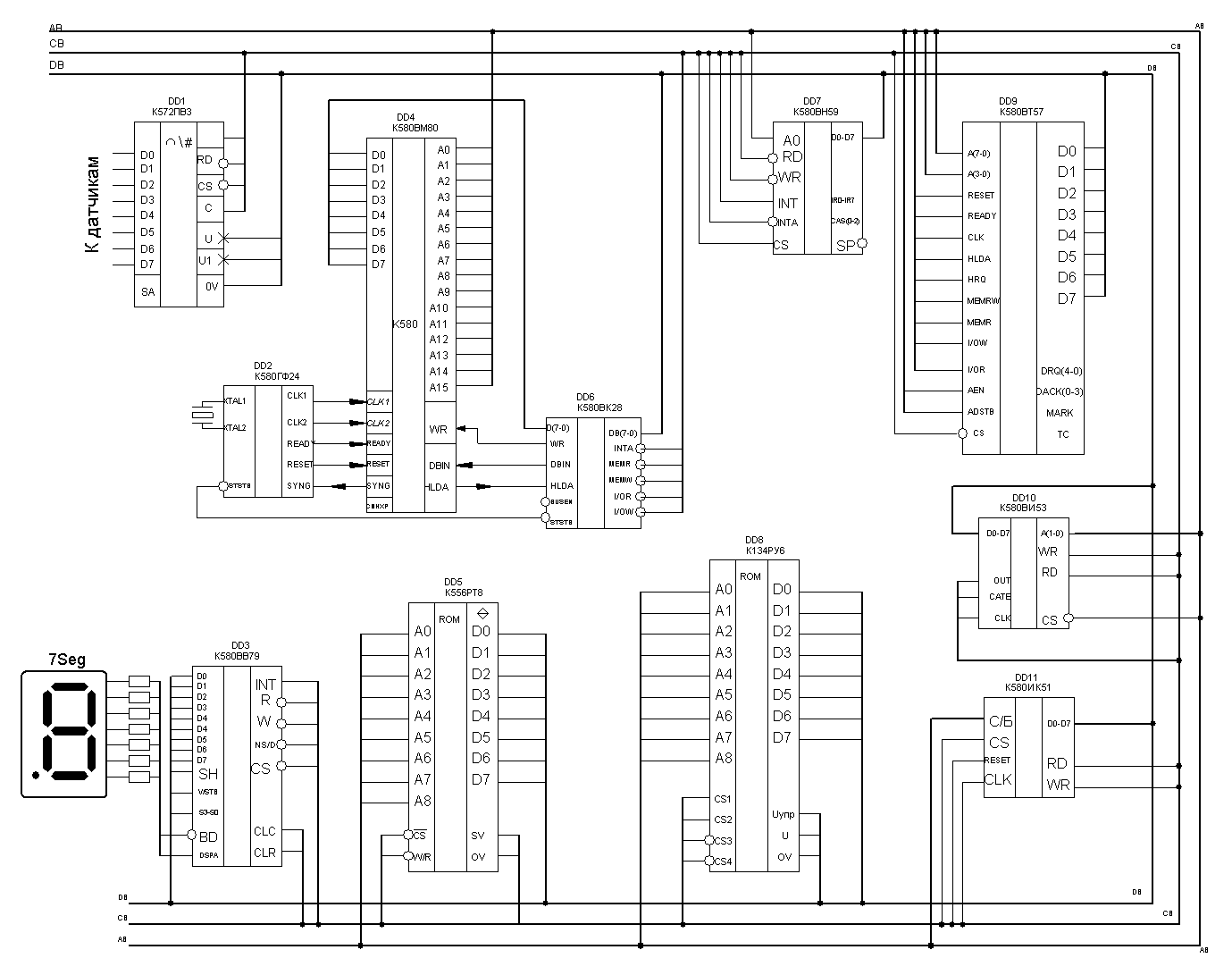

- •6. Реализация микропроцессора к580вм80 в системе

4.3 Контроллер прямого доступа к памяти

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначена для организации высоко-коростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства. Контроллер прямого доступа к памяти (КПДП) генерирует управляющие сигналы, необходимые для организации обмена. КПДП содержит четыре канала прямого доступа, каждый из которых обеспечивает передачу блок данных размером до 16К байт с произвольным начальным адресом в диапазоне от 0 до 64К байт.

У прощенная

структурная схема КПДП приведена па

рисунке 17. В состав БИС входят:

двунаправленный двустабильный буфер

данных (ВD), предначен-ный

для обмена информацией между МП и КПДП;

схема управления чтением/записью(RWCU), адресующая

внутренние регистры КПДП и управляющая

обменом по шинеD(7-0); блок

управления (CU), содержащий

регистры режима и Рисунок 18 - Структурная

схема контроллера прямого доступа к

памяти

прощенная

структурная схема КПДП приведена па

рисунке 17. В состав БИС входят:

двунаправленный двустабильный буфер

данных (ВD), предначен-ный

для обмена информацией между МП и КПДП;

схема управления чтением/записью(RWCU), адресующая

внутренние регистры КПДП и управляющая

обменом по шинеD(7-0); блок

управления (CU), содержащий

регистры режима и Рисунок 18 - Структурная

схема контроллера прямого доступа к

памяти

состояния

КПДП и обеспечивающий последовательность

операций, необходимую для организации

режима прямого доступа к памяти; блок

управления приоритетами(PCU),

обеспечивающий определенный порядок

обслуживания запросов внешних

устройств; четыре канала прямого доступа(СН0 –СН3), каждый из которых

содержит регистр адреса ячейки памяти,

с которой производится обмен, и счетчик

циклов обмена, два старших разряда

которого отведены для задания операции

обмена.

состояния

КПДП и обеспечивающий последовательность

операций, необходимую для организации

режима прямого доступа к памяти; блок

управления приоритетами(PCU),

обеспечивающий определенный порядок

обслуживания запросов внешних

устройств; четыре канала прямого доступа(СН0 –СН3), каждый из которых

содержит регистр адреса ячейки памяти,

с которой производится обмен, и счетчик

циклов обмена, два старших разряда

которого отведены для задания операции

обмена.

П ри

подключении КПДП к шинам микроЭВМ

младший байт адреса памяти выдается

по линиямА (3-0) и А (7-4), старший

байт - через шинуD(7-0), по

этому КПДП обычно подключается вместе

с буферным регистром. Схема подключения

КПДП к системной шине с использованием

буферного регистра К589ИР12 показана

на рисунке 18.

ри

подключении КПДП к шинам микроЭВМ

младший байт адреса памяти выдается

по линиямА (3-0) и А (7-4), старший

байт - через шинуD(7-0), по

этому КПДП обычно подключается вместе

с буферным регистром. Схема подключения

КПДП к системной шине с использованием

буферного регистра К589ИР12 показана

на рисунке 18.

Рисунок 19 - Схема подключения контроллера прямого доступа к памяти к системной шине

Рисунок 20 - цоколевка КР580ВТ57

Таблица

9

– Назначение выводов КР580ВТ57

Таблица

9

– Назначение выводов КР580ВТ57

|

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

Состояние | |

|

англ. |

рус. | ||||

|

1 |

RDIO |

ЧТВ |

Вход/выход |

Чтение ввода/вывода |

0,1 |

|

2 |

WR IO |

ЗПВ |

Вход/выход |

Запись ввода/вывода |

0,1 |

|

3 |

RD |

ЧТП |

Выход |

Чтение памяти |

0,1 |

|

4 |

WR |

ЗПП |

Выход |

Запись памяти |

0,1 |

|

5 |

М128 |

М128 |

Выход |

Модуль 128 |

0,1 |

|

6 |

RDY |

ГТ |

Вход |

Сигнал «Готовность» |

0,1 |

|

7 |

HLDA |

ПЗХ |

Вход |

Сигнал «Подтверждение захвата» |

0,1 |

|

8 |

STBA |

СТБА |

Выход |

Стробирующий сигнал адреса |

0,1 |

|

9 |

АЕ |

РА |

Выход |

Разрешение адреса |

0,1 |

|

10 |

HRQ |

ЗЗХВ |

Выход |

Запрос захвата |

0,1 |

|

11 |

CS |

ВМ |

Вход |

Выбор микросхемы |

0,1 |

|

12 |

С |

Т |

Вход |

Тактовый сигнал |

0,1 |

|

13 |

SR |

УСТ |

Вход |

Сигнал «Установка» |

0,1 |

|

25,24, 14, 15 |

DACK0—DACK3 |

ППДП |

Выходы |

Подтверждение прямого доступа к памяти каналов о-з |

0,1 |

|

19,18, 17, 16 |

DRQ0—DRQ3 |

ЗПДП |

Входы |

Запрос прямого доступа к памяти каналов 0—3 |

0,1 |

|

20 |

GND |

Общ |

|

Общий |

|

|

30,29, 28 27,26,23, 22, 21 |

D0—D7 |

Д0-Д7 |

Входы/выходы |

Канал данных |

0,1 |

|

31 |

Ucc |

|

— |

Напряжение питания |

|

|

32—35 |

АО—АЗ |

АО—АЗ |

Входы/выходы |

Канал адреса |

0,1,z |

|

36 |

ТС |

КСЧ |

Выход |

Конец счета |

0,1 |

|

37-40 |

А4-А7 |

А4-А7 |

Выходы |

Канал адреса |

0,1 |