- •Введение

- •1 АналиЗтехнического задания

- •2 Разработка процессорного модуля

- •2.2 Вспомогательные интерфейсные микросхемы

- •3 Разработка подсистемы памяти

- •3.2 Постоянное запоминающее устройство к541ре1

- •4.1 Подбор подсистемы ввода/вывода

- •4.2 Контролер прерываний

- •4.3 Контроллер прямого доступа к памяти

- •4.4 Программируемый таймер

- •4.5 Аналогово-цифровой преобразователь к572вп1

- •6. Реализация микропроцессора к580вм80 в системе

3 Разработка подсистемы памяти

3.1

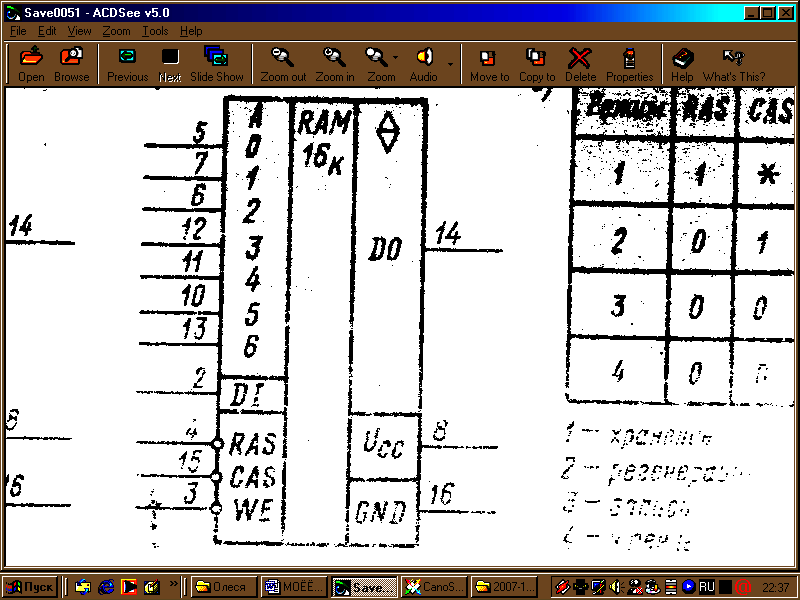

Оперативное запоминающее устройство

КР565РУ6

3.1

Оперативное запоминающее устройство

КР565РУ6

Микросхемы серии К565 представляют собой оперативные запоминающие устройства с произвольной выборкой динамического типа, изготавливаются по n– канальной МОП – технологии с кремниевыми затворами и двумя типами транзисторов (с индивидуальным и встроенным каналом) и предназначены для построения накопителей ОЗУ большой емкости.

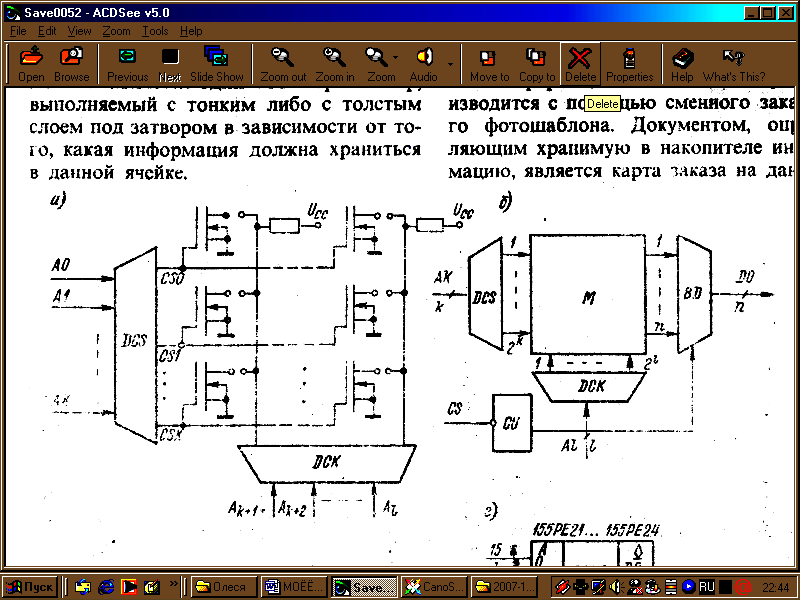

В ПЗУ запоминающие элементы объединяются в двухкоординатную матрицу, образованную при пересечении совокупности входных (чисел) и выходных (разрядов) информационных шин. В местах пересечения шин могут быть включены диоды, биполярные транзисторы и МОП – транзисторы. Запоминающим элементом накопителя ПЗУ является один МОП – транзистор, выполняемый с тонким либо с толстым слоем под затвором в зависимости от того, какая информация должна храниться в данной ячейке.

Рисунок 7 – Организация масочного ПЗУ (а) и обобщенная логическая __структура (б) КР565РУ6

Рисунок 8 – Цоколевка корпуса К565РУ6

Таблица 4 – Назначение выводов К565РУ6

|

Номера контактов |

Обозначение |

Назначение |

Тип сигнала |

Состояние | |

|

англ. |

рус. | ||||

|

1-8, 19, 22, 23 |

А0 – А6 |

А0-А6 |

Адресная шина |

Вход |

1,0 |

|

9-11, 13-17 |

D0 |

Д0 |

Считывание информации |

Вх/вых. |

0,1,z |

|

12 |

DI |

|

Запись информации |

|

|

|

24 |

Ucc |

|

Напряжение питания +5В |

|

|

|

18 |

RAS |

|

Выбор адреса строк |

Вх/вых. |

0,1,z |

|

20 |

CAS |

|

Выбор адреса столбцов |

Вх/вых. |

0,1,z |

|

|

WE |

|

Сигнал запись/чтение |

|

|

Регенерация информации в динамических ячейках памяти осуществляется за 128 циклов путем обращения к каждой из 128 строк не ранее, чем через каждые 2 мс перебором адресов А(0-6). Регенерация может быть осуществлена в любом из режимов ОЗУ, однако наиболее просто ее выполнить в режиме регенерации по сигналу RAS, когда сигналCASнаходиться в неактивном высоком логическом состоянии.

Основные параметры ОЗУ:

Напряжение питания, Uсс В 4,5-5,5;

Ток потребления, мА:

Динамический ICCAV <45(27);

хранения ICCS <3,2;

Входное

напряжение, В:

Входное

напряжение, В:

высокого уровня UIN 2,4-6,0;

низкого уровня UIL -1,0…+0,8;

Выходное напряжение, В:

высокого уровня UOHприIOH= -2 мА >2,4;

низкого уровня UOL при IOL= 4 мА <0,4;

Время выборки относительно сигнала выбора адреса столбцов tCAS, нс 70.

Подробная схема подключения ОЗУ к шинам адреса и данных посредством буферного регистра и шинного формирователя будет представлена в пункте разработки уточненной схемы МП БИС, сигналы и входы с помощью которых производиться подключение микросхемы будут указаны в пункте подбора буферного регистра и шинного формирователя.

БР

ША

ОЗУ

ФШ

ШД

Рисунок 9 – Подключение ОЗУ к шинам адреса и данных