- •Введение

- •1 АналиЗтехнического задания

- •2 Разработка процессорного модуля

- •2.2 Вспомогательные интерфейсные микросхемы

- •3 Разработка подсистемы памяти

- •3.2 Постоянное запоминающее устройство к541ре1

- •4.1 Подбор подсистемы ввода/вывода

- •4.2 Контролер прерываний

- •4.3 Контроллер прямого доступа к памяти

- •4.4 Программируемый таймер

- •4.5 Аналогово-цифровой преобразователь к572вп1

- •6. Реализация микропроцессора к580вм80 в системе

2.2 Вспомогательные интерфейсные микросхемы

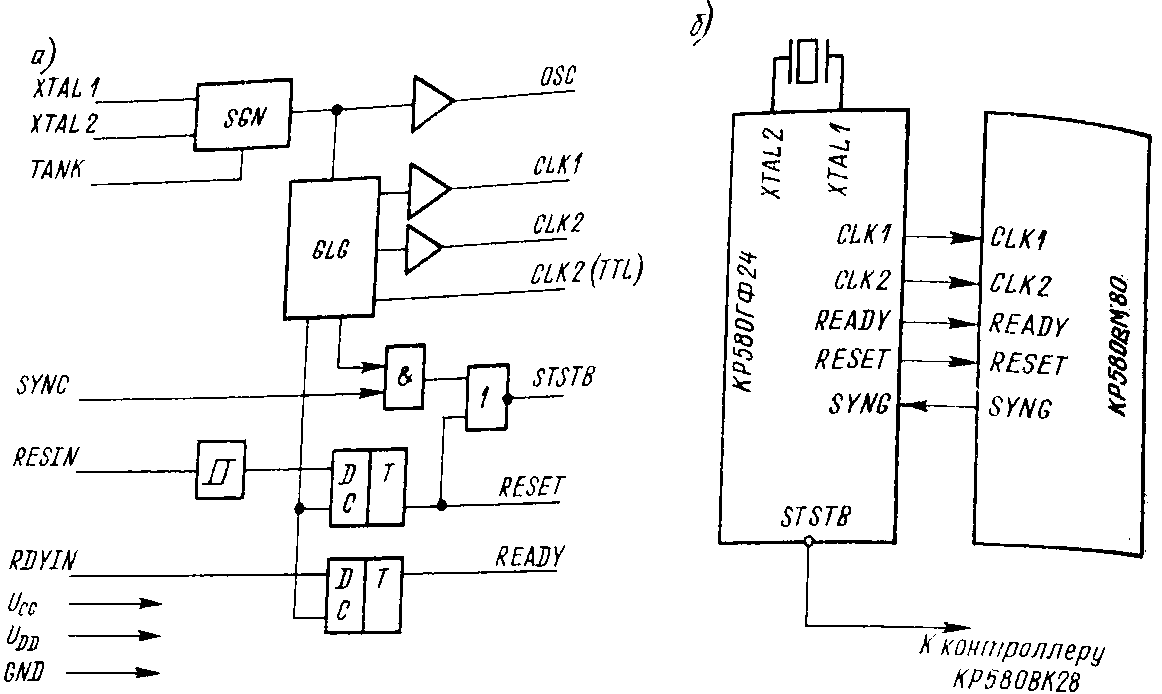

Разработка генератора тактовых импульсов

Генератор тактовых импульсов КР580ГФ24 предназначен для синхронизации микропроцессорных систем на основе комплекта К580. Генератор тактовых импульсов (ГТИ) формирует тактовые импульсы частотой до 2.5 мГн, амплитудой 12 В, тактовые импульсы амплитудой до 5 В для ТТЛ-схем, а также некоторые управляющие сигналы для микропроцессорной системы.

Структурная

схема ГТИ и подключение к МП представлены

на рисунке 3.

Структурная

схема ГТИ и подключение к МП представлены

на рисунке 3.

Рисунок 3 - Структурная схема и подключение ГТИ

ГТИ

состоит из задающего генератора(SGN),

генератора тактовых импульсов(GLG),

порогового элемента формирователей

и логических схем. Для работы ГТИ

необходимо подключение внешнего

кварцевого резонатора с частотой

колебаний в 9 раз большей, чем частота

выходных тактовых импульсов ГТИ.

ГТИ

состоит из задающего генератора(SGN),

генератора тактовых импульсов(GLG),

порогового элемента формирователей

и логических схем. Для работы ГТИ

необходимо подключение внешнего

кварцевого резонатора с частотой

колебаний в 9 раз большей, чем частота

выходных тактовых импульсов ГТИ.

Таблица

2 - Назначение выводов КР580ГФ24

Таблица

2 - Назначение выводов КР580ГФ24

|

Вывод |

Обозначение |

Тип сигнала |

Состояние |

Функциональное назначение | |

|

англ. |

рус. | ||||

|

1 |

RESET |

СБ |

Выход |

0,1,z |

Установка в исходное состояние мп |

|

2 |

RESIN |

РСБ |

вход |

0,1,z |

Вход для генерации сигнала «Сброс» |

|

3 |

RDYIN |

ГТ |

вход |

0,1 |

Сигнал «готовность» |

|

4 |

RDY |

ГТ |

выход |

0,1 |

Сигнал «готовность» |

|

5 |

SYN |

СИНХ |

вход |

0,1 |

Сигнал синхронизации |

|

6 |

C |

С |

выход |

0,1 |

Тактовый сигнал, синхронный с фазой С2 |

|

7 |

STB |

СТБ |

выход |

0,1 |

Стробирующий сигнал |

|

8 |

GND |

общ |

- |

- |

Общий |

|

9 |

UCC2 |

- |

- |

- |

Напряжение +12 В |

|

10 |

C2 |

С2 |

выход |

|

Тактовые сигналы фаза С2(+12В) |

|

11 |

C1 |

С1 |

выход |

|

Тактовые сигналы фаза С1(+12В) |

|

12 |

OSC |

ТТЛ |

выход |

|

Тактовые сигналы опорной частоты (ТТЛ) |

|

13 |

TANK |

ПКК |

- |

|

Вывод для подключения колебательного контура |

|

14 |

X1 |

ПРЗ |

- |

|

Вывод для подключения резонатора |

|

15 |

X2 |

ПРЗ |

- |

|

Вывод для подключения резонатора |

|

16 |

UCC1 |

5В |

- |

|

Напряжение +5V |

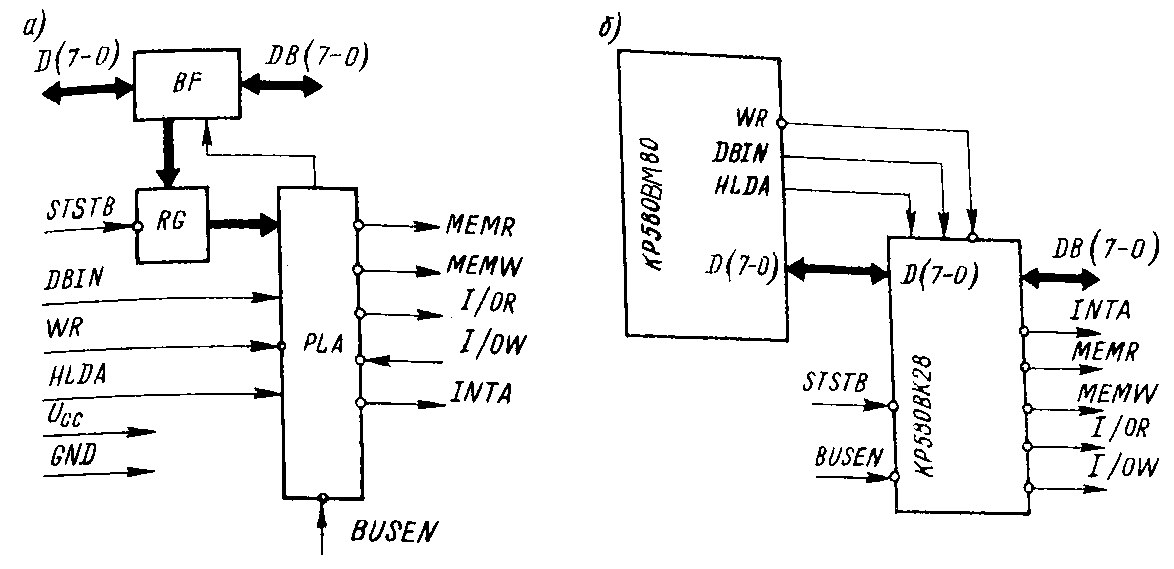

2.2.1 Разработка системного контроллера и шинного формирователя. Системный контроллер и шинный формирователь КР580ВК28 предназначен для фиксации слова-состояния МП, выработки системных управляющих сигналов, буферизации шины данных МП и управления направлением передачи.

Структурная схема системного контроллера и шинного формирователя

(СКФ) приведена на рисунке 4. В состав

СКФ входят: шинный формирователь-усилитель

(BF), обеспечивающий

увеличение нагрузочной способности

системной информационной шины; регистр

(RG) для записи и

хранения слова-состояния МП; комбинационная

схема(PLA) для формирования выходных управляющих

сигналов.

формирования выходных управляющих

сигналов.

Рисунок 4 - Структурная схема и подключение системного контроллера и шинного формирователя

Рисунок 5 – Условно-графическое обозначение К580ВА86

Таблица 3 — Описание выводов шинного формирователя КР580ВА86

|

Номер вывода |

Обозначение |

Назначение |

Тип сигнала |

Состояние | |

|

англ. |

рус. | ||||

|

1 – 8 |

А0 – А7 |

А0 – А7 |

Шина А |

вход/выход |

0,1 |

|

9 |

ОЕ |

РВ |

Разрешение выхода |

Вход |

0,1 |

|

10 |

GND |

|

Общий |

|

|

|

11 |

T |

НП |

Направление передачи |

вход/выход |

0,1 |

|

19 – 12 |

B0 – B7 |

Б0-Б7 |

Шина В |

вход/выход |

0,1 |

|

20 |

Ucc |

Осн.+5В |

+5 В |

|

|

2. 3 Упрощенная структурная схема

В

рассматриваемой цифровой системе, как

правило, информация передается от

одного узла вычислительной системы к

другому в виде двоичных сигналов. Если

информация передается из одного блока

в другой по одной линии путем представлени я

логических уравнений в виде последовательных

рядов, то под таким видом подразумевается

последовательную передачу информации.

Достоинством такого способа является

минимизация числа видов связи, но для

передачи слова изn

бит требуется n

тактов синхронизации. При параллельном

способе передачи информации каждый из

n

бит посылается по отдельной линии, а

сами линии упорядочиваются. Под шиной,

в этом случае подразумевается совокупность

линий, по которым передается информация.

Информация передается по шине параллельно

битами, а последовательно словами.

Каждый элемент данных считывается с

шины синхронно с системой синхронизации.

я

логических уравнений в виде последовательных

рядов, то под таким видом подразумевается

последовательную передачу информации.

Достоинством такого способа является

минимизация числа видов связи, но для

передачи слова изn

бит требуется n

тактов синхронизации. При параллельном

способе передачи информации каждый из

n

бит посылается по отдельной линии, а

сами линии упорядочиваются. Под шиной,

в этом случае подразумевается совокупность

линий, по которым передается информация.

Информация передается по шине параллельно

битами, а последовательно словами.

Каждый элемент данных считывается с

шины синхронно с системой синхронизации.

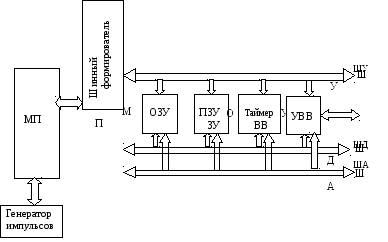

Остановим свой выбор на трехшинной организации конструкции микроЭВМ, представленной на рисунке 6.

Рисунок 6 - Трехшинная организация конструкции микропроцессорного устройства

В

такой схеме (организации системы)

различают 3 шины: управления, адресную

и данных.

В

такой схеме (организации системы)

различают 3 шины: управления, адресную

и данных.

По ШУ передаются служебные управляющие слова (сигналы синхронизации, чтения, запись, запросы на прерывание, подтверждение адреса и др.)

По шине адреса происходит передача микропроцессором адреса из ОЗУ в ПЗУ или устройств ввода/вывода, по шине данных - соответственно передача данных.

Раздельная ШД и ША характерны для большинства микроЭВМ. Выделение отдельно шин для всех управляющих сигналов, адресной информации и данных, упрощает организацию обмена информации между отельными компонентами и уменьшает время выполнения команд в микроЭВМ.