курсовой проект / таймер-- / 5

.doc5.3 Архитектура программируемого таймера КР580ВИ53

БИС программируемою таймера КР58ОВИ53 предназначена для организации работы микропроцессорных систем в режиме реального времени и позволяет формировать сигналы с различными временными и частотными характеристиками.

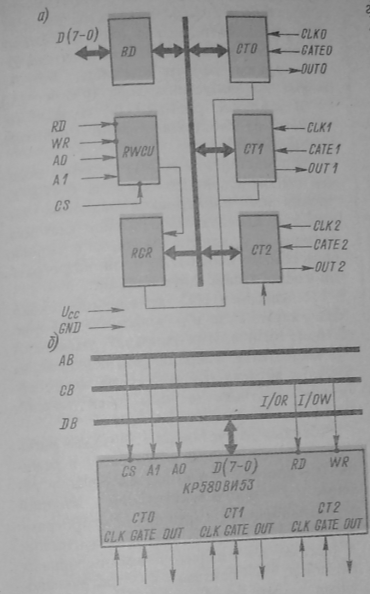

Программируемый таймер (ПТ) имеет три независимых канала, каждый из которых содержит 16-разрядный вычитающий счетчик. Счетчики могут работать двоичном или двоично-десятичном коде с однобайтными или двухбайтными числами. Упрощенная схема ПТ приведена на рисунке 13.

В состав БИС входит буфер данных (BD) для обмена данными и упраыляющими словами между МП и ПТ .Схема управления чтения записью, обеспечивающая выполнение операций ввода вывода информации в ПТ, регистр управляещего слова (RGR),предназначенный для записи слов, задающих режим счетчиков, счетчик каналов.

5.4Архитектура БИС программируемого контроллера прерываний КР580ВН59

БИС программируемого контроллера прерывания (ПКП) представляет собой устройство, реализующее до восьми уровней запросов на прерывание с возможностми программного маскирования и изменения дисциплины обслуживания прерываний. За счет каскадного включения БИС КР580ВН59 число уровней прерывания может быть расширено до 64.

Рисунок 13-Спряжение таймера с микропроцессором