- •INTRODUCTION TO ASICs

- •1.1 Types of ASICs

- •1.2 Design Flow

- •1.3 Case Study

- •1.4 Economics of ASICs

- •1.5 ASIC Cell Libraries

- •1.6 Summary

- •1.7 Problems

- •1.8 Bibliography

- •1.9 References

- •CMOS LOGIC

- •2.12 References

- •2.1 CMOS Transistors

- •2.2 The CMOS Process

- •2.3 CMOS Design Rules

- •2.4 Combinational Logic Cells

- •2.5 Sequential Logic Cells

- •2.6 Datapath Logic Cells

- •2.7 I/O Cells

- •2.8 Cell Compilers

- •2.9 Summary

- •2.10 Problems

- •2.11 Bibliography

- •ASIC LIBRARY DESIGN

- •3.1 Transistors as Resistors

- •3.3 Logical Effort

- •3.4 Library-Cell Design

- •3.5 Library Architecture

- •3.6 Gate-Array Design

- •3.7 Standard-Cell Design

- •3.8 Datapath-Cell Design

- •3.9 Summary

- •3.10 Problems

- •3.11 Bibliography

- •3.12 References

- •PROGRAMMABLE ASICs

- •4.1 The Antifuse

- •4.2 Static RAM

- •4.4 Practical Issues

- •4.5 Specifications

- •4.6 PREP Benchmarks

- •4.7 FPGA Economics

- •4.8 Summary

- •4.9 Problems

- •4.10 Bibliography

- •4.11 References

- •5.1 Actel ACT

- •5.2 Xilinx LCA

- •5.3 Altera FLEX

- •5.4 Altera MAX

- •5.5 Summary

- •5.6 Problems

- •5.7 Bibliography

- •5.8 References

- •6.1 DC Output

- •6.2 AC Output

- •6.3 DC Input

- •6.4 AC Input

- •6.5 Clock Input

- •6.6 Power Input

- •6.7 Xilinx I/O Block

- •6.8 Other I/O Cells

- •6.9 Summary

- •6.10 Problems

- •6.11 Bibliography

- •6.12 References

- •7.1 Actel ACT

- •7.2 Xilinx LCA

- •7.3 Xilinx EPLD

- •7.4 Altera MAX 5000 and 7000

- •7.5 Altera MAX 9000

- •7.6 Altera FLEX

- •7.7 Summary

- •7.8 Problems

- •7.9 Bibliography

- •7.10 References

- •8.1 Design Systems

- •8.2 Logic Synthesis

- •8.3 The Halfgate ASIC

- •8.3.4 Comparison

- •8.4 Summary

- •8.5 Problems

- •8.6 Bibliography

- •8.7 References

- •9.1 Schematic Entry

- •9.3 PLA Tools

- •9.4 EDIF

- •9.5 CFI Design Representation

- •9.6 Summary

- •9.7 Problems

- •9.8 Bibliography

- •9.9 References

- •VHDL

- •10.1 A Counter

- •10.2 A 4-bit Multiplier

- •10.3 Syntax and Semantics of VHDL

- •10.5 Entities and Architectures

- •10.6 Packages and Libraries

- •10.7 Interface Declarations

- •10.8 Type Declarations

- •10.9 Other Declarations

- •10.10 Sequential Statements

- •10.11 Operators

- •10.12 Arithmetic

- •10.13 Concurrent Statements

- •10.14 Execution

- •10.15 Configurations and Specifications

- •10.16 An Engine Controller

- •10.17 Summary

- •10.18 Problems

- •10.19 Bibliography

- •10.20 References

- •IEEE Language Reference Manual project

- •VERILOG HDL

- •11.1 A Counter

- •11.2 Basics of the Verilog Language

- •11.3 Operators

- •11.4 Hierarchy

- •11.5 Procedures and Assignments

- •11.6 Timing Controls and Delay

- •11.7 Tasks and Functions

- •11.8 Control Statements

- •11.9 Logic-Gate Modeling

- •11.10 Modeling Delay

- •11.11 Altering Parameters

- •11.12 A Viterbi Decoder

- •11.13 Other Verilog Features

- •11.14 Summary

- •11.15 Problems

- •11.16 Bibliography

- •11.17 References

- •12.2 A Comparator/MUX

- •12.3 Inside a Logic Synthesizer

- •12.6 VHDL and Logic Synthesis

- •12.8 Memory Synthesis

- •12.9 The Multiplier

- •12.10 The Engine Controller

- •12.13 Summary

- •12.14 Problems

- •12.15 Bibliography

- •12.16 References

- •SIMULATION

- •13.1 Types of Simulation

- •13.3 Logic Systems

- •13.4 How Logic Simulation

- •13.5 Cell Models

- •13.6 Delay Models

- •13.7 Static Timing Analysis

- •13.8 Formal Verification

- •13.9 Switch-Level Simulation

- •13.11 Summary

- •13.12 Problems

- •13.13 Bibliography

- •13.14 References

- •TEST

- •14.1 The Importance of Test

- •14.2 Boundary-Scan Test

- •14.3 Faults

- •14.4 Fault Simulation

- •14.6 Scan Test

- •14.7 Built-in Self-test

- •14.8 A Simple Test Example

- •14.10 Summary

- •14.11 Problems

- •14.12 Bibliography

- •14.13 References

- •15.1 Physical Design

- •15.3 System Partitioning

- •15.4 Estimating ASIC Size

- •15.5 Power Dissipation

- •15.6 FPGA Partitioning

- •15.7 Partitioning Methods

- •15.8 Summary

- •15.9 Problems

- •15.10 Bibliography

- •15.11 References

- •16.1 Floorplanning

- •16.2 Placement

- •16.3 Physical Design Flow

- •16.4 Information Formats

- •16.5 Summary

- •16.6 Problems

- •16.7 Bibliography

- •16.8 References

- •ROUTING

- •17.1 Global Routing

- •17.2 Detailed Routing

- •17.3 Special Routing

- •17.5 Summary

- •17.6 Problems

- •17.7 Bibliography

- •17.8 References

- •A.2 VHDL Syntax

- •A.3 BNF Index

- •A.5 References

- •B.2 Verilog HDL Syntax

- •B.3 BNF Index

- •B.4 Verilog HDL LRM

- •B.5 Bibliography

- •B.6 References

7.3 Xilinx EPLD

The Xilinx EPLD family uses an interconnect bus known as Universal Interconnection Module ( UIM ) to distribute signals within the FPGA. The UIM, shown in Figure 7.7 , is a programmable AND array with constant delay from any input to any output. In Figure 7.7 :

●C G is the fixed gate capacitance of the EPROM device.

●C D is the fixed drain parasitic capacitance of the EPROM device.

●C B is the variable horizontal bus ( bit line) capacitance.

●C W is the variable vertical bus ( word line) capacitance.

Figure 7.7 shows the UIM has 21 output connections to each FB. 1 Thus the

XC7272 UIM (with a 4 ¥ 2 array of eight FBs as shown in Figure 7.7 ) has 168 (8 ¥ 21) output connections. Most (but not all) of the nine I/O cells attached to each FB have two input connections to the UIM, one from a chip input and one feedback from the macrocell output. For example, the XC7272 has 18 I/O cells that are outputs only and thus have only one connection to the UIM, so n = (18 ¥ 8) 18 = 126 input connections. Now we can calculate the number of tracks in the UIM: the XC7272, for example, has H = 126 tracks and V = 168/2 = 84 tracks. The actual physical height, V , of the UIM is determined by the size of the FBs, and is close to the die height.

The UIM ranges in size with the number of FBs. For the smallest XC7236 (with a 2 ¥ 2 array of four FBs), the UIM has n = 68 inputs and 84 outputs. For the XC73108 (with a 6 ¥ 2 array of 12 FBs), the UIM has n = 198 inputs. The UIM is a large array with large parasitic capacitance; it employs a highly optimized structure that uses EPROM devices and a sense amplifier at each output. The signal swing on the UIM uses less than the full V DD = 5 V to reduce the interconnect delay.

1. 1994 data book p. 3-62 and p. 3-78.

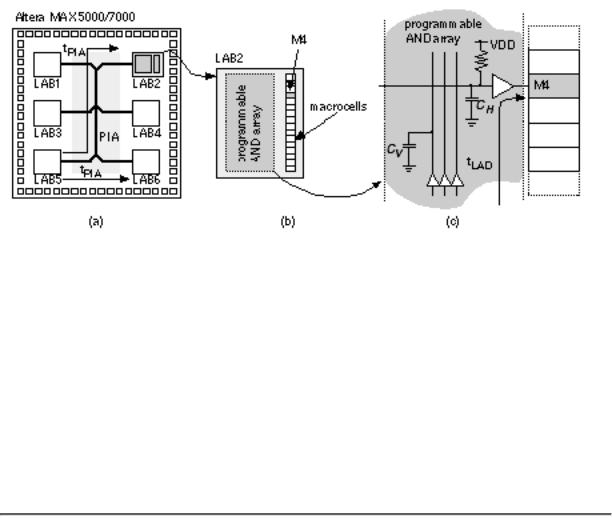

7.4 Altera MAX 5000 and 7000

Altera MAX 5000 devices (except the EPM5032, which has only one LAB) and all MAX 7000 devices use a Programmable Interconnect Array ( PIA ), shown in Figure 7.8 . The PIA is a cross-point switch for logic signals traveling between LABs. The advantages of this architecture (which uses a fixed number of connections) over programmable interconnection schemes (which use a variable number of connections) is the fixed routing delay. An additional benefit of the simpler nature of a large regular interconnect structure is the simplification and improved speed of the placement and routing software.

FIGURE 7.8 A simplified block diagram of the Altera MAX interconnect scheme. (a) The PIA (Programmable Interconnect Array) is deterministic delay is independent of the path length. (b) Each LAB (Logic Array Block) contains a programmable AND array. (c) Interconnect timing within a LAB is also fixed.

Figure 7.8 (a) illustrates that the delay between any two LABs, t PIA , is fixed. The delay between LAB1 and LAB2 (which are adjacent) is the same as the delay between LAB1 and LAB6 (on opposite corners of the die). It may seem rather strange to slow down all connections to the speed of the longest possible connection a large penalty to pay to achieve a deterministic architecture. However, it gives Altera the opportunity to highly optimize all of the connections since they are completely fixed.

7.5 Altera MAX 9000

Figure 7.9 shows the Altera MAX 9000 interconnect architecture. The size of the MAX 9000 LAB arrays varies between 4 ¥ 5 (rows ¥ columns) for the EPM9320 and 7 ¥ 5 for the EPM9560. The MAX 9000 is an extremely coarse-grained architecture, typical of complex PLDs, but the LABs themselves have a finer structure. Sometimes we say that complex PLDs with arrays (LABs in the Altera MAX family) that are themselves arrays (of macrocells) have a dual-grain architecture .

FIGURE 7.9 The Altera MAX 9000 interconnect scheme. (a) A 4 ¥ 5 array of Logic Array Blocks (LABs), the same size as the EMP9400 chip. (b) A simplified block diagram of the interconnect architecture showing the connection of the FastTrack buses to a LAB.

In Figure 7.9 (b), boxes A, B, and C represent the interconnection between the FastTrack buses and the 16 macrocells in each LAB:

●Box A connects a macrocell to one row channel.

●Box B connects three column channels to two row channels.

●Box C connects a macrocell to three column channels.

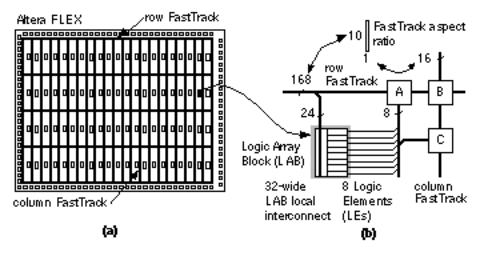

7.6 Altera FLEX

Figure 7.10 shows the interconnect used in the Altera FLEX family of complex PLDs. Altera refers to the FLEX interconnect and MAX 9000 interconnect by the same name, FastTrack, but the two are different because the granularity of the logic cell arrays is different. The FLEX architecture is of finer grain than the MAX arrays because of the difference in programming technology. The FLEX horizontal interconnect is much denser (at 168 channels per row) than the vertical interconnect (16 channels per column), creating an aspect ratio for the interconnect of over 10:1 (168:16). This imbalance is partly due to the aspect ratio of the die, the array, and the aspect ratio of the basic logic cell, the LAB.

FIGURE 7.10 The Altera FLEX interconnect scheme. (a) The row and column FastTrack interconnect. The chip shown, with 4 rows ¥ 21 columns, is the same size as the EPF8820. (b) A simplified diagram of the interconnect architecture showing the connections between the FastTrack buses and a LAB. Boxes A, B, and C represent the bus-to-bus connections.

As an example, the EPF8820 has 4 rows and 21 columns of LABs ( Figure 7.10 a). Ignoring, for simplicity s sake, what happens at the edge of the die we can total the routing channels as follows:

●Horizontal channels = 4 rows ¥ 168 channels/row = 672 channels.

●Vertical channels = 21 rows ¥ 16 channels/row = 336 channels.

It appears that there is still approximately twice (672:336) as much interconnect capacity in the horizontal direction as the vertical. If we look inside the boxes A, B, and C in Figure 7.10 (b) we see that for individual lines on each bus:

●Box A connects an LE to two row channels.

●Box B connects two column channels to a row channel.

●Box C connects an LE to two column channels.

There is some dependence between boxes A and B since they contain MUXes rather than direct connections, but essentially there are twice as many connections to the column FastTrack as the row FastTrack, thus restoring the balance in interconnect capacity.