- •INTRODUCTION TO ASICs

- •1.1 Types of ASICs

- •1.2 Design Flow

- •1.3 Case Study

- •1.4 Economics of ASICs

- •1.5 ASIC Cell Libraries

- •1.6 Summary

- •1.7 Problems

- •1.8 Bibliography

- •1.9 References

- •CMOS LOGIC

- •2.12 References

- •2.1 CMOS Transistors

- •2.2 The CMOS Process

- •2.3 CMOS Design Rules

- •2.4 Combinational Logic Cells

- •2.5 Sequential Logic Cells

- •2.6 Datapath Logic Cells

- •2.7 I/O Cells

- •2.8 Cell Compilers

- •2.9 Summary

- •2.10 Problems

- •2.11 Bibliography

- •ASIC LIBRARY DESIGN

- •3.1 Transistors as Resistors

- •3.3 Logical Effort

- •3.4 Library-Cell Design

- •3.5 Library Architecture

- •3.6 Gate-Array Design

- •3.7 Standard-Cell Design

- •3.8 Datapath-Cell Design

- •3.9 Summary

- •3.10 Problems

- •3.11 Bibliography

- •3.12 References

- •PROGRAMMABLE ASICs

- •4.1 The Antifuse

- •4.2 Static RAM

- •4.4 Practical Issues

- •4.5 Specifications

- •4.6 PREP Benchmarks

- •4.7 FPGA Economics

- •4.8 Summary

- •4.9 Problems

- •4.10 Bibliography

- •4.11 References

- •5.1 Actel ACT

- •5.2 Xilinx LCA

- •5.3 Altera FLEX

- •5.4 Altera MAX

- •5.5 Summary

- •5.6 Problems

- •5.7 Bibliography

- •5.8 References

- •6.1 DC Output

- •6.2 AC Output

- •6.3 DC Input

- •6.4 AC Input

- •6.5 Clock Input

- •6.6 Power Input

- •6.7 Xilinx I/O Block

- •6.8 Other I/O Cells

- •6.9 Summary

- •6.10 Problems

- •6.11 Bibliography

- •6.12 References

- •7.1 Actel ACT

- •7.2 Xilinx LCA

- •7.3 Xilinx EPLD

- •7.4 Altera MAX 5000 and 7000

- •7.5 Altera MAX 9000

- •7.6 Altera FLEX

- •7.7 Summary

- •7.8 Problems

- •7.9 Bibliography

- •7.10 References

- •8.1 Design Systems

- •8.2 Logic Synthesis

- •8.3 The Halfgate ASIC

- •8.3.4 Comparison

- •8.4 Summary

- •8.5 Problems

- •8.6 Bibliography

- •8.7 References

- •9.1 Schematic Entry

- •9.3 PLA Tools

- •9.4 EDIF

- •9.5 CFI Design Representation

- •9.6 Summary

- •9.7 Problems

- •9.8 Bibliography

- •9.9 References

- •VHDL

- •10.1 A Counter

- •10.2 A 4-bit Multiplier

- •10.3 Syntax and Semantics of VHDL

- •10.5 Entities and Architectures

- •10.6 Packages and Libraries

- •10.7 Interface Declarations

- •10.8 Type Declarations

- •10.9 Other Declarations

- •10.10 Sequential Statements

- •10.11 Operators

- •10.12 Arithmetic

- •10.13 Concurrent Statements

- •10.14 Execution

- •10.15 Configurations and Specifications

- •10.16 An Engine Controller

- •10.17 Summary

- •10.18 Problems

- •10.19 Bibliography

- •10.20 References

- •IEEE Language Reference Manual project

- •VERILOG HDL

- •11.1 A Counter

- •11.2 Basics of the Verilog Language

- •11.3 Operators

- •11.4 Hierarchy

- •11.5 Procedures and Assignments

- •11.6 Timing Controls and Delay

- •11.7 Tasks and Functions

- •11.8 Control Statements

- •11.9 Logic-Gate Modeling

- •11.10 Modeling Delay

- •11.11 Altering Parameters

- •11.12 A Viterbi Decoder

- •11.13 Other Verilog Features

- •11.14 Summary

- •11.15 Problems

- •11.16 Bibliography

- •11.17 References

- •12.2 A Comparator/MUX

- •12.3 Inside a Logic Synthesizer

- •12.6 VHDL and Logic Synthesis

- •12.8 Memory Synthesis

- •12.9 The Multiplier

- •12.10 The Engine Controller

- •12.13 Summary

- •12.14 Problems

- •12.15 Bibliography

- •12.16 References

- •SIMULATION

- •13.1 Types of Simulation

- •13.3 Logic Systems

- •13.4 How Logic Simulation

- •13.5 Cell Models

- •13.6 Delay Models

- •13.7 Static Timing Analysis

- •13.8 Formal Verification

- •13.9 Switch-Level Simulation

- •13.11 Summary

- •13.12 Problems

- •13.13 Bibliography

- •13.14 References

- •TEST

- •14.1 The Importance of Test

- •14.2 Boundary-Scan Test

- •14.3 Faults

- •14.4 Fault Simulation

- •14.6 Scan Test

- •14.7 Built-in Self-test

- •14.8 A Simple Test Example

- •14.10 Summary

- •14.11 Problems

- •14.12 Bibliography

- •14.13 References

- •15.1 Physical Design

- •15.3 System Partitioning

- •15.4 Estimating ASIC Size

- •15.5 Power Dissipation

- •15.6 FPGA Partitioning

- •15.7 Partitioning Methods

- •15.8 Summary

- •15.9 Problems

- •15.10 Bibliography

- •15.11 References

- •16.1 Floorplanning

- •16.2 Placement

- •16.3 Physical Design Flow

- •16.4 Information Formats

- •16.5 Summary

- •16.6 Problems

- •16.7 Bibliography

- •16.8 References

- •ROUTING

- •17.1 Global Routing

- •17.2 Detailed Routing

- •17.3 Special Routing

- •17.5 Summary

- •17.6 Problems

- •17.7 Bibliography

- •17.8 References

- •A.2 VHDL Syntax

- •A.3 BNF Index

- •A.5 References

- •B.2 Verilog HDL Syntax

- •B.3 BNF Index

- •B.4 Verilog HDL LRM

- •B.5 Bibliography

- •B.6 References

6.5 Clock Input

When we bring the clock signal onto a chip, we may need to adjust the logic level (clock signals are often driven by TTL drivers with a high current output capability) and then we need to distribute the clock signal around the chip as it is needed. FPGAs normally provide special clock buffers and clock networks. We need to minimize the clock delay (or latency), but we also need to minimize the clock skew.

6.5.1 Registered Inputs

Some FPGAs provide a flip-flop or latch that you can use as part of the I/O circuit (registered I/O). For other FPGAs you have to use a flip-flop or latch using the basic logic cell in the core. In either case the important parameter is the input setup time. We can measure the setup with respect to the clock signal at the flip-flop or the clock signal at the clock input pad. The difference between these two parameters is the clock delay.

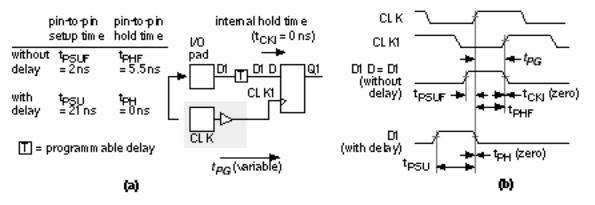

FIGURE 6.18 Clock input. (a) Timing model with values for a Xilinx XC4005-6. (b) A simplified view of clock distribution. (c) Timing diagram. Xilinx eliminates the variable internal delay t PG , by specifying a pin-to-pin setup time, t PSUFmin = 2 ns.

Figure 6.18 shows part of the I/O timing model for a Xilinx XC40005-6. 1

●t PICK is the fixed setup time for a flip-flop relative to the flip-flop clock.

●t skew is the variable clock skew , the signed delay between two clock edges.

●t PG is the variable clock delay or latency .

To calculate the flip-flop setup time ( t PSUFmin ) relative to the clock pad (which is the parameter system designers need to know), we subtract the clock delay, so that

t PSUF = t PICK t PG . (6.6)

The problem is that we cannot easily calculate t PG , since it depends on the clock distribution scheme and where the flip-flop is on the chip. Instead Xilinx specifies t PSUFmin directly, measured from the data pad to the clock pad; this time is called a pin-to-pin timing parameter . Notice t PSUF min = 2 ns ` t PICK t PG max = 1 ns.

Figure 6.19 shows that the hold time for a XC4005-6 flip-flop ( t CKI ) with respect to the flip-flop clock is zero. However, the pin-to-pin hold time including the clock delay is t PHF = 5.5 ns. We can remove this inconvenient hold-time restriction by delaying the input signal. Including a programmable delay allows Xilinx to guarantee the pin-to-pin hold time ( t PH ) as zero. The penalty is an

increase in the pin-to-pin setup time ( t PSU ) to 21 ns (from 2 ns) for the XC4005-6, for example.

FIGURE 6.19 Programmable input delay. (a) Pin-to-pin timing model with values from an XC4005-6. (b) Timing diagrams with and without programmable delay.

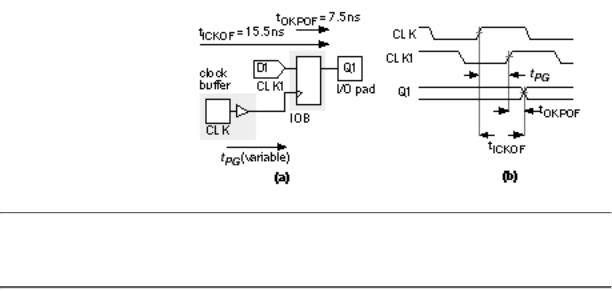

We also have to account for clock delay when we register an output. Figure 6.20 shows the timing model diagram for the clock-to-output delay.

FIGURE 6.20

Registered output.

(a)Timing model with values for an XC4005-6 programmed with the fast slew-rate option.

(b)Timing diagram.

1.The Xilinx XC4005-6 timing parameters are from the 1994 data book p. 2-50 to p. 2-53.

6.6 Power Input

The last item that we need to bring onto an FPGA is the power. We may need multiple VDD and GND power pads to reduce supply bounce or separate VDD pads for mixed-voltage supplies. We may also need to provide power for on-chip programming (in the case of antifuse or EPROM programming technology). The package type and number of pins will determine the number of power pins, which, in turn, affects the number of SSOs you can have in a design.

6.6.1 Power Dissipation

As a general rule a plastic package can dissipate about 1 W, and more expensive ceramic packages can dissipate up to about 2 W. Table 6.3 shows the thermal characteristics of common packages. In a high-speed (high-power) design the ASIC power consumption may dictate your choice of packages. Actel provides a formula for calculating typical dynamic chip power consumption of their FPGAs. The formula for the ACT 2 and ACT 3 FPGAs are complex; therefore we shall use the simpler formula for the ACT 1 FPGAs as an example 1 :

TABLE 6.3 Thermal characteristics of ASIC packages.

q JA /°CW 1 q JA /°CW 1

Package 2 Pin count Max. power P max /W

|

|

|

(still air) 3 , |

4 |

(still air) 5 |

|

|

|

|

||

CPGA |

84 |

|

33 |

|

32 38 |

CPGA |

100 |

|

35 |

|

|

CPGA |

132 |

|

30 |

|

|

CPGA |

175 |

|

25 |

16 |

|

CPGA |

207 |

|

22 |

|

|

CPGA |

257 |

|

15 |

|

|

CQFP |

84 |

|

40 |

|

|

CQFP |

172 |

|

25 |

|

|

PQFP |

100 |

1.0 |

55 |

|

56 75 |

PQFP |

160 |

1.75 |

33 |

|

30 33 |

PQFP |

208 |

2.0 |

33 |

27-32 |

|

VQFP |

80 |

|

68 |

|

|

PLCC |

44 |

|

52 |

44 |

|

PLCC |

68 |

|

45 |

|

28 35 |

PLCC |

84 |

1.5 |

44 |

PPGA |

132 |

|

33 34 |

Total chip power = 0.2 (N ¥ F1) + 0.085 (M ¥ F2) + 0.8 ( P ¥ F3) mW (6.7)

where

F1 = average logic module switching rate in MHz

F2 = average clock pin switching rate in MHz

F3 = average I/O switching rate in MHz

M = number of logic modules connected to the clock pin

N = number of logic modules used on the chip

P = number of I/O pairs used (input + output), with 50 pF load

As an example of a power-dissipation calculation, consider an Actel 1020B-2 with a 20 MHz clock. We shall initially assume 100 percent utilization of the 547 Logic Modules and assume that each switches at an average speed of 5 MHz. We shall also initially assume that we use all of the 69 I/O Modules and that each switches at an average speed of 5 MHz. Using Eq. 6.7 , the Logic Modules dissipate

P LM = (0.2)(547)(5) = 547 mW , (6.8)

and the I/O Module dissipation is

P IO = (0.8)(69)(5) = 276 mW . (6.9)

If we assume the clock buffer drives 20 percent of the Logic Modules, then the additional power dissipation due to the clock buffer is

P CLK = (0.085)(547)(0.2)(5) = 46.495 mW . (6.10)

The total power dissipation is thus

P D = (547 + 276 + 46.5) = 869.5 mW , (6.11)

or about 900 mW (with an accuracy of certainly no better than ± 100 mW).

Suppose we intend to use a very thin quad flatpack ( VQFP ) with no cooling (because we are trying to save area and board height). From Table 6.3 the thermal

resistance, q JA , is approximately 68 °CW 1 for an 80-pin VQFP. Thus the maximum junction temperature under industrial worst-case conditions (T A = 85 °C) will be

T J = (85 + (0.87)(68)) = 144.16 °C , (6.12)

(with an accuracy of no better than 10 °C). Actel specifies the maximum junction temperature for its devices as T Jmax = 150 °C (T Jmax for Altera is also 150 °C, for Xilinx T Jmax = 125°C). Our calculated value is much too close to the rated maximum for comfort; therefore we need to go back and check our assumptions for power dissipation. At or near 100 percent module utilization is not unreasonable for an Actel device, but more questionable is that all nodes and I/Os switch at 5 MHz.

Our real mistake is trying to use a VQFP package with a high q JA for a high-speed design. Suppose we use an 84-pin PLCC package instead. From Table 6.3 the thermal resistance, q JA , for this alternative package is

approximately 44 °CW 1 . Now the worst-case junction temperature will be a more reasonable

T J = (85 + (0.87)(44)) = 123.28 °C , (6.13)

It is possible to estimate the power dissipation of the Actel architecture because the routing is regular and the interconnect capacitance is well controlled (it has to be since we must minimize the number of series antifuses we use). For most other architectures it is much more difficult to estimate power dissipation. The exception, as we saw in Section 5.4 Altera MAX, are the programmable ASICs based on programmable logic arrays with passive pull-ups where a substantial part of the power dissipation is static.

6.6.2 Power-On Reset

Each FPGA has its own power-on reset sequence. For example, a Xilinx FPGA configures all flip-flops (in either the CLBs or IOBs) as either SET or RESET. After chip programming is complete, the global SET/RESET signal forces all flip-flops on the chip to a known state. This is important since it may determine the initial state of a state machine, for example.

1.1994 data book, p.1-9

2.CPGA = ceramic pin-grid array; CQFP = ceramic quad flatpack; PQFP = plastic quad flatpack; VQFP = very thin quad flatpack; PLCC = plastic leaded chip carrier; PPGA = plastic pin-grid array.

3.q JA varies with die size.

4.Data from Actel 1994 data book p. 1-9, p. 1-45, and p. 1-94.

5.Data from Xilinx 1994 data book p. 4-26 and p. 4-27.