- •Оглавление

- •1. Основные определения

- •1.1. Основные пояснения и термины

- •1.2. Пассивные элементы схемы замещения

- •1.3. Активные элементы схемы замещения

- •1.4. Основные определения, относящиеся к схемам

- •1.5. Режимы работы электрических цепей

- •1.6. Основные законы электрических цепей

- •2. Эквивалентные преобразования схем

- •2.1. Последовательное соединение элементов электрических цепей

- •2.2. Параллельное соединение элементов электрических цепей

- •2.3.Преобразование треугольника сопротивлений в эквивалентную звезду

- •2.4.Преобразование звезды сопротивлений в эквивалентный треугольник

- •3. Анализ электрических цепей постоянного тока с одним источником энергии

- •3.1. Расчет электрических цепей постоянного тока с одним источником методом свертывания

- •3.2. Расчет электрических цепей постоянного тока с одним источником методом подобия или методом пропорциональных величин

- •4. Анализ сложных электрических цепей с несколькими источниками энергии

- •4.1. Метод непосредственного применения законов Кирхгофа

- •4.2. Метод контурных токов

- •Порядок расчета

- •Рекомендации

- •4.3. Метод узловых потенциалов

- •4.4. Метод двух узлов

- •4.5. Метод эквивалентного генератора

- •5. Нелинейные электрические цепи постоянного тока

- •5.1. Основные определения

- •5.2. Графический метод расчета нелинейных цепей постоянного тока

- •6. Электрические цепи однофазного переменного тока

- •6.1. Основные определения

- •6.2. Изображения синусоидальных функций времени в векторной форме

- •6.3. Изображение синусоидальных функций времени в комплексной форме

- •6.4. Сопротивление в цепи синусоидального тока

- •6.5. Индуктивная катушка в цепи синусоидального тока

- •6.6. Емкость в цепи синусоидального тока

- •6.7. Последовательно соединенные реальная индуктивная катушка и конденсатор в цепи синусоидального тока

- •6.8. Параллельно соединенные индуктивность, емкость и активное сопротивление в цепи синусоидального тока

- •6.9. Резонансный режим в цепи, состоящей из параллельно включенных реальной индуктивной катушки и конденсатора

- •6.10. Мощность в цепи синусоидального тока

- •6.11. Баланс мощностей

- •6.12. Согласованный режим работы электрической цепи. Согласование нагрузки с источником

- •7. Трёхфазные цепи

- •7.1. Основные определения

- •7.2. Соединение в звезду. Схема, определения

- •7.3. Соединение в треугольник. Схема, определения

- •7.4. Расчет трехфазной цепи, соединенной звездой

- •7.5. Мощность в трехфазных цепях

- •8. Переходные процессы в линейных электрических цепях

- •8.1. Общая характеристика переходных процессов

- •8.2. Переходные процессы в цепях с одним реактивным элементом

- •9. Несинусоидальные периодические токи.

- •10. Электроника. Введение.

- •10.1. Полупроводниковые материалы.

- •10.2 Полупроводниковые диоды.

- •10.3. Биполярный транзистор

- •10.4. Полевые транзисторы.

- •10.5. Тиристоры.

- •11. Усилители электрических сигналов

- •11.1. Общие сведения, классификация и основные характеристики усилителя. Типовые функциональные каскады полупроводникового усилителя.

- •11.2. Анализ работы транзисторного усилителя. Понятие о классах усиления усилительных каскадов.

- •11.3. Температурная стабилизация режимов в транзисторных усилителях. Особенности работы усилителя на полевом транзисторе.

- •11.4. Избирательные усилители. Усилители мощности. Усилители постоянного тока.

- •11.5. Анализ дифференциального усилителя.

- •11.6. Операционный усилитель (оу). Схемы стабилизации и повышения входного сопротивления оу.

- •12. Источники вторичного электропитания

- •12.1. Классификация, состав и основные параметры.

- •12.2. Показатели выпрямителей однофазного тока.

- •12.3. Трехфазные выпрямители. Внешние характеристики выпрямителей.

- •12.4. Принцип работы выпрямителей на тиристорах.

- •12.5. Сглаживающие фильтры и оценка эффективности их работы.

- •12.6. Компенсационные стабилизаторы напряжения и преобразователи постоянного тока в переменный.

- •13. Основы цифровой электронной техники

- •13.1. Анализ логических устройств.

- •13.2. Логические операции и способы их аппаратурной реализации.

- •13.3. Сведения об интегральных логических микросхемах.

- •13.4. Схемотехнические и конструктивно-технологические особенности логических микросхем различных серий.

- •13.5. Принципы функционирования цифровых устройств комбинационной логики.

13.3. Сведения об интегральных логических микросхемах.

Комбинационные устройства в виде интегральных микросхем широко используют в цифровой электронике в качестве сумматоров, шифраторов, дешифраторов, мультиплексоров, демультиплексоров, компараторов (устройств сравнения) и т. п.

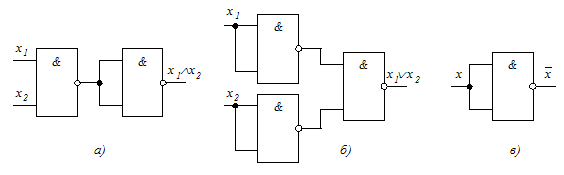

Схемотехника логических микросхемосновывается на преимущественном применении логических элементов универсального типа: И—НЕ и ИЛИ—НЕ. В качестве примера на рис. 13.3 показаны типичные для отечественной микроэлектроники функциональные схемы элементарных логических операций И, ИЛИ и НЕ (рис. 13.3, а, б, в), реализуемые на базовом элементе И—НЕ. По аналогичной методике можно выполнить указанные операции и на базовом элементе ИЛИ—НЕ.

Функциональная полнота базовых элементов позволяет в микросхемах одной серии реализовать логические устройства самого различного применения. Например, логические микросхемы серии 555 с базовым элементом И—НЕ насчитывают многие десятки наименований.

Параметры логических микросхем регламентируются ГОСТ 18683—73 и включают большое число показателей, основными из которых являются следующие:

уровни

напряжений, обеспечивающие

значения логических 0 и 1. Эти напряжения,

обозначаемые соответственно

![]() и

и

![]() должны существенно различаться для

предотвращения ложных переключений;

должны существенно различаться для

предотвращения ложных переключений;

помехоустойчивость,оцениваемая наибольшим значением напряжения помехи Uпом max, при котором не происходит изменений на выходе (ложных срабатываний);

потребляемый токInm(мощность Pnm);

время задержки tзпри переключениях логического устройства из одного состояния в другое, обусловливающее его быстродействие

Рис. 13.3. Реализация логических операций И (а), ИЛИ (6), НЕ (в) на элементах И—НЕ

13.4. Схемотехнические и конструктивно-технологические особенности логических микросхем различных серий.

В

цифровой электронике наибольшее

распространение получили потенциальные

логические элементы, управляемые

сигналами двух уровней (![]() и

и![]() ).

Эти элементы обладают достаточной

надежностью, высокой помехоустойчивостью

и хорошо приспособлены для изготовления

способами интегральной технологии.

Базовый логический элемент (например,

И—НЕ) состоит в этом случае из двух

компонентов: элемента, реализующего

логическое умножение (схемы совпадения),

и потенциального инвертора. При этом

предусматривается возможность подключения

к инвертору нескольких схем совпадения

для реализации функции ИЛИ. Дополнительные

электроды, предназначенные для подключения

к логическому элементу других однотипных

устройств, называют в логике расширительными.

).

Эти элементы обладают достаточной

надежностью, высокой помехоустойчивостью

и хорошо приспособлены для изготовления

способами интегральной технологии.

Базовый логический элемент (например,

И—НЕ) состоит в этом случае из двух

компонентов: элемента, реализующего

логическое умножение (схемы совпадения),

и потенциального инвертора. При этом

предусматривается возможность подключения

к инвертору нескольких схем совпадения

для реализации функции ИЛИ. Дополнительные

электроды, предназначенные для подключения

к логическому элементу других однотипных

устройств, называют в логике расширительными.

В зависимости от схемотехнических и конструктивно-технологических особенностей микросхем различают следующие их типы.

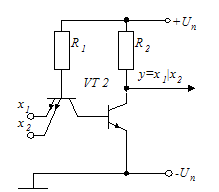

1. Транзисторно-транзисторная логика(ТТЛ) универсального типа (рис. 13.4) основана на использовании многоэмиттерного интегрального транзистора VT1, который допускает раздельное управление общей для всех эмиттеров коллекторной цепью. Если на все эмиттеры прибора подавать сигналы, соответствующие логической 1, то коллекторный переход транзистора VT1 оказывается смещенным в прямом направлении и на выходе инвертора, выполненного на транзисторе VT2, получают 0. Наоборот, при подаче хотя бы на один эмиттер 0 наблюдается насыщение многоэмиттерного транзистора VT1 и на выходе инвертора формируется 1. Таким образом, микросхемы ТТЛ реализуют положительную потенциальную логику, при которой нулевой уровень обеспечивается напряжениемU0≤0.4B, а единичныйU1≥2.4B.

Рис. 13.4. Упрощенная принципиальная электрическая схема базового логического элемента 2И— НЕ серии ТТЛ

Удовлетворительное быстродействие, высокая помехоустойчивость и принципиальная совместимость с микросхемами большинства типов (табл. 13.4) являются достоинствами ТТЛ. Однако значительная потребляемая мощность и малая критичность к перегрузкам требуют применения для питания таких микросхем относительно мощных и стабилизированных источников.

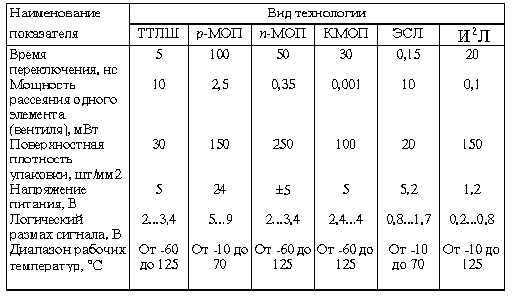

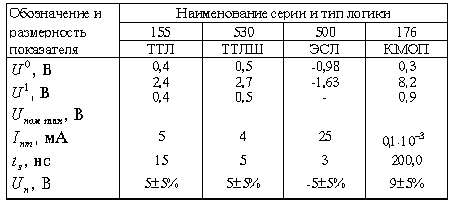

Таблица 13.4 Основные показатели некоторых логических микросхем

2. Транзисторно-транзисторная логика с диодами Шотки (ТТЛШ)может быть отнесена к разновидности ТТЛ. Здесь для повышения быстродействия транзисторы используют в ненасыщенном режиме, для чего их коллекторные переходы шунтируют диодами Шотки. В импульсном режиме эти диоды открываются раньше коллекторных р-n-переходов, существенно ускоряя процессы рассасывания неосновных носителей. Этим и обеспечивается значительно большее быстродействие микросхем с ТТЛШ по сравнению с ТТЛ (см. табл. 13.4).

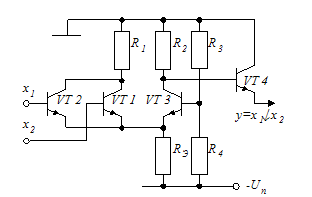

3. Эмиттерно-связанная логика(ЭСЛ), основанная на применении переключателя тока на транзисторахVT1,VT2,VT3 (рис. 13.5), относится к типу сверхскоростной. Высокое быстродействие микросхемы (малое время задержки распространенияtз) достигается использованием ненасыщенного режима работы транзисторов, снижением разности уровней напряженийU0иU1(логического перепада - разностью единичного и нулевого уровней напряжений) и применением на выходе эмиттерного повторителя (транзисторVT4), ускоряющего процессы переключения. Несмотря на отрицательную полярность напряжения питания, в элементе реализуется положительная логика. Недостатками микросхем ЭСЛ являются меньшая в сравнении с ТТЛ-схемами помехозащищенность и большая потребляемая мощность (см. табл.13.4).

Рис. 13.5. Упрощенная принципиальная электрическая схема базового логического элемента 2ИЛИ— НЕ серии ЭСЛ

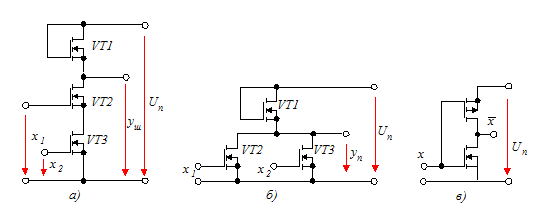

Рис. 13.6. Схемы включения полевых транзисторов в НСТЛ логике на n-канальных приборах при реализации логических операций И—НЕ (а) и ИЛИ—НЕ (б) и накомплементарных приборах при реализации логической операции НЕ (в)

4. Транзисторная логика с непосредственной связью(НСТЛ), реализуемая на полевых транзисторах двух типов: металл—оксид— полупроводник (МОП) или металл—нитридоксид—полупроводник (МНОП), — является экономичной. В зависимости от типа полевых транзисторов, используемых в микросхемах этой логики, различают три их разновидности: р-МОП — на р-канальных приборах;n-МОП — наn-канальных транзисторах; КМОП — на комплементарных структурах, состоящих из попарно включенных идентичных транзисторов с различными (р и п) проводимостями каналов.

Микросхемы этой логики, как правило, реализуют логические операции И—НЕ и ИЛИ—НЕ аналогично рассмотренным в § 13.2 контактным цепям (см. табл. 13.3). Так, для реализации логической операции И—НЕ в усилительной цепи последовательно включаются три полевых транзистора (рис. 13.6, а). При этом один из них (в данном случае VT1) используется в качестве токозадающего элемента, выполняющего роль нагрузочного резистора с сопротивлениемRС(рис. 11.9, а) в цепи стока транзистораVT2. Для появления на выходе сигнала низкого уровня, соответствующего логическому нулю (yш=0), необходимо, чтобы оба транзистораVT2 иVT3 были открыты, т. е. на затворы этих транзисторов должен быть подан сигнал высокого уровня, соответствующего логической 1 (x1=x2=1). Если хотя бы один из транзисторов (VT2 илиVT3) заперт, что соответствует сигналу низкого уровня (логическому 0) на его входе (затворе), значение выходного сигнала усилительной цепи будет близкоUп(логической 1), т.е.yш=1.

Для реализации логической операции ИЛИ—НЕ токозадающий транзистор VT1 включают последовательно с двумя параллельно соединенными транзисторамиVT2 иVT3 (рис. 13.6, б). Если хотя бы один из транзисторовVT2 илиVT3 открыт, что соответствует наличию на его входе (затворе) сигнала высокого уровня (логической 1), то выходной сигнал будет низкого уровня (логический 0). Значение его примерно равно напряжениюUСИоткрытого транзистора, работающего в режиме насыщения.

В случае применения полевых транзисторов с каналами различного типа (рис. 13.6, в) при подаче на вход (затвор) сигнала, соответствующего логическим 0 или 1, будет открыт только один из транзисторов, что значительно снижает потребляемую цепью мощность. Из сравнения усилительных цепей, приведенных на рис. 13.6, в и рис. 9 в табл. 13.2, очевидна их аналогия в электронной реализации логической операции НЕ.

Микросхемы на МОП-структурах, особенно типа КМОП, отличаются конструктивной простотой исполнения (например, схемы инверторов, приведенные на рис. 13.6), высокой помехоустойчивостью и чрезвычайно малой потребляемой мощностью.

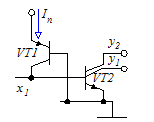

5. Интегрально-инжекционная логика(И2Л) относится к типу биполярной, так как в ней используются многоколлекторные биполярные транзисторы (VT2) (рис. 13.7), которые в этом случае имеют большую плотность монтажа, малую потребляемую мощность и т. п. Вместе с тем в И2Л удается сохранить высокое быстродействие биполярных транзисторов при малых мощностях рассеяния. Схемотехнические принципы, положенные в основу разработки микросхем на И2Л, приводят к следующим результатам: исключение резисторов позволяет снизить потребляемую мощность; применение специальных инжектирующих устройств (дополнительных р-n-р-транзисторов —VT1), используемых в режиме генераторов тока, обеспечивает высокое быстродействие (исключение накоплений заряда, уменьшение паразитных емкостей); размещение логических элементов вдоль инжекционных шин упрощает топологию микросхем. К отличительным особенностям микросхем на И2Л следует отнести питание от источника токаIпи возможность объединения в одном кристалле аналоговой и цифровой интегральных схем.

Рис. 13.7. Принципиальная электрическая схема элемента И2Л

Для конкретизации схемотехнических и технологических особенностей логических микросхем, применяемых в современных электронных устройствах, в табл. 13.5 приведены их усредненные показатели.

Таблица 13.5 Усредненные показатели для микросхем с различными