- •Екзаменаційний білет № 1

- •2. Вирішення багатокрітеріальних задач.

- •3. Математичне описування динамічних систем.

- •Екзаменаційний білет № 2

- •3. Моделювання систем за допомогою безперервних марківських ланцюгів.

- •Екзаменаційний білет № 3

- •1. Планування. Управління ресурсами, боротьба з взаємоблокуванням.

- •3. Вирішення багатокрітеріальних задач.

- •Екзаменаційний білет № 4

- •1. Файлові системи. Принципи побудови файлових систем.

- •2. Основні нормальні форми. Характеристика і приклади відносин, що знаходяться в 1нф, 2нф, 3нф.

- •Id, category, product1, product2, product3

- •3. Моделювання систем за допомогою дискретних марківських ланцюгів.

- •Екзаменаційний білет № 5

- •1. Поняття асемблера, компілятора, транслятора, інтерпретатора.

- •2. Основні оператори мови маніпулювання даними. Оператор вибірки даних (одно- і багатотабличні запити оператора select).

- •3. Поняття системи масового обслуговування. Класифікація систем масового обслуговування.

- •Классификация смо и их основные элементы

- •Екзаменаційний білет № 6

- •1. Завантажувачі. Завдання завантажувачів. Принципи побудови завантажувачів.

- •2. Технологія Ethernet.

- •3. Стадії та етапи створення асу тп.

- •Екзаменаційний білет № 7

- •1. Принципи об’єктно-орієнтованого програмування (парадигми програмування, поняття класу).

- •2. Технологія Token Ring.

- •3. Склад і коротка характеристика розділів технічного проекта.

- •Екзаменаційний білет № 9

- •1. Інкапсуляція. Поняття, сфери застосування.

- •2. Характеристика протоколу hdlc.

- •3. Методи боротьби з помилками, що виникають в каналах передачі даних. Завадостійке кодування. Екзаменаційний білет № 10

- •1. Поліморфізм. Поняття, сфери застосування.

- •2. Методи доступу в мережу.

- •3. Основні параметри завадостійких кодів. Принципи виявлення та виправлення помилок.

- •Екзаменаційний білет № 11

- •1. Принципи розробки розподілених клієнт-серверних програм. Особливості розробки мережевих програм з використанням сокетів.

- •2. Характеристика протоколу ip. Адресація в ip-мережах.

- •3. Циклічні коди. Алгоритми кодування і декодування. Циклические коды.

- •Свойства циклических кодов по обнаружению ошибок

- •Екзаменаційний білет № 12

- •1. Багаторівнева комп’ютерна організація – структура й призначення рівнів.

- •2. Характеристика протоколу tcp.

- •3. Статичні методи стиснення інформації. Алгоритм арифметичного стиснення.

- •Екзаменаційний білет № 13

- •1. Схема комп’ютера з єдиною шиною. Основні характеристики та принципи роботи шини комп’ютера.

- •2. Стадії та етапи створення асу тп.

- •3. Оптимальне кодування інформації. Алгоритми формування коду Хофмана та Шенона-Фано.

- •Екзаменаційний білет № 14

- •1. Структура процесора, внутрішні блоки, види регістрів.

- •2. Склад і коротка характеристика розділів технічного проекта.

- •3. Аналого-числові перетворення безперервного сигналу на базі теореми Котельникова в.А.

- •Екзаменаційний білет № 15

- •1. Команди процесора, структура команд. Цикл Фон-Неймана.

- •2. Склад і зміст проектних рішень з технічного забезпечення.

- •3. Протоколи фізичного рівня.

- •Екзаменаційний білет № 16

- •1. Структуру пам’яті комп’ютера. Елементи статичної та динамічної пам’яті.

- •2. Склад і задачі організацій, що беруть участь у роботах зі створення асу тп.

- •3. Характеристика протоколу ip. Адресація в ip-мережах.

- •Екзаменаційний білет № 17

- •1. Переривання, типи, алгоритм обробки переривання процесором.

- •2. Перелік видів випробувань асу тп та їх короткий зміст.

- •3. Характеристика протоколу tcp.

- •Екзаменаційний білет № 18

- •1. Загальні характеристики канального рівня.

- •2. Поняття системи масового обслуговування. Класифікація систем масового обслуговування.

- •Классификация смо и их основные элементы

- •3. Пропускна спроможність двійкового каналу зв’язку з перешкодами та без перешкод.

- •Екзаменаційний білет № 19

- •1. Загальні відомості з теорії систем. Класифікація систем.

- •2. Математичне описування динамічних систем.

- •3. Загальні характеристики канального рівня.

- •Екзаменаційний білет № 20

- •1. Поняття вимірювальної шкали. Види шкал.

- •2. Основні параметри завадостійких кодів. Принципи виявлення та виправлення помилок.

- •3. Стадії та етапи створення асу тп.

- •Екзаменаційний білет № 21

- •1. Показники якості та ефективності та крітерії їх оцінювання.

- •2. Структура процесора, внутрішні блоки, види регістрів.

- •3. Основні параметри завадостійких кодів. Принципи виявлення та виправлення помилок.

- •Екзаменаційний білет № 22

- •1. Вирішення задачі вибору.

- •2. Поняття операційної системи.

- •3. Розрахунок вартості проектних робіт ресурсним методом.

- •Екзаменаційний білет № 23

- •1. Декомпозиція. Компроміси між повнотою та простотою.

- •2. Характеристика протоколу hdlc.

- •3. Застосування елементних кошторисних норм для розрахунку вартості пусконалагоджувальних робіт.

- •Екзаменаційний білет № 24

- •1. Агрегування. Види агрегування.

- •2. Методи доступу в мережу.

- •3. Багатократні та комбіновані методи модуляції.

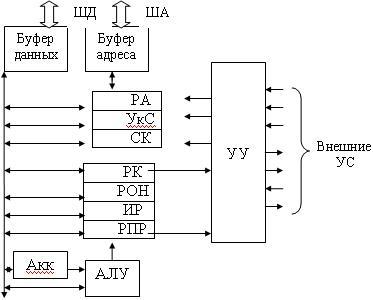

2. Структура процесора, внутрішні блоки, види регістрів.

Устройство управления(УУ) организует автоматическое выполнение программ и функционирование ЭВМ как единой системы. Основная задача УУ – выработка управляющих сигналов (УС) и распределение их по цепям управления.

Арифметическологическое устройство(АЛУ) предназначено для выполнения арифметических и логических операций над поступающими в него данными.

Оперативная память(ОП) представляет собой массив запоминающих элементов (ЗЭ), организованных в виде ячеек, способных хранить некую единицу информации.

Процессором называется функциональная часть ЭВМ, предназначенная для непосредственного осуществления процесса преобразования (обработки) информации и управления этим процессом. Другими словами – это совокупность арифметическологического устройства и устройства управления.

Регистр адреса Регистр адреса (РА) предназначен для хранения адреса ячейки основной памяти вплоть до завершения операции (считывание или запись) с этой ячейкой.

Указатель стека Указатель стека(УкС) — это регистр, где хранится адрес вершины стека. В реальных вычислительных машинах стек реализуется в виде участка основной памяти обычно расположенного в области наибольших адресов.

Заполнение стека происходит в сторону уменьшения адресов, при этом вершина стека — это ячейка, куда была произведена последняя по времени запись. Для хранения адреса такой ячейки и предназначен УкС. При выполнении операции занесения в стек содержимое УкС сначала уменьшается на единицу, после чего используется в качестве адреса, по которому производится запись. Соответствующая ячейка становится новой вершиной стека. Считывание из стека происходит из ячейки, на которую указывает текущий адрес в УкС, после чего содержимое указателя стека увеличивается на единицу. Таким образом, вершина стека опускается, а считанное слово считается удаленным из стека. Хотя физически считанное слово и осталось в ячейке памяти, при следующей записи в стек оно будет заменено новой информацией.

Счетчик команд

Согласно этому принципу соседние команды программы располагаются в ячейках памяти со следующими по порядку адресами и выполняются преимущественно в той же очередности, в какой они размещены в памяти ЭВМ. Таким образом, адрес очередной команды может быть получен путём увеличения адреса ячейки, из которой была считана текущая команда, на длину выполняемой команды, представленную числом занимаемых ею ячеек. Реализацию такого режима и призван обеспечивать счетчик команд — двоичный счетчик, в котором хранится и модифицируется адрес очередной команды программы. Перед началом вычислений в СК заносится адрес ячейки основной памяти, где хранится команда, которая должна быть выполнена первой. В процессе выполнения каждой команды путем увеличения содержимого СК на длину выполняемой команды в счетчике формируется адрес следующей подлежащей выполнению команды. В данном случае любая команда занимает одну ячейку, поэтому содержимое СК увеличивается на единицу. По завершении текущей команды адрес следующей команды программы всегда берется из счетчика команд. Для изменения естественного порядка вычислений (перехода в иную точку программы) достаточно занести в СК адрес точки перехода.

Регистр команды Счетчик команд определяет лишь местоположение команды в памяти, но не содержит информации о том, что это за команда. Чтобы приступить к выполнению команды, ее необходимо извлечь из памяти и разместить в регистре команды (РК). Этот этап носит название выборки команды. Только с момента загрузки команды в РК она становится «видимой» для процессора. В РК команда хранится в течение всего времени ее выполнения.

Регистры общего назначения Регистры общего назначения (РОН), служат для временного хранения операндов и результатов вычислений. Это самый быстрый, но и минимальный по емкости тип памяти, который иногда объединяют понятиемсверхоперативное запоминающее устройство — СОЗУ. Как правило, количество регистров невелико, хотя в архитектурах с сокращенным набором команд их число может доходить до нескольких десятков.

Индексные регистры Индексные регистры (ИР) служат для формирования адресов операндов при реализации циклических участков программ.

Регистр признака результата Регистр признака результата (РПР) предназначен для фиксации и хранения признака, характеризующего результат последней выполненной арифметической или логической операции. Такие признаки могут информировать о равенстве результата нулю, о знаке результата, о возникновении переноса из старшего разряда, переполнении разрядной сетки и т. д. Содержимое РПР обычно используется устройством управления для реализации условных переходов по результатам операций АЛУ. Под каждый из возможных признаков отводится один разряд РПР.

АккумуляторАккумулятор (Акк) — это регистр, на который возлагаются самые разнообразные функции. Так, в него предварительно загружается один из операндов, участвующих в арифметической или логической операции. В Акк может храниться результат предыдущей команды и в него же заносится результат очередной операции. Через Акк зачастую производятся операции ввода и вывода. Строго говоря, аккумулятор в равной мере можно отнести как к АЛУ, так и к УУ, а в ЭВМ с регистровой архитектурой его можно рассматривать как один из регистров общего назначения.

Буфер данных Буфер данных призван компенсировать разницу в быстродействии запоминающих устройств и устройств, выступающих в роли источников и потребителей хранимой информации. В буфер данных при чтении заносится содержимое ячейки ОП, а при записи — помещается информация, подлежащая сохранению в ячейке ОП.

Буфер адреса Наличие буфера адреса также позволяет компенсировать различия в быстродействии оперативной памяти и других устройств ЭВМ.