- •Введение

- •Лекция 1

- •1. Электрические цепи постоянного тока

- •Электрическая цепь постоянного тока. Параметры злементов цепи. Закон Ома

- •1.2. Режимы работы источника электрической энергии

- •1.3. Законы Кирхгофа

- •1.4. Использование законов Кирхгофа для расчета электрических цепей

- •Лекция 2

- •1.5. Эквивалентные преобразования электрических цепей

- •1.5.1. Последовательное соединение элементов.

- •1.5.2. Параллельное соединение элементов.

- •1.5.3. Смешанное соединение резистивных элементов.

- •1.5.4. Эквивалентные преобразования резистивных элементов треугольником и звездой.

- •1.6. Работа и мощность постоянного тока. Закон Джоуля – Ленца

- •2. Электрические цепи переменного тока

- •2.1. Генерация синусоидальной эдс. Основные величины, характеризующие переменный ток

- •2.2. Представление синусоидальных величин аналитически, графически, вращающимися векторами, комплексными числами

- •2.3. Цепь переменного тока с активным сопротивлением

- •2.4. Цепь переменного тока с индуктивностью

- •2.5. Цепь переменного тока с ёмкостью

- •Лекция 4

- •2.6. Неразветвлённая цепь переменного тока с активным сопротивлением, индуктивностью и ёмкостью. Резонанс напряжений

- •2.7. Разветвленная цепь однофазного переменного тока. Резонанс токов

- •2.8. Колебательный lc - контур переменного тока

- •2.9. Мощность однофазного переменного тока. Коэффициент мощности

- •3. Трёхфазные электрические цепи

- •3.1. Преимущество трёхфазного тока. Принцип получения трёхфазной эдс

- •Лекция 6

- •3.2. Соединение источников и потребителей электрической энергии звездой. Соотношения между фазными и линейными напряжениями и токами при симметричной и несимметричной нагрузках

- •3.2.1. Наличие нулевого провода

- •3.2.2. Отсутствие нулевого провода

- •3.3. Обрыв фазы и короткое замыкание фазы без нулевого провода при соединении источников энергии и потребителей звездой

- •3.3.1. Обрыв фазы a

- •3.3.2. Короткое замыкание фазы a

- •3.4. Соединение источников и приёмников электроэнергии треугольником. Соотношения между фазными и линейными напряжениями и токами при симметричной и несимметричной нагрузках

- •3.5. Обрыв фаз и обрыв линейного провода при соединении источников и потребителей треугольником

- •3.5.1. Обрыв фазы ab

- •3.5.2. Обрыв фаз ab и bc

- •3.5.3. Обрыв линейного провода

- •3.6. Мощность трёхфазной цепи

- •Лекция 7

- •3.7. Соотношения активных мощностей при симметричной нагрузке и при соединении звездой и треугольником

- •3.8. Вращающееся магнитное поле трёхфазной системы переменного тока

- •4. Трансформаторы

- •4.1. Однофазные трансформаторы. Устройство и принцип действия

- •4.2. Режимы работы трансформатора. Коэффициент полезного действия трансформатора

- •Лекция 8

- •4.3. Трёхфазные трансформаторы

- •4.4. Измерительные трансформаторы

- •5. Электрические машины постоянного тока

- •5.1. Устройство и принцип действия генератора постоянного тока

- •5.2. Генераторы постоянного тока независимого и параллельного

- •Лекция 9

- •5.3. Генераторы постоянного тока последовательного и смешанного возбуждений и их основные характеристики

- •5.4. Принцип действия электродвигателя постоянного тока

- •5.5. Электродвигатели постоянного тока параллельного возбуждения и их основные характеристики

- •5.6. Электродвигатели постоянного тока последовательного и смешанного возбуждений и их основные характеристики

- •5.7. Пуск, регулирование частоты вращения и реверс электродвигателей постоянного тока

- •Лекция 10

- •6.Трёхфазные асинхронные машины

- •6.1.Устройство и принцип действия асинхронного двигателя

- •6.2. Зависимость частоты вращения ротора, величины эдс и тока

- •6.3. Электромагнитный момент и механическая характеристика

- •Лекция 11

- •6.4. Пуск и реверс асинхронных двигателей

- •6.5. Регулирование частоты вращения трёхфазного асинхронного двигателя

- •Лекция 12

- •7. Полупроводниковые приборы

- •7.1. Электропроводность полупроводников

- •7.2. Полупроводниковые диоды. Устройство, принцип действия

- •7.3. Биполярные транзисторы. Устройство, принцип работы

- •7.4. Схемы включения биполярных транзисторов с p-n-p структурой

- •7.5. Полевые транзисторы с управляющим p-n переходом

- •7.6. Динисторы, тиристоры. Устройство, принцип действия

- •7.7. Симисторы. Устройство, принцип действия

- •Лекция 14

- •7.8. Фоторезисторы и фотодиоды. Устройство, принцип действия

- •7.9. Фототранзисторы, фототиристеры, оптроны.

- •8. Схемы электронных преобразователей

- •8.1. Однополупериодные выпрямители

- •Лекция 15

- •8.2. Двухполупериодные выпрямители

- •8.3. Трёхфазные выпрямители. Электрические сглаживающие фильтры

- •Лекция 16

- •8.4. Электронные усилители на биполярных транзисторах

- •8.5. Импульсные усилители

- •8.6. Операционные усилители

- •9. Цифровые устройства

- •9.1. Логические функции, логически устройства.

- •9.2. Основные логические элементы.

- •4. Логический элемент или, операция логическое сложение ,

- •9.3. Асинхронный rs-триггер. Устройство, принцип действия

- •Лекция 18

- •9.4. Синхронный rs-триггер. Устройство, принцип действия

- •9.5. Синхронные d-триггер. Устройство, принцип действия

- •9.6. Шифратор. Устройство, принцип работы

- •9.7. Дешифратор. Устройство, принцип работы

- •Лекция 19

- •9.8. Регистры. Устройство, принцип работы

- •9.9. Счётчики импульсов. Устройство, принцип работы

- •Библиографический список

- •Cодержание

- •Иванов Евгений Николаевич

- •Электротехника и электроника

- •Конспект лекций

Лекция 18

9.4. Синхронный rs-триггер. Устройство, принцип действия

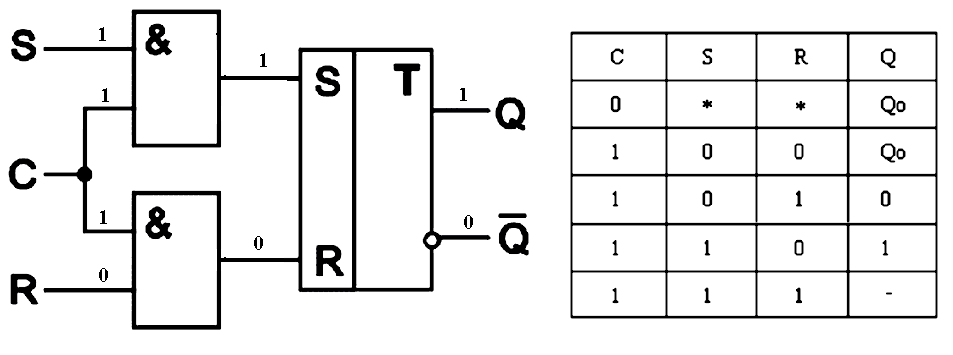

Синхронный RS-триггер снабжён синхронизирующим входом С, который разрешает приём сигналов с информационных входов R и S. Если на синхронизирующий вход С поступает сигнал лог.0, то любые логические сигналы, подаваемые на информационные входы R и S, не влияют на состояние триггера. При подаче на синхронизирующий вход С сигнала лог.1, синхронный RS-триггер работает в режиме асинхронного RS-триггера.

На рис.9.5 изображено условное обозначение синхронного RS-триггера.

Рис.9.5. Условное обозначение синхронного RS-триггера

На рис.9.6 приведена структурная логическая схема и таблица истинности RS-триггера, построенного на двух логических элементах И, а также на одном асинхронном RS-триггере.

Рис.9.6. Структурная логическая схема и таблица истинности RS-триггера

Из таблицы истинности следует, что при подаче на вход С сигнала лог.0 триггер сохраняет на выходе Q информацию, предшествующую подаче этого сигнала, при любом состоянии информационных входов R и S (0 или 1). При подаче на синхронизирующий вход С сигнала лог.1, синхронный RS-триггер превращается в асинхронный RS-триггер.

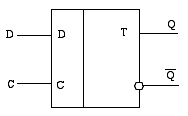

9.5. Синхронные d-триггер. Устройство, принцип действия

Синхронный D-триггер предназначен для одноступенчатого запоминания информации. На рис.9.7 показаны условное обозначение и таблица истинности

D

-

триггера. Триггер имеет два входа:

информационный D

и синхронизирующий C,

а также два выхода: прямой Q

и

инверсный

![]() .

.

Согласно таблице истинности, при подаче на синхронизирующий вход C сигнала лог.0, а на вход D любого из логических сигналов лог. 0 или лог.1, на выходе Q будет сохранён логический сигнал, подаваемый на вход D.

Рис.9.7. Условное обозначение и таблица истинности

D – триггера

При подаче на вход C сигнала лог.1, на выходе Q будет сохранён логический сигнал, подаваемый на вход D.

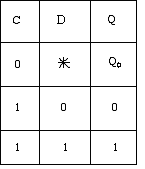

На рис.9.8 изображена логическая схема, реализующая принцип действия синхронного D - триггера. Схема состоит из асинхронного триггера, двух логических элементов И и одного инвертора. На схеме показан один из вариантов работы таблицы истинности.

Рис.9.8. Логическая схема, реализующая принцип действия синхронного D -триггера

9.6. Шифратор. Устройство, принцип работы

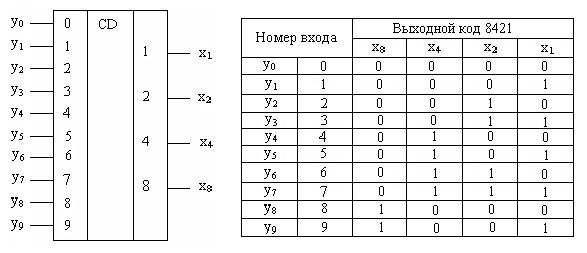

Шифратор осуществляет преобразование десятичных чисел в двоичную систему счисления. На рис.9.9 приведено символическое изображение шифратора, преобразующего десятичные числа 0, 1, 2, … , 9 в выходной код 8421 и его таблица истинности. Символ CD образован из букв английского слова Coder. Слева показаны 10 входов шифратора, справа – выходы шифратора; цифрами 1,2,4,8 обозначены весовые коэффициенты двоичных четырёх разрядов шифратора.

Из

таблицы истинности видно, что выходу

x1

будет соответствовать лог. 1,

если одна из входных переменных y1,

y3,

y5,

y7,

y9

будет также иметь лог. 1.

Следовательно, можно составить логическую

операцию x1=y1![]() y3

y3![]() y5

y5![]() y7

y7![]() y9.

Для остальных выходов можно составить

логические операции: x2=y2

y9.

Для остальных выходов можно составить

логические операции: x2=y2![]() y3

y3![]() y6

y6![]() y7,

x4=y4

y7,

x4=y4![]() y5

y5![]() y6

y6![]() y7,

x8=y8

y7,

x8=y8![]() y9.

y9.

Рис.9.9. Символическое изображение шифратора и его таблица истинности

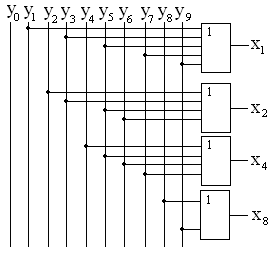

Используя полученные логические операции, можно реализовать логическую схему шифратора, построенную на логических элементах ИЛИ, приведённую на рис.9.10. Шифраторы используются в устройствах ввода информации в цифровые системы с клавиатуры.

Рис.9.10. Логическая схема шифратора