- •Введение

- •1. Структура курса, отчетность.

- •2.Литература: Конспект лекций ( Электронное пособие)

- •Краткая история развития микропроцессорных систем

- •Архитектурные признаки контроллеров

- •Тема 1. Базовая структура микроконтроллерной (мк) системы управления

- •Тема 2. Модель микроконтроллера

- •Режимы обмена информацией

- •Тема 3. Структура базового мк

- •Тема 4. Организация и функционирование базового цпу

- •Устройство управления и синхронизации

- •Тема 5. Языки программирования контроллера

- •Основные группы команд контроллера

- •2. Команды арифметических операций.

- •3. Команды логических операций

- •4. Команды передачи управления

- •Этапы реализации логических функций

- •Реализация логических функций ( вариант 2)

- •Управление пуском – остановом электродвигателя

- •Тема 7. Управление параметром в заданных пределах

- •Алгоритм управления температурой

- •Тема 8. Формирование временных интервалов таймером

- •Тема 9. Обработка прерываний в контроллере

- •Настройка контроллеров прерывания

- •Тема 9. Последовательный интерфейс в мк

- •Принцип организации последовательного адаптера

- •Тема 10. Организация параллельного интерфейса

- •Основные характеристики адаптера

- •Структурная схема параллельного периферийного адаптера

- •Программирование адаптера

- •Тема 11. Аналого-цифровые и цифро-аналоговые преобразователи

- •Тема 12 .Разработка и отладка программ в симуляторе adsim812

- •Симулятор adSim812

Принцип организации последовательного адаптера

Модуль состоит из двух независимых подсистем: передатчика (Transmitter) и приемника (Receiver), поэтому возможен режим одновременной передачи и приема информации в последовательном коде. Основу каждой подсистемы составляет сдвиговый регистр и параллельный регистр буфера данных. Обращение к буферу данных приемника и передатчика осуществляется по одному и тому же адресу, но при выполнении операции записи данные будут помещены в буфер передатчика TDBUF, операции чтения – данные будут считаны из буфера приемника RDBUF.

Передача данных от МК к другому устройству инициируется посредством записи байта данных в регистр TDBUF. Если работа передатчика разрешена (бит ТЕ в регистре управления модулем равен 1), то аппаратные средства модуля загружают содержимое TDBUF в сдвиговый регистр и под управлением генератора скорости обмена биты из сдвигового регистра, начиная с младшего DO, последовательно передаются на вывод TxD MK. По завершении передачи байта данных устанавливается бит TI, который информирует МК о том, что буфер передатчика пуст и в него могут быть загружены новые данные для передачи. Бит TI генерирует запрос на прерывание, если прерывания от передатчика в МК разрешены. Бит TI может также быть считан программно.

Рис. Структура последовательного адаптера

Если работа приемника разрешена (бит RE в регистре управления модулем равен 1), то после распознавания стартового бита аппаратные средства приемника преобразуют данные, которые поступают на вход RxD в последовательном коде, в параллельный код. После завершения приема последнего бита в сдвиговом регистре приемника находится принятый байт данных, который автоматически переносится в регистр RDBUF. Одновременно устанавливается в 1 флаг завершения приема RI. Бит RI может быть считан под управлением программы, и, если прерывания от приемника разрешены, генерируется запрос на прерывание. В процессе выполнения подпрограммы обработки прерывания принятый байт данных считывается из регистра данных приемника RDBUF в память МК. Сразу после копирования байта данных из сдвигового регистра в RDBUF приемник может начать формирование следующего байта данных, отдельные биты которого продолжают поступать на вход RxD. Однако необходимо, чтобы центральный процессор МК успел считать данные из буферного регистра RDBUF до завершения формирования в сдвиговом регистре следующего принятого байта. Если этого не произошло, то возникшая аварийная ситуация в модулях UART разрешается различными путями. В модулях SCI фирмы Motorola запись следующего принятого байта в буферный регистр данных не производится и устанавливается флаг ошибки OR (Overrun). Этот флаг наравне с триггером RI может генерировать запрос на прерывание от приемника. В модулях МК Intel MCS-51 и ему полностью аналогичных такая защита отсутствует: следующий принятый байт затирает предыдущий в регистре RDBUF.

Термин асинхронный означает, что при передаче символов послания скорость их передачи может быть различной.

Для организации каналов связи используются 3 типа кабелей, отличающихся стоимостью, скоростью передачи данных, надежностью передачи и внешним видом:

витая пара (экранированная и неэкранированная);

коаксиальный кабель (тонкий и толстый);

волоконно-оптический кабель.

С технической точки зрения интерфейсы отличаются:

режимом передачи данных (синхронный и асинхронный);

формой кадра (кол-во передаваемых бит для кодирования символа и специальных бит);

уровнями передаваемых сигналов и скоростью обмена;

количество физических линий (от 2 до 4);

расстояние передачи данных между источником и приемником.

Упомянутые типы интерфейсов последовательной связи отличаются:

режимом передачи данных (синхронный или асинхронный);

форматом кадра (число бит в посылке при передаче байта полезной информации);

временными диаграммами сигналов на линиях (уровни сигналов и положение фронтов при переключениях).

Среди различных типов встроенных модулей последовательного обмена, входящих в МК сложился стандарт "де-факто" – модуль UART (Universal Asynchronous Receiver and Transmitter). В переводе с английского UART – универсальный асинхронный приемопередатчик.

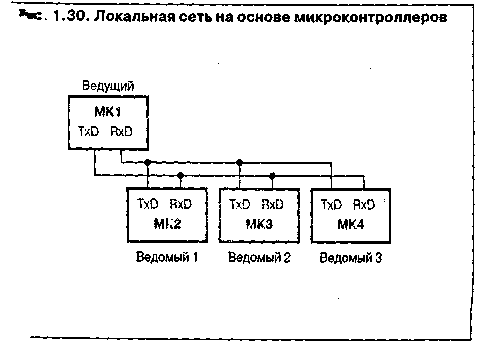

На

рис. ниже приведена структура такой

локальной МК сети. Один из МК в этой сети

является ведущим, все остальные –

ведомыми. В каждый момент времени обмен

возможен между ведущим и одним из

ведомых, обмен между двумя ведомыми не

реализуется. Инициатором обмена всегда

является только ведущий.

На

рис. ниже приведена структура такой

локальной МК сети. Один из МК в этой сети

является ведущим, все остальные –

ведомыми. В каждый момент времени обмен

возможен между ведущим и одним из

ведомых, обмен между двумя ведомыми не

реализуется. Инициатором обмена всегда

является только ведущий.