- •Занятие 1

- •4.3 Требования к динамическому диапазону приемного тракта и технические решения, обеспечивающие их выполнение

- •4.3.1 Согласование динамических диапазонов элементов приемного тракта

- •4.3.2 Шумовая автоматическая регулировка усиления

- •4.3.3 Усилители с логарифмической амплитудной характеристикой

- •4.4 Технические решения, обеспечивающие помехозащиту рлс методами пространственной и поляризационной селекции

- •4.4.1 Уменьшение угловых размеров главного лепестка дна и снижение уровня боковых лепестков

- •4.4.2 Уменьшение уровня приема в направлении на постановщик ашп

- •4.5 Устройства защиты рлс от импульсных помех

- •4.5.1 Устройства защиты от узкополосных импульсных помех

- •4.5.2 Устройства защиты от широкополосных импульсных помех

- •4.5.3 Устройства защиты от нип

- •4.5.4 Особенности построения устройств защиты от ответных импульсных помех

- •Занятие 2

- •4.7 Влияние пассивных помех на боевые возможности рлс

- •4.7.1 Методика определения возможностей рлс (рлк) по обнаружению воздушных объектов в условиях пассивных помех

- •4.8 Обобщенная структурная схема системы сдц

- •4.8.1 Структурная схема систем сдц

- •4.8.2 Основные характеристики системы сдц

- •4.9 Устройства селекции движущихся целей

- •4.9.1 Устройства сдц с эквивалентной внутренней когерентностью с чпв на видеочастоте

- •4.9.2 Устройства сдц с внешней когерентностью с чпв на видеочастоте

- •4.9.3 Устройства сдц с чпв на промежуточной частоте

- •Занятие 3

- •4.10 Принципы построения элементов и устройств системы сдц

- •4.10.1 Ограничитель

- •4.10.2 Фазовый детектор

- •4.10.3 Устройство формирования опорного напряжения

- •4.10.4 Устройство череспериодной компенсации

- •4.10.5 Устройство чпк на вычитающих потенциалоскопах

- •4.10.6 Влияние нестабильностей аппаратуры на эффективность систем сдц

- •Занятие 4

- •4.11 Системы сдц на базе автокомпенсаторов

- •4.11.1 Структурная схема чпак

- •4.11.2 Основные характеристики чпак

- •4.12 Фильтровые и корреляционно-фильтровые системы сдц

- •4.12.1 Фильтровые системы сдц

- •4.12.2 Корреляционно-фильтровые системы сдц

- •4.12.3 Основные характеристики фильтровых и корреляционнофильтровых систем сдц

- •4.13 Дискретно-аналоговые и цифровые системы сдц

- •4.13.1 Дискретно-аналоговые системы сдц

- •4.13.2 Цифровые системы сдц

- •Занятие 5

- •5.2 Принципы построения устройств преобразования радиолокационных сигналов в цифровую форму

- •5.2.1 Устройства дискретизации аналоговых сигналов

- •5.2.2 Устройства квантования

- •5.2.3 Аналого-цифровые преобразователи, их параметры и основные типы

- •5.3 Принципы построения цифровых обнаружителей радиолокационных сигналов

- •5.3.1 Цифровые обнаружители радиолокационных сигналов при бинарном квантовании

- •5.3.2 Цифровые обнаружители радиолокационных сигналов при многоуровневом квантовании

- •5.4 Цифровые измерители координат воздушных объектов

- •5.4.1 Цифровые измерители дальности и азимута

- •5.4.2 Измерение доплеровской частоты сигнала

- •Занятие 6

- •5.5 Вторичная обработка радиолокационной информации

- •5.5.1 Существо процедур вторичной обработки рли

- •5.5.2 Стробирование и селекция отметок в стробах

- •5.5.3 Оценка параметров траекторий

- •5.5.3.1 Сглаживание и экстраполяция при вторичной обработке

- •5.5.3.2 Алгоритм фильтрации параметров траектории по методу максимального правдоподобия

- •5.5.4 Оптимальное последовательное сглаживание координаты и скорости ее изменения

- •5.5.5 Последовательное сглаживание скорости и курса. Выявления маневра воздушного объекта

- •5.5.6 Обнаружение и сопровождение траекторий воздушных объектов в обзорной рлс

- •5.5.6.1 Структурная схема алгоритма обнаружения траекторий

- •5.5.6.2 Структурная схема алгоритма сопровождения траекторий

- •5.5.7 Полуавтоматическое сопровождение траекторий воздушных объектов

- •Занятие 7

- •6.1 Индикаторные устройства рлс и их основные характеристики

- •6.1.1 Назначение и классификация индикаторных устройств

- •6.1.2 Влияние индикаторов на характеристики рлс

- •6.2 Принципы построения индикаторов обзорных рлс

- •6.2.1 Функциональный состав индикатора

- •6.2.2 Ико с вращающимися отклоняющими системами

- •6.2.3 Индикатор кругового обзора с неподвижной отклоняющей системой

- •Занятие 8

- •6.3 Принципы построения системы отображения радиовысотомера

- •6.3.1 Способы построения индикаторов измерения высоты

- •6.3.2 Функциональная схема индикатора измерения высоты

- •6.4 Системы передачи и формирования масштабных отметок азимута рлс ртв

- •6.4.1 Принципы построения систем передачи азимута рлс ртв

- •6.4.2 Принципы построения систем формирования масштабных отметок азимута рлс ртв

4.13 Дискретно-аналоговые и цифровые системы сдц

В рассмотренных ранее аналоговых системах СДЦ в качестве устройств запоминания сигналов использовались линии задержки на период следования. Недостатки таких систем связаны с тем, что в них затруднена вобуляция частоты повторения, устройства сложны в производстве, имеют значительный уровень ложных сигналов из-за переотражений от торцов, изгибов, граней.

Вычитающие потенциалоскопы в системах СДЦ РЛС старого парка (например, в РЛС П-18 и 5Н84А) используются для запоминания и череспериодного вычитания. Недостатки таких систем связаны с небольшим динамическим диапазоном (около 10 дБ), небольшим коэффициентом подавления даже абсолютно коррелированных сигналов, что обусловлено малым коэффициентом перезаряда элемента мишени, и междупериодным растеканием зарядов по мишени. Вычитающие потенциалоскопы сложны и критичны в настройке, сильно ослабляют сигналы, из-за чего существенно сказываются их собственные шумы.

В значительной мере этих недостатков лишены дискретно-аналоговые и особенно цифровые системы СДЦ.

4.13.1 Дискретно-аналоговые системы сдц

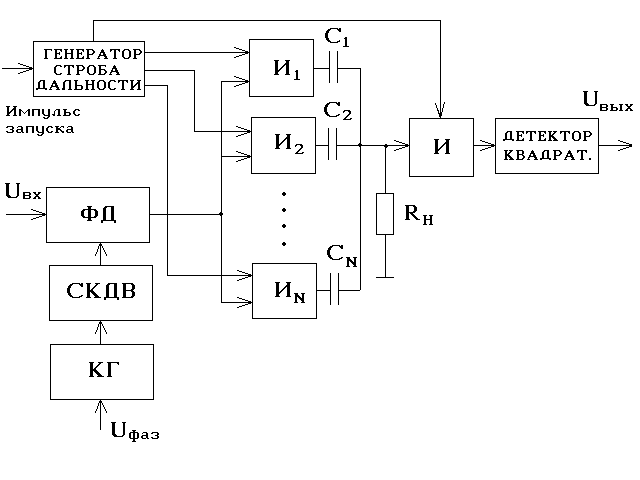

Упрощенная структурная схема одного из квадратурных каналов дискретно-аналоговой СДЦ с однократным ЧПВ приведена на рис.4.78.

Рис.4.78. Упрощенная структурная схема квадратурного канала дискретно-аналоговой СДЦ

Выходные видеосигналы ФД с помощью ключей (схем И), открываемых стробами дальности, распределяются по каналам дальности. В каждом канале включены конденсаторы (С1, С2, ... СN). Во время действия помехи (сигнала) конденсатор данного канала дальности заряжается через открытую схему Иi и общий для всех каналов резистор R до амплитуды импульса. После закрывания схемы Иi конденсатор сохраняет свой заряд до прихода импульса в следующем периоде следования. Если последовательность импульсов пачки будет иметь на выходе ФД такую же амплитуду и полярность, то перезаряда не будет и на R падение напряжения не создастся. Если же импульсы пачки промодулированы по амплитуде, то на R будет выделен сигнал разностной амплитуды, т.е. в схеме производится однократное ЧПВ сигналов. Съем сигналов с сопротивления R производится в каждом дискрете дальности с помощью схем И, открываемой импульсами считывания.

Набор ключей, конденсаторов и резистора представляет собой дискретную модель вычитающего потенциалоскопа. Чтобы получить большой коэффициент подавления необходимо, чтобы конденсатор любого кольца дальности успевал за время длительности импульса зарядится до его амплитудного значения, а затем сохранил заряд до прихода следующего импульса. Это достигается выбором малой постоянной цепи заряда через открытую схему Иi и большим сопротивлением утечки закрытой схемы Иi. Применение таких схем (систем СДЦ) позволяет получить коэффициент подпомеховой видимости до 35 дБ.

Таким образом, дискретно-аналоговые системы СДЦ представляют собой определенный набор ключей, конденсаторов и резистора, что в совокупности образует дискретную модель вычитающего потенциалоскопа.

4.13.2 Цифровые системы сдц

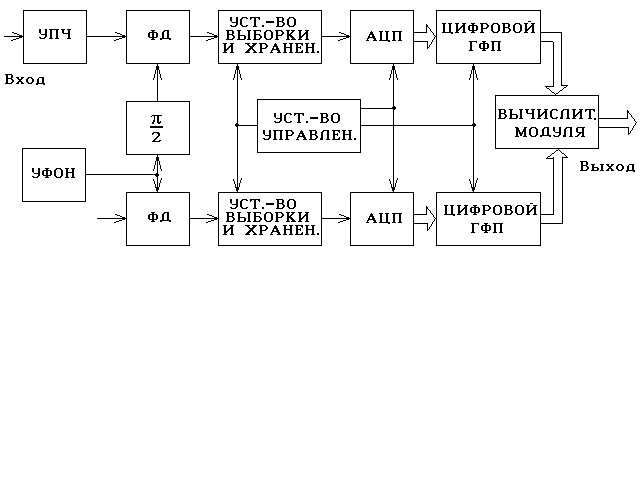

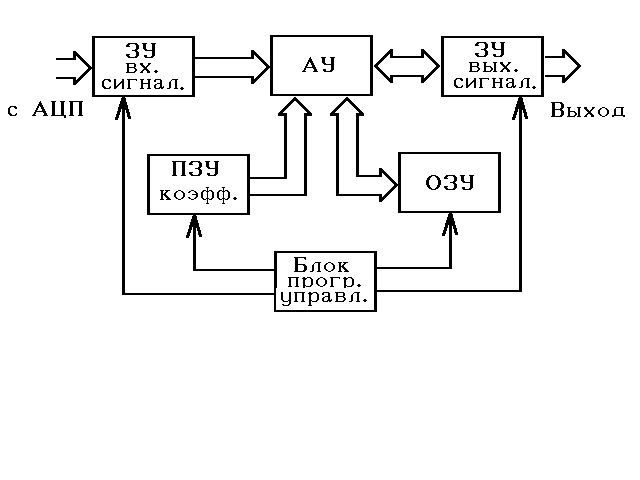

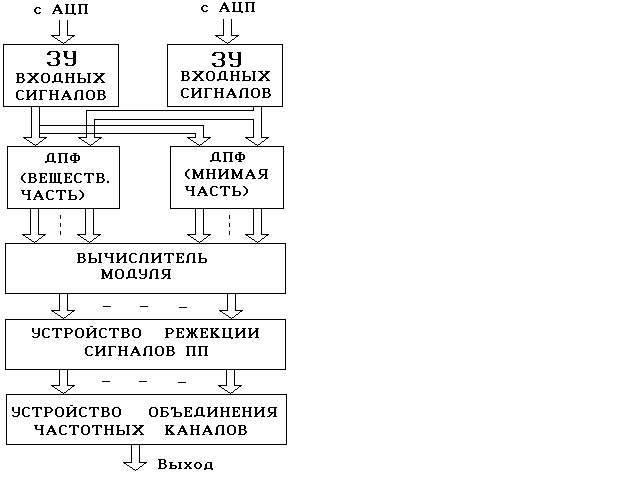

В цифровых системах СДЦ наиболее полно проявляются преимущества цифровых методов и устройств обработки радиолокационных сигналов. Их принципиальным отличием от обычных систем СДЦ является цифровая реализация гребенчатого фильтра подавления (рис.4.79).

Коэффициент подавления ПП, реализуемый в цифровых системах СДЦ, определяется соотношением

КППр = (К-1ПП пред + К-1ПП АЦП + S К-1ПП i,)-1, (4.77)

где КПП пред − предельно достижимый коэффициент подавления ПП для заданных структуры цифрового гребенчатого фильтра подавления(ЦГФП), параметров ПП и динамического диапазона тракта до АЦП; КПП АЦП ≈ 10 -0,6m (здесь m − разрядность АЦП); КПП i − коэффициент подавления, обусловленный нестабильностью i-го функционального узла РЛС (генератора СВЧ, местного и когерентного гетеродинов).

Из формулы (4.77) видно, что использование цифровой системы СДЦ еще не является гарантией высокой помехозащищенности РЛС от ПП. Для полной реализации ее возможностей необходимо принимать меры по стабилизации параметров зондирующего сигнала, частот гетеродинов и расширению динамического диапазона приемного тракта (Дпр КППтр).

Рис.4.79. Обобщенная структурная схема цифровой системы СДЦ

Цифровые ГФП могут обрабатывать сигналы во временной или частотной областях. В первом случае ЦГФП являются эквивалентом аналоговых устройств ЧПК, соответствующей кратности (с обратными связями или без них), а во втором − набора доплеровских фильтров корреляционно-фильтровых систем СДЦ.

Рассмотрим особенности технической реализации ЦГФП, осуществляющих обработку сигналов во временной области (цифровые режекторные фильтры).

Цифровые ГФП могут быть выполнены по рекурсивной и нерекурсивной схемам.

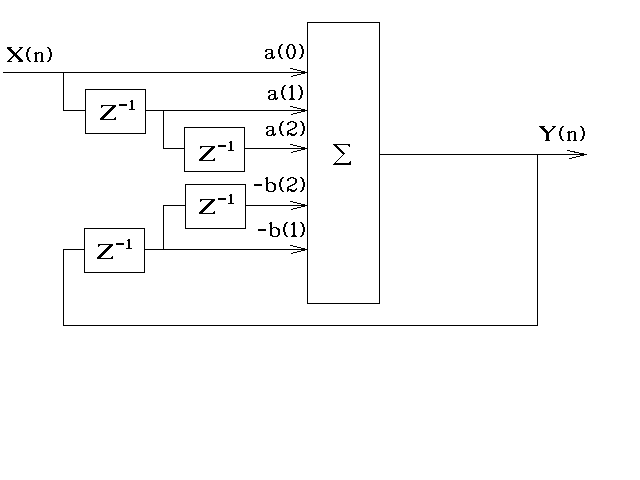

Обобщенная структурная схема режекторного фильтра содержит совокупность линий задержки, соединенных последовательно, с выходов которых сигналы через соответствующие переключатели поступают на сумматор (рис.4.80).

В этом фильтре обработка сигналов осуществляется с использованием выражения:

![]() (4.78)

(4.78)

где х (n) − входной сигнал в момент tn; у (n) − выходной сигнал в момент tn; а (i), b (i) − весовые коэффициенты. Если не все b(i) = 0, то фильтр называется рекурсивным. Примером рекурсивного фильтра первого порядка является цифровой рециркулятор.

В рекурсивных фильтрах выходной сигнал зависит не только от значений входного сигнала в данный момент, но и от значений выходного сигнала в предыдущие моменты времени.

Рис.4.80. Обобщенная структура цифрового ГФП (Z-1- элемент задержки на Тп)

Рекурсивные фильтры называют еще фильтрами с бесконечной памятью или с бесконечной импульсной характеристикой (БИХ-фильтры), поскольку в них хранится вся «история» входной последовательности.

Реализация рекурсивных фильтров требует применения обратных связей, а значит принятия дополнительных мер по обеспечению их устойчивости. Примером рекурсивного фильтра первого порядка является цифровой рециркулятор.

В случае, когда все коэффициенты b(i) в формуле (4.78) равны нулю

![]() (4.79)

(4.79)

не зависит от значений выходного сигнала в предыдущие моменты времени.

Цифровые фильтры, реализующие этот алгоритм, называются нерекурсивными или фильтрами с конечной памятью (КИХ-фильтры) или трансверсальными фильтрами. Реализация их не требует использования обратных связей и поэтому такие фильтры всегда устойчивы. Это является их преимуществом перед рекурсивными ЦФ.

Недостатком рекурсивных ЦФ является накопление ошибок, так как при вычислении последующих отсчетов выходного сигнала используются неточно полученные (из-за конечного числа разрядов вычислительного устройства) предшествующие отсчеты.

Преимущество рекурсивных ЦФ состоит в том, что для их реализации требуется обычно намного меньше элементов, чем для эквивалентных им (с точки зрения характеристик) нерекурсивных ЦФ. В системах СДЦ могут применяться как рекурсивные, так и нерекурсивные ЦФ.

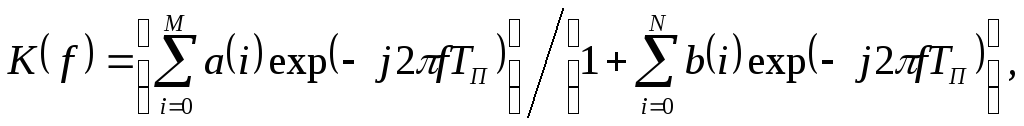

Частотная характеристика ЦФ определяется соотношением

(4.80)

(4.80)

Требуемый вид частотной характеристики обеспечивается выбором значений весовых коэффициентов а(i) и b(i).

Для анализа частотной характеристики цифровых фильтров широко применяется метод Z − преобразования:

X(n − i) = X(z) Z-i, (4.81)

т.е. Z-i соответствует задержке на iТ. Тогда

![]() (4.82)

(4.82)

Z − преобразование удобно тем, что подставляя в выражение для передаточной функции Н(z) = y(z)/x(z) значения z = exp(j2πfT), можно получить комплексную частотную характеристику фильтра:

Н(f) = |H(f)| exp[j arg H(f)]. (4.83)

Требуемый вид амплитудно частотной характеристики (АЧХ) обеспечивается выбором значений весовых коэффициентов а(i) и b(i).

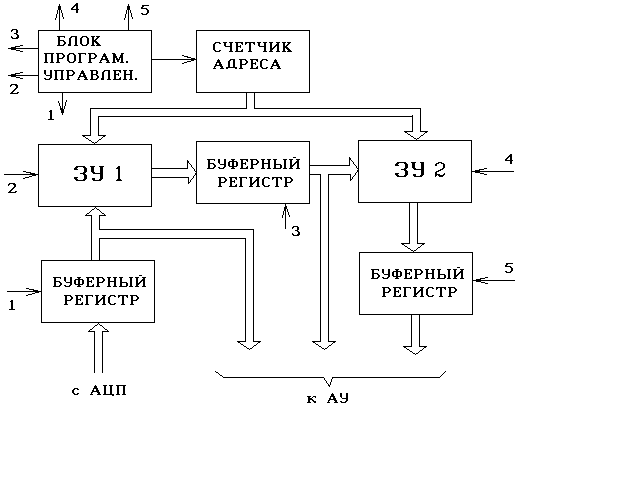

В состав ЦФ (рис.4.81) входят:

ЗУ входных и выходных сигналов;

оперативное и постоянное запоминающие устройства;

арифметическое устройство.

Рис.4.81. Структурная схема цифрового фильтра

Запоминающие устройства могут иметь различную структуру. Организация ЗУ для нерекурсивного фильтра второго порядка (эквивалент двукратного устройства ЧПК) иллюстрируется на рис.4.82.

Буферный регистр запоминает код выходного сигнала АЦП на время Тд. ЗУ1 обеспечивает запоминание кодов сигналов со всех N каналов дальности на Тп. Емкость его составляет N∙m бит, где m − разрядность АЦП.

Запоминающее устройство может выполняться на микросхемах памяти, управляемых адресным счетчиком, или сдвиговых регистрах. В микросхемах памяти в качестве запоминающих элементов используют триггеры. Если одна микросхема запоминает один разряд кода сигналов со всех каналов дальности, то для запоминания N m-разрядных слов необходимо m корпусов микросхем.

Так как входные (выходные) сигналы поступают (считываются) на ЗУ (с ЗУ) последовательно, то управление работой ЗУ существенно упрощается − ячейки для записи и считывания можно выбирать, например с помощью адресного счетчика, на вход которого поступают импульсы дискретизации. Принцип построения ЗУ2 аналогичен ЗУ1.

В общем случае емкость ЗУ входных и выходных сигналов примерно равна 2Тп FДmax m (М + N) бит.

Оперативное запоминающее устройство предназначено в общем случае для хранения промежуточных результатов вычислений. В ЦГФП классический вариант ОЗУ, как правило, не применяется из-за высоких требований к его быстродействию.

Постоянное запоминающее устройство предназначено для хранения постоянных весовых коэффициентов или результатов умножения возможных значений входных сигналов на их коэффициенты. Выполняется обычно на микросхемах памяти.

Рис.4.82. Организация ЗУ в нерекурсивном фильтре второго порядка (двукратном цифровом череспериодном компенсаторе)

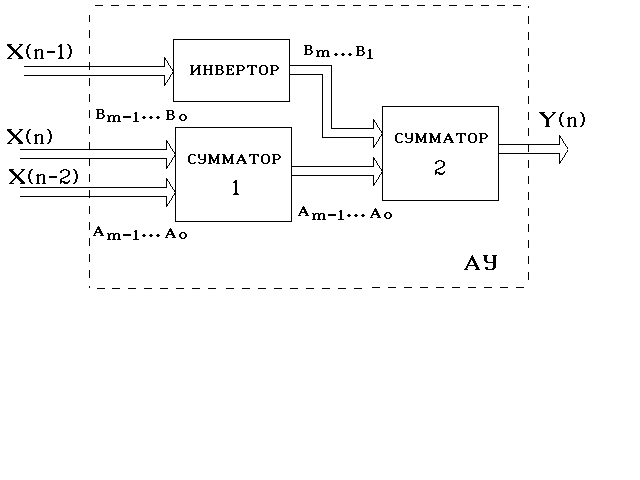

Арифметическое устройство осуществляет вычисление в соответствии с алгоритмом работы ЦГФП. Например, в случае нерекурсивного фильтра второго порядка АУ (рис.4.83) выполняет операцию вида y(n) = x(n) − 2x(n − 1) + x(n − 2) и может быть реализовано на основе двух полных сумматоров.

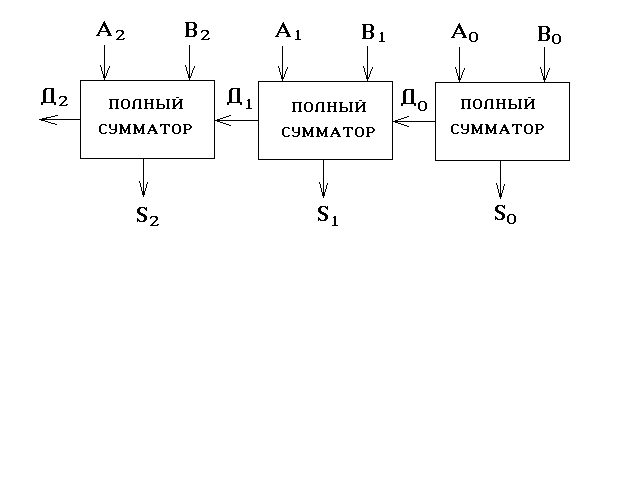

Каждый разряд сумматора (рис.4.84) функционирует в соответствии с табл.4.8.

Рассмотрим особенности технической реализации цифровых гребенчатых фильтров подавления, осуществляющих обработку в частотной области.

Рис.4.83. Арифметическое устройство нерекурсивного фильтра второго порядка

Рис.4.84. Структура сумматора

Таблица 4.8

|

Аi |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

Вi |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

Di-1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

Di |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

Si |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

В ряде случаев бывает целесообразным обрабатывать сигналы в частотной области. Это связано, во-первых, с облегчением задачи синтеза ЦГФП с заданными частотными характеристиками (поскольку сигналы в каждом частотном канале обрабатываются независимо друг от друга) и, во-вторых, с упрощением технической реализации фильтров.

В общем случае включают помимо сумматоров умножители, реализованные либо по классической схеме, либо на базе ПЗУ.

Для перехода в частотную область используется дискретное преобразование Фурье (ДПФ). Для конечного числа N выборок входного сигнала х (n) оно определяется соотношением

![]() (4.84)

(4.84)

k = 0, N − 1, S(k) − комплексная составляющая спектра на k-й частоте.

В общем случае х (n)= х1(n) + j x2(n) (здесь: х1(n), x2(n) − соответственно вещественная и мнимая части сигнала х (n)). Поэтому, обозначая Δφ = 2π /N и учитывая, что exp(-jα) = соs α − jsin α, алгоритм ДПФ можно представить в виде

![]()

![]() (4.85)

(4.85)

Модульное значение k-ой спектральной составляющей ДПФ можно представить в виде

![]() (4.86)

(4.86)

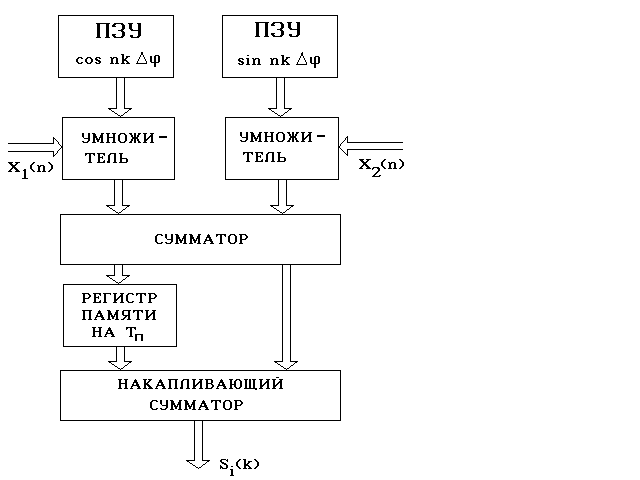

Соотношения (4.85), (4.86) определяют алгоритм работы устройства, обеспечивающего ДПФ входных сигналов в ЦГФП (рис.4.85).

Рис.4.85. Цифровой гребенчатый фильтр подавления, осуществляющий обработку сигналов в частотной области

Рассмотрим особенности технической реализации фильтра подобного типа.

Организация ЗУ входных сигналов зависит от быстродействия АУ, осуществляющего операции ДПФ. Если АУ способно обеспечить вычисление S1(k) и S2(k) за период дискретизации ТД, то ЗУ входных сигналов по принципу построения аналогично ЗУ, рассмотренному в выше. Емкость ЗУ при этом составляет 2Тп FД m (N − 1) бит. Если же быстродействие АУ недостаточно, то операции по вычислению S1(k) и S2(k) выполняются последовательно и необходимость в ЗУ входных сигналов отпадает (их роль выполняют буферные регистры, запоминающие коды выборки входного сигнала на время ТД).

Устройство, осуществляющее ДПФ, может быть реализовано либо на микропроцессорах, либо на типовых элементах дискретной техники. Микропроцессоры целесообразно использовать в случае параллельного (одновременного) выполнения операций ДПФ над всеми N выборками входных сигналов канала дальности.

Рис.4.86. Устройство вычисления действительной части Si(k)

Если по соображениям стоимости и аппаратурных затрат параллельный способ вычисления ДПФ реализовать невозможно, производится последовательное выполнение операций ДПФ по мере поступления выборок входных сигналов.

Устройство, вычисляющее каждую (действительную и мнимую) частей Si(k), в этом случае строится на основе умножителей и накапливающих сумматоров (рис.4.86).

В ПЗУ хранятся значения cos (n k Δφ) и sin (n k Δφ). Исходное состояние регистра памяти на Тп − нулевое.

После поступления на вход устройства первой сигнальной выборки x1(0) и x2 (0) в регистре памяти запоминается на Тп число, равное x1(0) cos (0) + x2 (0) sin (0) = x1(0).

После поступления второй выборки на один вход накапливающего сумматора поступает x1(0) из регистра памяти, а на второй

x1(1) cos (k Δφ) + x2(1) sin (k Δφ).

Таким образом, за i циклов в накапливающем сумматоре формируется число, равное

![]()

Процесс вычисления S1(k) заканчивается после поступления на вход устройства N-й сигнальной выборки, после чего регистр устанавливается в нулевое состояние и начинается процесс вычисления S1(k) для следующих N выборок.

Для реализации устройства, осуществляющего ДПФ, в канале дальности необходимо иметь: 2N накапливающих сумматоров, примерно 3N умножителей и 2Тп.FД.N регистров памяти с разрядностью

m + log2N.

Для обеспечения высокой эффективности работы системы СДЦ необходимо, чтобы число импульсов в пачке удовлетворяло условию М∙(3-4) N. В противном случае можно пропустить пачку полезных импульсов и существенно снизить возможности РЛС по селекции малоподвижных целей.

Вычислитель модулей представляет собой устройство, обеспечивающее для каждой пары S1(k) и S2(k) вычисление по формулам

![]() (аналог

линейного детектора);

(аналог

линейного детектора);

либо

![]() (аналог

квадратичного детектора).

(аналог

квадратичного детектора).

Упрощение его технической реализации обеспечивается использованием алгоритма приближенного вычисления.

В устройстве режекции сигналов ПП осуществляется оценка интенсивности помехи на k-й частоте по сигналам нескольких смежных каналов дальности и деление модуля k-й спектральной составляющей | S(k) | на эту оценку. Подобная операция осуществляется с помощью цифровой ШАРУ.

Функции и структура устройства объединения выходных сигналов зависят от возможности вобуляции Fп в РЛС. Если в процессе облучения цели вобуляция частоты повторения зондирующих импульсов не производится, то выходные сигналы всех каналов устройства режекции ПП сравниваются с порогом и объединяются с помощью схемы ИЛИ.

Порог выбирается из условия обеспечения заданного значения Рлт. Селекция малоподвижных целей в этом случае невозможна.

В случае вобуляции Fп, помимо борьбы со «слепыми» скоростями, появляется возможность селекции малоподвижных целей.

Принцип селекции основан на том, что в случае малоподвижной цели изменение частоты повторения не приводит к существенному изменению частоты пульсаций сигналов на выходе ФД. Поэтому сигнал от такой цели будет находиться в одном и том же частотном канале в отличие от сигнала, отраженного от скоростной цели.

Предельное значение коэффициента подавления ПП в системах СДЦ на основе ДПФ можно оценить по формулам, выведенным при изучении фильтровых и корреляционно-фильтровых систем СДЦ. Для повышения Кпп целесообразно осуществлять предварительное взвешивание пачки из N импульсов. В случае больших N устройство ДПФ цифрового фильтра должно строиться на основе быстрого преобразования Фурье (БПФ). Это реализовано в РЛС 19Ж6.

БПФ представляет собой алгоритм, позволяющий (при параллельной обработке) резко сократить время вычисления ДПФ. Основная идея БПФ состоит в том, что исходная N-точечная последовательность разбивается на две более короткие.

При четном N она разбивается на две N/2 − точечные последовательности.

Для вычисления ДПФ каждой из них потребуется (N/2 − 1)2 умножений, а для вычисления ДПФ исходной последовательности − примерно 2 (N/2)2 = N2/2 комплексных умножений, т. е. вдвое меньше, чем при прямом вычислении. Эту операцию повторяют, т. е. вычисляют два N/4 − точечных ДПФ вместо одного N/2 − точечного до тех пор, пока не дойдут до двухточечных ДПФ. На каждом этапе разбиения объем вычислений сокращается примерно вдвое.

Данный алгоритм БПФ называется алгоритмом с прореживанием по времени, поскольку на каждом этапе временная последовательность разделяется на две последовательности меньшей длины (прореживается). Общее число операций при прямом способе вычислений ДПФ составляет примерно N2, а при использовании БПФ − примерно N log2 N.