- •ПРЕДИСЛОВИЕ

- •1. КЛАССИФИКАЦИЯ И ФУНКЦИОНАЛЬНОЕ НАЗНАЧЕНИЕ СОВРЕМЕННЫХ ИЗДЕЛИЙ МИКРОЭЛЕКТРОНИКИ

- •1.1. Полупроводники

- •1.2. Электронно-дырочной переход (p-n переход)

- •1.3. Полупроводниковые диоды

- •1.4. Биполярные транзисторы

- •1.5. Полевые транзисторы

- •1.6. Элементы интегральных схем

- •1.7. Силовые полупроводниковые приборы

- •2. АНАЛОГОВЫЕ ЭЛЕКТРОННЫЕ УСТРОЙСТВА — УСИЛИТЕЛИ СИГНАЛОВ

- •2.1. Основные параметры и характеристики

- •2.2. Усилители на биполярных транзисторах

- •2.3. Усилители на полевых транзисторах

- •2.4. Усилители с обратной связью

- •2.5. Усилители мощности

- •2.6. Усилители постоянного тока

- •2.7. Дифференциальные усилители

- •2.8. Операционные усилители

- •3. ОСНОВЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

- •3.1. Сигналы цифровых устройств

- •3.2. Алгебра логики

- •3.3. Транзисторные ключи

- •3.3.1. Ключи на биполярных транзисторах

- •3.3.2. МДП-транзисторные ключи

- •3.4. Логические интегральные микросхемы

- •3.4.1. Общие сведения

- •3.4.2. Базовые элементы логических интегральных микросхем

- •3.5. Комбинационные устройства

- •3.5.1. Дешифраторы и шифраторы

- •3.5.2. Распределители и коммутаторы

- •3.5.3. Цифровой компаратор

- •3.6. Последовательностные устройства

- •3.6.1. Триггеры. Общие сведения

- •3.6.2. Транзисторные триггеры

- •3.6.3. Интегральные триггеры

- •3.6.4. Счетчики

- •3.6.5. Регистры

- •3.7. Полупроводниковые запоминающие устройства

- •4. ГЕНЕРАТОРЫ И ФОРМИРОВАТЕЛИ СИГНАЛОВ

- •4.1. Генераторы синусоидальных колебаний

- •4.1.1. Генераторы LC-типа (LC-генераторы)

- •4.1.2. Кварцевые генераторы

- •4.1.3. Генераторы RC-типа (RC-генераторы)

- •4.2. Генераторы прямоугольных импульсов

- •4.3. Генераторы линейно изменяющегося напряжения и тока

- •5. УСТРОЙСТВА И ЭЛЕМЕНТЫ АВТОМАТИКИ

- •5.2. Датчики различной физической природы

- •5.3. Аналоговые компараторы

- •5.4. Устройства сопряжения микропроцессорных систем с объектами

- •5.4.1. Аналого-цифровые преобразователи

- •5.4.2. Цифро-аналоговые преобразователи

- •5.5. Релейные схемы

- •5.5.1. Электромагнитные контактные реле. Общие сведения и основные параметры

- •5.5.2. Электронные реле

- •5.5.3. Фотоэлектронные реле

- •5.5.4. Электронные реле на тиристорах

- •5.6. Магнитные усилители, их назначение и классификация

- •5.7. Микропроцессоры

- •6. ИСТОЧНИКИ ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ

- •6.1. Выпрямители

- •6.1.1. Определение и параметры выпрямителя

- •6.1.2. Схемы выпрямителей

- •6.2. Сглаживающие фильтры

- •6.2.1. Активные фильтры на транзисторах

- •6.2.2. Активные фильтры на операционных усилителях

- •6.3. Стабилизаторы напряжения

- •6.3.1. Виды стабилизаторов и основные характеристики

- •6.3.2. Параметрические стабилизаторы напряжения

- •6.3.3. Стабилитронные интегральные микросхемы (СИМС)

- •6.4. Компенсационные стабилизаторы напряжения

- •6.4.1. Компенсационные стабилизаторы напряжения на транзисторах

- •6.5. Импульсные источники питания

- •6.5.1. Виды и особенности импульсных источников питания

- •6.5.2. Импульсные стабилизаторы напряжения

- •ПРИЛОЖЕНИЕ

- •СПИСОК РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

- •СОДЕРЖАНИЕ

3.4. Логические интегральные микросхемы

3.4.1. Общие сведения

В большинстве современных ЭВМ и цифровых устройств различного назначения обработка информации осуществляется с помощью двоичных чисел, операции над которыми выполняют логические элементы. Схемотехническая реализация современных логических элементов осуществляется на основе интегральных микросхем (ИМС).

По способу кодирования информации различают потенциальные и импульсные интегральные логические элементы (ИЛЭ). Информация, обрабатываемая потенциальными логическими элементами, характеризуется отличающимися потенциальными уровнями. Если логической единице соответствует высокий потенциальный уровень, а логическому нулю — низкий, такую логику называют положительной (позитивной). Наоборот, если логической единице соответствует низкий потенциальный уровень, то говорят об отрицательной (негативной) логике.

В импульсных логических элементах логической единице отвечает наличие импульса, а логическому нулю — его отсутствие.

Параметры логических интегральных микросхем

КпараметрамлогическихинтегральныхмикросхемИМСотносятся: 1) входное и выходное напряжение логической единицы U вх1 и Uвых1 — значения высокого уровня напряжения на входе и выхо-

де микросхемы;

2) входное и выходное напряжение логического нуля U вх0 и Uвых0 — значения низкого уровня напряжения на входе и выходе микросхемы;

3)входной Iвх1 и выходной Iвых1 токи логической единицы, входнойIвх0 и выходной Iвых0 токи логического нуля;

4)логический перепад сигнала ∆Uлог =Uвых1 −Uвых0 , пороговое напряжение Uпор.сх — напряжение на входе, при котором состояние микросхемы изменяется на противоположное;

5)входное сопротивление логической ИМС — отношение приращения входного напряжения к приращению входного тока

(различают Rвх0 и Rвх1 ), выходное сопротивление — отношение приращения выходного напряжения к приращению выходного тока (различают Rвх0 и Rвх1 );

125

6)статистическая помехоустойчивость — максимально допусти-

мое напряжение статистической помехи по высокому Uпом1 и низкому Uпом0 уровням входного напряжения, при котором еще не происходит изменения уровней выходного напряжения микросхемы;

7)средняя потребляемая мощность

Pпотр.ср = (Pпотр0 + Pпотр1 ) 2 ,

2 ,

где Pпотр0 , Pпотр1 — мощности, потребляемые микросхемой в состоянии соответственно логического нуля и логической единицы на выходе;

8)коэффициент объединения по входу Kоб , показывающий, какое число аналогичных логических ИМС можно подключить ко входу данной схемы, и определяющий максимальное число входов логической ИМС;

9)коэффициент разветвления по выходу Kразв , показывающий, какое количество аналогичных нагрузочных микросхем можно подключить к выходу данной ИМС, и характеризующий нагрузочную способность логической ИМС.

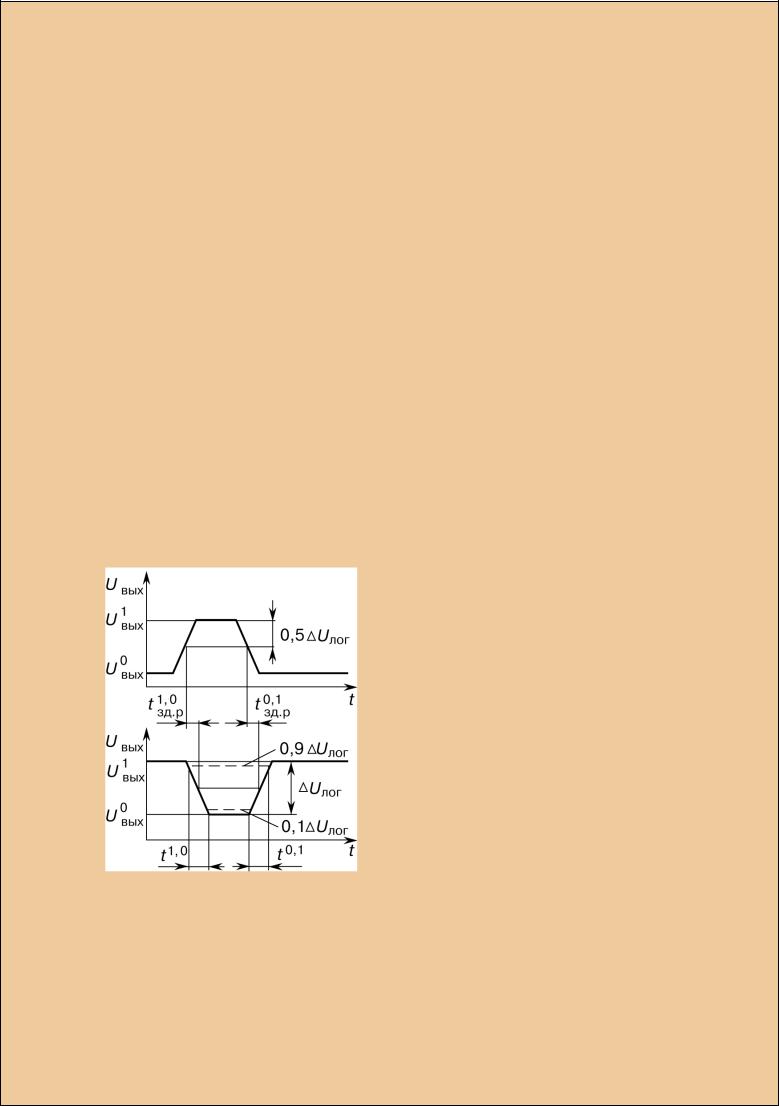

Динамические параметры логических ИМС можно проиллюстрировать с помощью временны′х диаграмм входного и выходно-

|

го напряжений при переключении |

|

|

микросхемы (рис. 3.9). На времен- |

|

|

ны′х диаграммах введены следую- |

|

|

щие обозначения: t 0, 1 — время пе- |

|

|

рехода из состояния логического |

|

|

нуля в состояние логической еди- |

|

|

ницы, измеренное между уровнями |

|

|

0, 1 и 0, 9 логического перепада |

|

|

сигнала; t1, 0 — время перехода из |

|

|

состояния логической |

единицы в |

|

состояние логического нуля, изме- |

|

|

ренное между уровнями 0, 9 и 0, 1 |

|

|

логического перепада |

сигнала; |

|

t1зд, 0.р — время задержки распростра- |

|

Рис. 3.9. Временные диаграммы |

нения сигнала при включении мик- |

|

росхемы, измеренное между уровня- |

||

напряжений при переключении |

ми 0, 5 логического перепада вход- |

|

микросхемы |

ного и выходного сигналов; tзд0, 1.р — |

|

126

время задержки распространения сигнала при выключении микросхемы, измеренное между уровнями 0, 5 логического перепада входного и выходного сигналов.

Среднее время задержки распространения сигнала tзд.р.ср = ( t1,зд0.р + tзд0, .1р )/2.

3.4.2. Базовые элементы логических интегральных микросхем

Логические ИМС объединяют в серии. В основе каждой серии лежит базовый элемент — электрическая схема, выполняющая логическую операцию И—НЕ либо ИЛИ—НЕ. От параметров базового элемента в значительной степени зависят свойства и функциональные возможности разрабатываемой серии логических микросхем.

По принципу построения базовые элементы выпускаемых промышленностью логических ИМС можно выделить в следующие основные группы:

•диодно-транзисторные логические элементы (ДТЛ);

•транзисторно-транзисторные элементы (ТТЛ);

•элементыэмиттерно-связаннойлогики(ЭСЛ) напереключателяхтока;

•элементы с инжекционным питанием (И2Л);

•элементы на МДП-транзисторах.

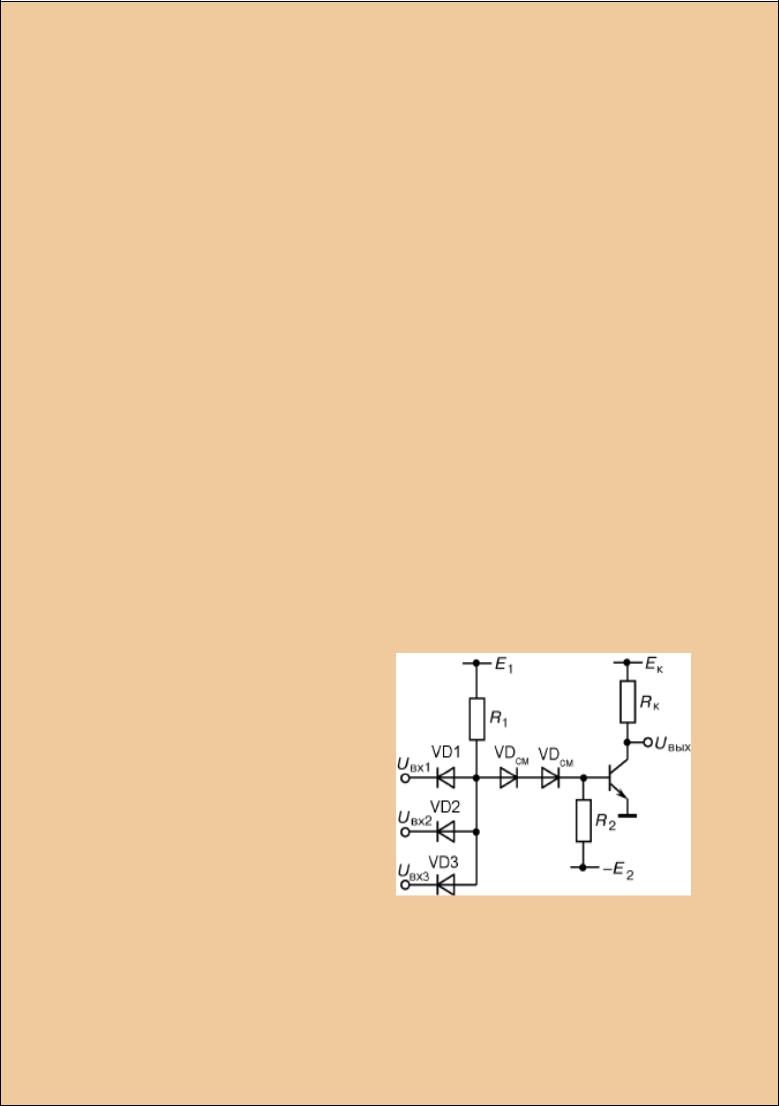

Диодно-транзисторные элементы. Базовый элемент ДТЛ

(рис. 3.10) выполняет логическую операцию И—НЕ. При запира-

нии положительным напряже- |

|

||

нием всех входных диодов уп- |

|

||

равляющий транзистор, вы- |

|

||

полняющий роль |

инвертора, |

|

|

отпирается, формируя на вы- |

|

||

ходе сигнал низкого уровня. |

|

||

Входные |

диоды должны |

|

|

иметь очень малое прямое со- |

|

||

противление. |

В |

противном |

|

случае падение |

напряжения |

|

|

на открытом диоде от проте- |

|

||

каниятокаIд = Ек/ (rпр + R1) мо- |

|

||

жет привести к отпиранию уп- |

Рис. 3.10. Базовый элемент типа ДТЛ |

||

равляющего транзистора. Кро- |

|||

ме того, диоды должны иметь

127

достаточно высокое быстродействие, чтобы не влиять на быстродействиевсеймикросхемы.

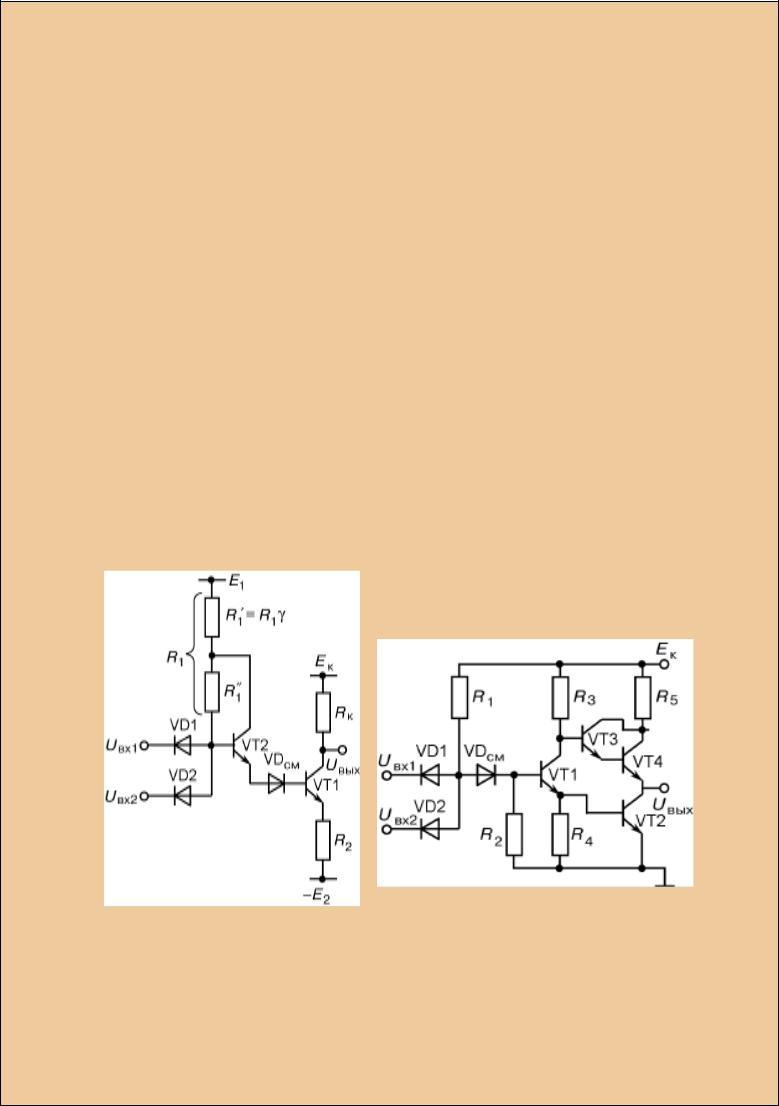

Диоды смещения VDсм должны иметь достаточно большое пороговое напряжение отпирания для повышения помехоустойчивости схемы, а также малое прямое сопротивление для уменьшения потерь в цепи смещения после их отпирания. Для повышения нагрузочной способности элемента ДТЛ один из диодов смещения можно заменить транзистором, коллектор которого подключен к общей точке резисторов R′1 и R″1 (рис. 3.11). Резисторы R′1 и R″1 образуют делитель напряжения с коэффициентом деления γ. Эмиттерный переход транзистора играет роль смещающего диода. С уменьшением коэффициента деления γ возрастает ток эмиттера транзистора VT2 , который является одновременно базовым током управляющего транзистора VT1. При этом увеличивается нагрузочная способность схемы (коэффициент разветвления), но повышается степень насыщения транзистора VT1. Оптимальное значение γ составляет 0,6...0,7.

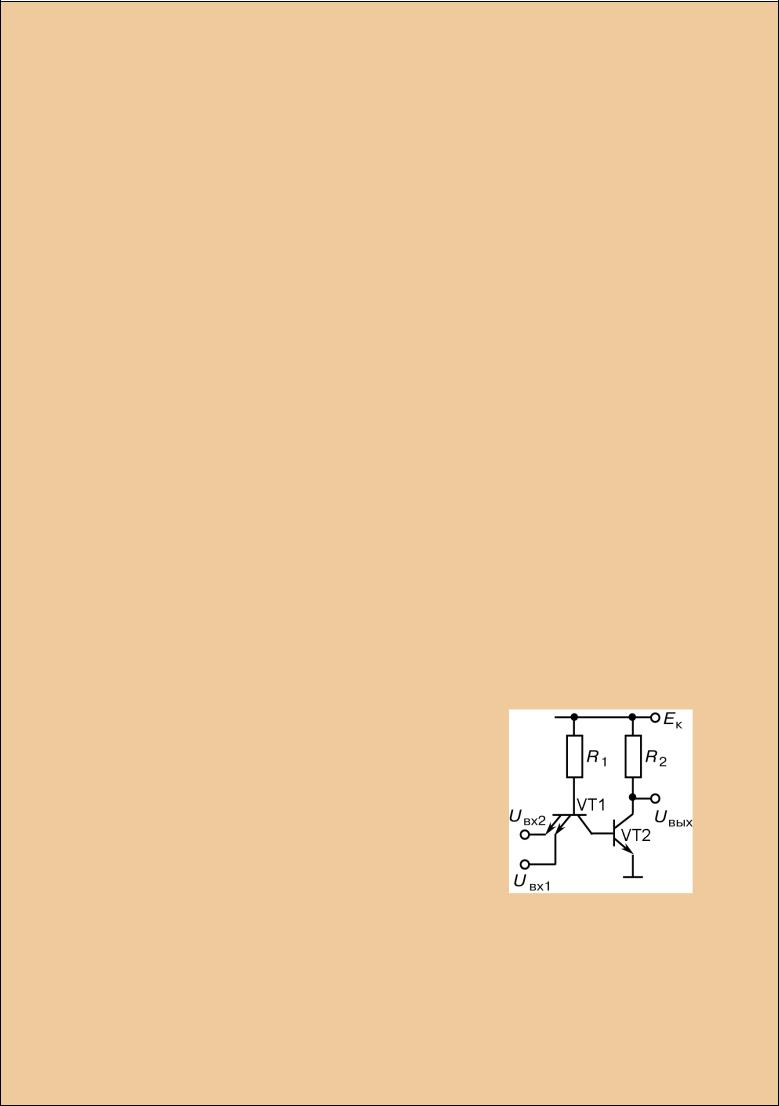

Другой способ повышения нагрузочной способности элемента ДТЛ — использование на выходе схемы так называемого сложного инвертора (рис. 3.12). Сложный инвертор — это двухтактный усилитель мощности на транзисторах, работающих в ключевом

Рис. 3.11. ДТЛ с повышенной |

Рис. 3.12. ДТЛ со сложным инвертором |

|

нагрузочной способностью |

||

|

128

|

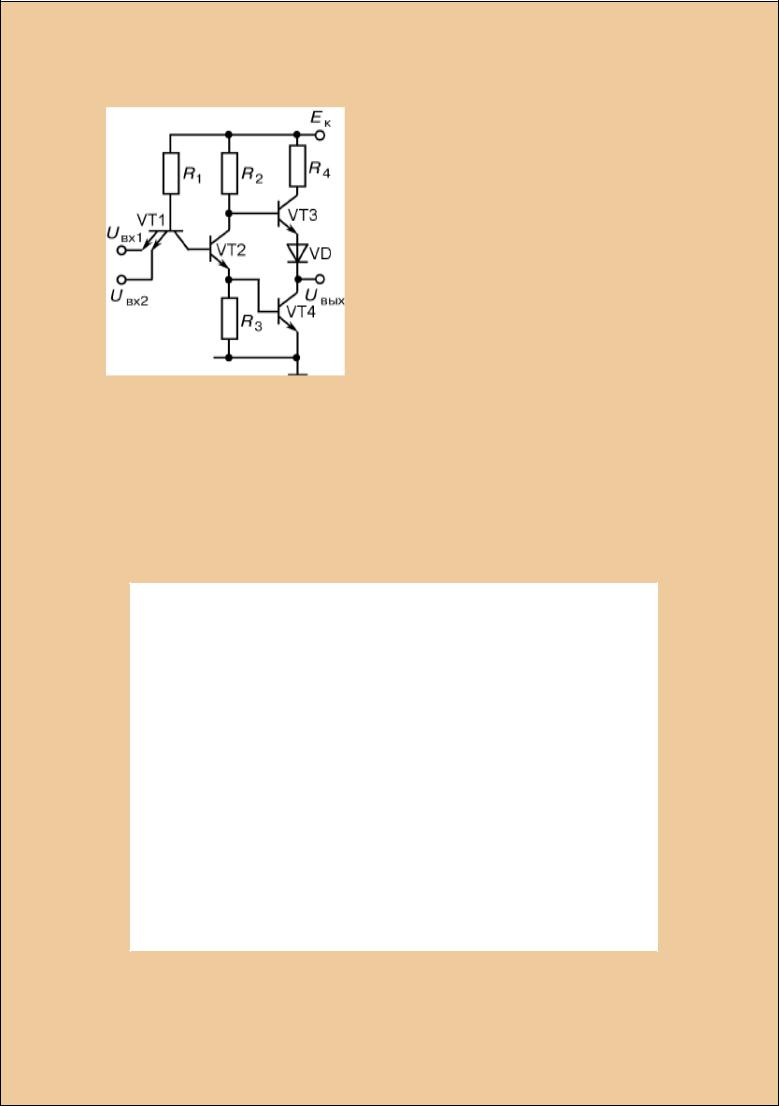

Дополнительными |

компонента- |

|

ми в схеме базового элемента ТТЛ |

|

|

(рис. 3.14) по сравнению со схемой |

|

|

на рис. 3.13 являются транзисторы |

|

|

VT3 и VT4, образующие сложный |

|

|

инвертор. Диод VD повышает порог |

|

|

отпирания транзистора VT3, обеспе- |

|

|

чивая его закрытое состояние при |

|

|

открытом и насыщенном транзисто- |

|

|

ре VT4. Использование сложного |

|

|

инвертора повышает |

помехоустой- |

|

чивость и нагрузочную способность |

|

|

схемы. Базовый элемент (рис. 3.14) — |

|

Рис. 3.14. ТТЛ со сложным |

основной при разработке современ- |

|

инвертором |

ных микросхем ТТЛ-логики. |

|

Наряду с микросхемами ТТЛ-ло- гики разработаны микросхемы типа ТТЛШ, в которых для увеличения быстродействия использованы транзисторы Шотки, работающие в активном режиме. Транзистор Шотки — это обычный интегральный транзистор п-р-п с нелинейной обратной связью, образованной диодом Шотки (рис. 3.15, б)

Рис. 3.15. ТТЛШ-логика (а) со структурами Шотки (б)

130

Базовый элемент микросхемы ТТЛШ-логики изображен на рис. 3.15, а и б.

Ниже рассмотрены две основные разновидности интегральных логических схем на МДП-транзисторах.

Логические схемы на однотипных МДП-транзисторах. В этих схе-

мах используется только один тип транзисторов — либо р-канальные, либо п-канальные. Более широкое применение находят п-канальные МДП-транзисторы, обеспечивающие большее быстродействие. Типо- выесхемыэлементовИЛИ—НЕиИ—НЕнап-канальныхМДП-тран- зисторах приведены на рис. 3.16, а, б. Транзисторы VT1 и VT2 — активные(управляющие), транзисторVT3 — нагрузочный.

При низком уровне напряжения на затворах активных транзисторов VT1 и VT2 (Uвх < U0, где U0 — пороговое напряжение) эти транзисторы будут закрыты и ток стока равен нулю. На выходе устанавливается высокий потенциал U1вх = Е – U0 — уровеньлогической единицы. При входном напряжении на затворах транзисторов VT1 или VT2 больше порогового напряжения U0 соответствующий транзисторотпираетсяиначинаетпротекатьтокстока. Дальнейшее увеличение Uвх приводиткуменьшениюнапряжения Uвых. Дляполучениямалого значения уровня логического нуля необходимо, чтобы сопротивление канала открытого транзистора VT1 (или VT2) было гораздо меньше сопротивления канала транзистора VT3.

Рис. 3.16. Типовые схемы элементов ИЛИ—НЕ (а) и И—НЕ (б) на n-канальных МДП-транзисторах

131

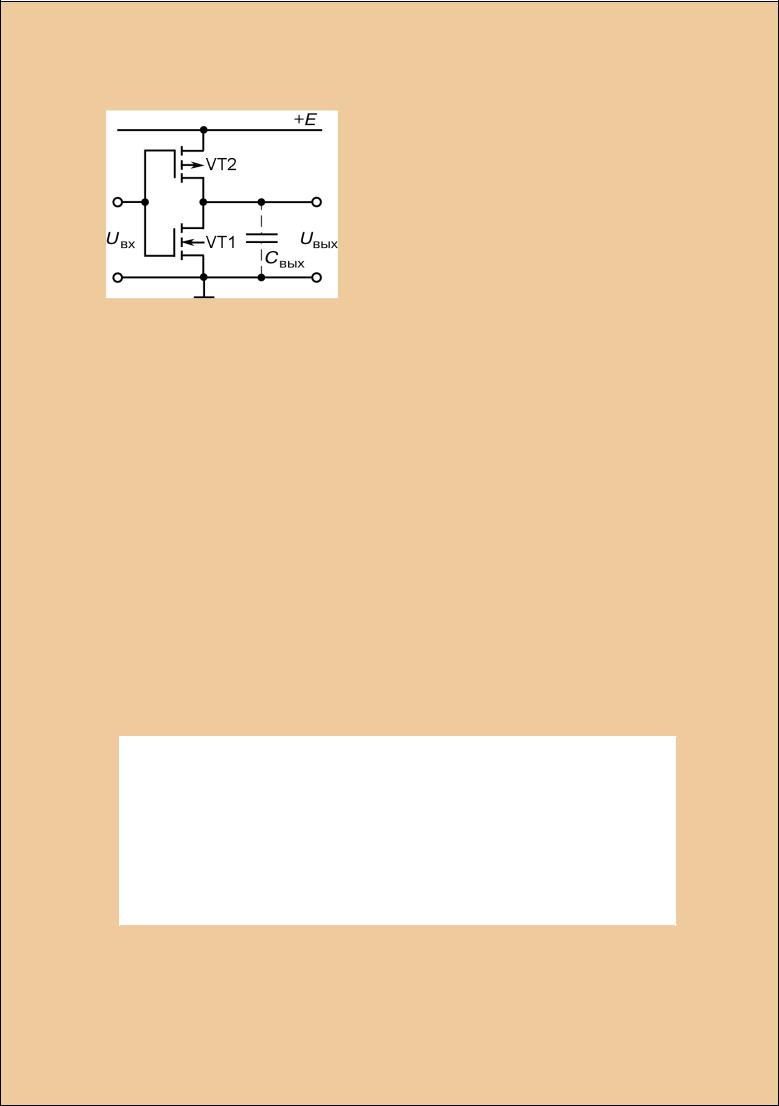

Рис. 3.17. Инвертор на комплиментарных МДП-транзисторах

Логические схемы на комплиментарных МДП-транзисторах (КМДП-

транзисторах). Принципиальная схема инвертора на комплиментарных МДП-транзисторах приведена на рис. 3.17, а стоковые вольт-амперные характеристики — на рис. 3.18. Если Uвх меньше порогового напряжения U01 транзистора VT1, то транзистор VT1 закрыт, а VT2 открыт. Выходное напряжение практически равно напряжению питания Е (рис. 3.18, а):

U вых1 = E − I ут1rк2 ≈ E,

где Iут1 — ток утечки между стоком и истоком закрытого транзистора VT1 (Iут ≈1 нА); rк2 — сопротивление канала открытого транзисто-

ра VT2 (rк2 ≈ 1 кОм).

При Uвх выше порогового напряжения U01 транзистор VT1 открывается, а VT2 закрывается. Выходное напряжение при Uвх ≈ E уменьшается практически до нуля (рис. 3.18, б):

U0вых = Iут2rк1 ≈ 0.

В обоих состояниях ключа, представленных на рис. 3.18, мощность в статистическом режиме практически не потребляется, так как один из транзисторов всегда закрыт, и ток, потребляемый от источника питания, определяется током утечки закрытого ключа. Малая потребляемая мощность — главное достоинство схем на

Рис. 3.18. Стоковые вольт-амперные характеристики транзисторов VT1 и VT2 в закрытом (а) и открытом (б) состояниях

132

КМДП-транзисторах. Это справедливо, однако, лишь для рассмотренного здесь статистического режима при низких частотах переключения. В общем случае (включающем и статику, и динамику) мощность Рпот , потребляемая ключом от источника питания Е, состоит из трех слагаемых:

Рпот = Ремк + Рскв + Рут ,

где Ремк = СвыхE2 fп — мощность, расходуемая на перезаряд выходной схемы Свых , определяемой выражением (3.5); fп — частота переключений схемы; Рскв = IсквEtф fп — мощность, определяемая сквозным током Iскв , который протекает в те моменты времени, когда при переходе схемы из одного состояния в другое открыты оба транзистора (один уже открылся, а второй еще не закрылся); tф — длительность фронта переключающего импульса; Рут = IутE — мощность, потребляемая в статистическом режиме.

При малых частотах переключения, схемы на КМДП-транзис- торах потребляют очень малую мощность. Однако при больших частотах переключения (fп > 1 МГц) эти схемы не имеют преимуществ по сравнению с ТТЛ-схемами.

Двухвходовые логические элементы ИЛИ—НЕ и И—НЕ представлены на рис. 3.19. Общие правила построения логических элементов на КМДП-транзисторах:

• параллельному соединению одного типа транзисторов соответствует последовательное соединение транзисторов другого типа;

Рис. 3.19. Основные логические элементы и их функциональное назначение

133