- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

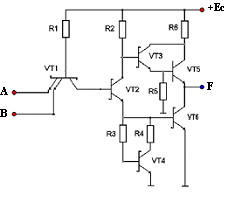

Серия к531

На рисунке 2.7 представлена схема логического элемента серии К531. Повышение быстродействия здесь получено снижением степени насыщения транзисторов за счет применения диодов Шотки, шунтирующих переход коллектор–база насыщенного транзистора. Диоды Шотки имеют существенно меньшее пороговое напряжение открывания, чем переход коллектор–база, поэтому во время действия входного импульса диоды Шотки открываются раньше, чем переход коллектор–база, таким образом предотвращается накопление избыточных зарядов в базовой области транзисторов. Накопления зарядов в самих диодах Шотки не происходит, так как протекающий в них ток вызван переносом основных носителей.

Рис. 2.7. Схема базового логического элемента серии К531

Работа транзисторов Шотки в ненасыщенной области приводит к увеличению падения напряжения на их переходах база–эмиттер, что уменьшает в статическом режиме ток потребления и соответственно потребляемую мощность. В выходном каскаде применена схема Дарлингтона (VT3 и VT5), позволяющая при выключении схемы повышенный ток заряда емкостной нагрузки, что уменьшает время задержки фронта выходного сигнала. Благодаря малому падению напряжения на переходе база–эмиттер транзистора VT3, а также низкому выходному сопротивлению схемы в обоих логических состояниях схема Дарлингтона позволяет получить в микросхемах этой серии более высокий уровень выходного напряжения U1вых.

Преимущества ИС с диодами Шотки: введение диодов Шотки исключает накопление лишних базовых зарядов, увеличивающих время выключения транзистора, и обеспечивает стабильность времени переключения в диапазоне температур. Для получения крутой передаточной характеристики добавляется схема активного выключения, что повышает динамическую помехозащи- щенность при высоком напряжении. Фиксация входов с помощью диодов Шотки уменьшает отрицательные выбросы импульсов напряжения на входе.

Серия К555(LS)

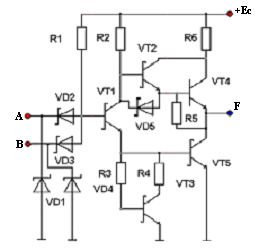

На рисунке 2.8. представлена схема логического элемента серии К555. Базовый логический элемент серии К555 состоит из трех основных каскадов: входного, реализующего функцию И, на диодах VD2,VD3 и резистореR1; фазоразделительного на транзисторе VT1,резисторе коллекторной нагрузкиR3 и резисторно-транзисторной (R3,R4, VT3), эмиттерной нагрузки; выходного двухканального усилителя с верхним плечом, состоящим из транзисторов VT2, VT4, включенных по схеме Дарлингтона с резисторомR5 нагрузки VT2 и ограничительного резистораR6, и нижним плечом на транзисторе VT5.

Рис. 2.8. Схема базового логического элемента серии К555

Входной каскад реализует функцию И при напряжении высокого уровня на входах в положительной логике. При этом выходное напряжение равно входному напряжению минус прямое падение напряжения на входном диоде Шотки: Uвых=U1вх–UD. НапряжениеUвыхпревышает в этом случае суммарное прямое падение напряжения на переходах база – эмиттер транзисторовVT1 и VT5 последующих каскадов и создает ток в базу транзистораVT1 второго каскада из цепи питания через резисторR1. Входной ток элемента соответствует обратному току входных диодов, является втекающим и незначительным. При напряжении низкого уровня на одном из входов (или всех входах) каскада реализуется функция ИЛИ в отрицательной логике. При этом напряжение на выходе каскадаUвых=U0вх+UD. Значения его для этого случая ниже 2Uбэпоследовательно включенных транзисторовVT1, VT5; ток через резисторR1 из цепи питания вытекает на вход элемента. Значение тока определяется разностью напряжения питания и входного напряжения с учетом прямого падения напряжения на входном диоде и номиналом резистораR1:

I0вх = [Ес – (U0вх + UD)]/ R1.

В фазоразделительном каскаде при (при напряжении высокого уровня на входе) протекает ток через его нагрузку. На эмиттерной нагрузке каскада поддерживается напряжение выше напряженияUбэтранзистора VT5, и при этом обеспечивается базовый ток транзистора. На коллекторной нагрузке за счет протекающего через транзисторVT1 тока создается падение напряжения на резистореR2 и напряжение на диодеVD5 ниже 2Uбэтранзисторов верхнего плеча выходного каскада VT2 и VT4. Ток в цепи диодаVD5 – втекающий для фазоразделительного каскада. При напряжении низкого уровня на входе транзисторVT1 устанавливается в 0 по базе и на эмиттерной нагрузке напряжение близко к 0, напряжениеUктранзистораVT1 превышает примерно 2Uбэ транзисторов VT2 и VT4 и обеспечиваются базовые токи этих транзисторов.

Для выходного каскада нижнее плечо (транзистор VT5) находится в открытом состоянии за счет тока, протекающего в базу. Верхнее плечо каскада в этом случае закрыто. Выходное напряжение каскада соответствует напряжению на коллекторе открытого транзистора с диодом Шотки U0вых≈Uбэ– –UD. Ток нагрузки каскада для этого режима – втекающий. В режиме низкого уровня на входе нижнее плечо закрыто, верхнее открыто. Каскад создает на выходе ток, вытекающий в нагрузку, ограничиваемый резисторомR6. Выходное напряжение соответствует высокому уровнюU1вых≈ Ес – (2Uбэ) –IR2.

Резистор R5 верхнего плеча выходного каскада создает необходимое напряжение на базе транзистора VT4 для его открывания. Для уменьшения потребляемой мощности при напряжении высокого уровня на выходе схемы резисторR5 подключен не к общей шине, а к выходу элемента. ДиодVD5, включенный последовательно сR5 и параллельно резистору коллекторной нагрузки фазоразделительного каскадаR2, позволяет уменьшить задержку включения схемы за счет использования части энергии, запасенной в емкости нагрузки, для увеличения тока коллектора транзистораVT1 в переходном режиме. Верхнее плечо выходного каскада выполнено на транзисторах VT2 и VT4 по схеме Дарлингтона, что обеспечивает высокий коэффициент усиления каскада в состоянии высокого уровня, повышает нагрузочную способность схемы и улучшает динамические свойства. Ток заряда емкости нагрузки в динамическом режиме пропорционален току короткого замыкания. Транзистор VT4 реализуется без диодов Шотки, то есть работает в активном режиме. К внешним входам ИС подключены антизвонные диоды, ограничивающие напряжение отрицательных помех.