- •Курс лекций по дисциплине: «цифровая электроника »

- •Минск бгуир 2010 Введение

- •1. Математический аппарат цифровых систем

- •1.1 Основы булевой алгебры

- •1.1.1 Основные положения и законы булевой алгебры

- •Примеры алгебраического метода доказательства теорем:

- •Табличный метод доказательства теоремы де-Моргана

- •1.1.2 Формы представления функций булевой алгебры

- •Булевы функции от двух переменных. Полнота и базис булевых функций.

- •1.2 Логические функции

- •Формы представления логических функции

- •1.3 Минимизация логических функций

- •1.3.1. Минимизация логических функций с помощью карт Карно

- •2. Элементная база цифровых устройств

- •2.1. Особенности структуры и элементной базы цифровых бис и сбис.

- •2.2. Логические элементы и их характеристики

- •2.3. Элементы ттл, ттлш

- •2.3.1. Элемент ттл с простым инвертором.

- •2.3.2. Элемент ттлш с простым инвертором.

- •2.3.3. Схемы ттл/ттлш логики со сложным инвертором

- •Серия к531

- •Серия к1533(als)

- •2.4. Элементы кмоп логики

- •2.4.1. Инвертор на комплементарных транзисторах

- •2.4.2. Логические элементы на комплементарных транзисторах (кмоп).

- •2.4.3. Буферированные кмоп

- •2.4.4. Схема кмоп логики с тремя состояниями выхода

- •2.4.5. Двунаправленный ключ

- •2.5. БиКмоп логика

- •3. Цифровые функциональные узлы комбинационного типа

- •3.3 Основные типы комбинационных узлов

- •3.3.1 Преобразователи кодов

- •3.3.2 Шифраторы и дешифраторы

- •3.3.3 Мультиплексоры и демультиплексоры

- •3.3.4 Комбинационные сумматоры

- •3.3.5 Мажоритарные элементы

- •4. Интегральнье триггеры

- •4.1 Классификация триггеров

- •4.2 Основные типы триггеров

- •4.2.1. Асинхронные и синхронные триггеры.

- •4.2.2. Способы управления триггерами.

- •4.3 Словари переходов

- •5. Функциональные узлы последовательностного типа

- •5.1 Последовательностные устройства

- •5.2 Проектирование последователъно-стных устройств

- •5.3 Счетчики

- •5.3.1. Классификация счетчиков.

- •5.4 Регистры

- •5.4.1. Регистры с параллельным приёмом и выдачей.

- •5.4.2. Регистры с последовательным приёмом или выдачей информации.

- •5.5 Генераторы кодов

2.3. Элементы ттл, ттлш

2.3.1. Элемент ттл с простым инвертором.

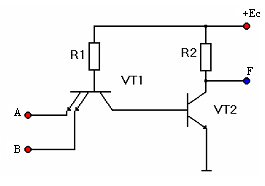

На рис.2.4, представлена схема элемента И-НЕ ТТЛ с простым инвертором. Схема элемента состоит из многоэмиттерного транзистора VT1, выполняющего логическую операцию И, и транзисторного ключа инвертораVT2. На выходе элемента реализуется функция И-НЕ.

Рис. 2.4. Схема элемента И-НЕ ТТЛ с простым инвертором

2.3.2. Элемент ттлш с простым инвертором.

Транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ) является одним из распространенных типов элементной базы цифровых логических микросхем различной степени интеграции, используемых в устройствах цифровой автоматики и вычислительной техники.

Наиболее эффективными для быстродействующих СБИС высокой функциональной сложности являются известные базовые ЛЭ, включающие быстродействующий ключевой транзистор, работающий в ненасыщенном режиме, и схему логической обработки сигналов на входе или выходе ключевого элемента.

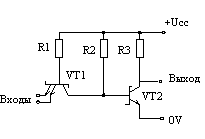

На рис. 2.5,а приведена основная электрическая схема ЛЭ ТТЛШ такой структуры. Схема содержит ключевой транзисторVT2 с диодом Шоттки, в котором ограничение насыщения обеспечивается диодом Шоттки, и логическую схему с функцией И на основе МЭТVTI. Такая схема имеет невысокий порог переключения (UТ ~ 0,5 В), широкий диапазон напряжений питания, высокое быстродействие.

а) б)

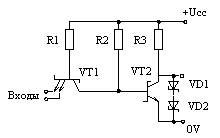

Рис. 2.5. Электрические схемы базовых логических элементов ТТЛШ СБИС:

а – основная схема логического элемента;

б – логический элемент с ограничением перепада напряжений диодами

На рис.2.5,бприведен вариант схем ЛЭ ТТЛШ такого типа с улучшенными характеристиками, а именно повышение быстродействия достигается за счет ограничения логического перепада напряжений ΔUТ, на выходе ЛЭ с помощью диодной цепочкиVDI,VD2.

2.3.3. Схемы ттл/ттлш логики со сложным инвертором

Серия К155

На рисунке 2.6 представлена схема логического элемента серии К155. Схема состоит из следующих каскадов: входного многоэмиттерного транзистора VT1с малым инверсным коэффициентом усиления по току, фазорасщепляющего каскада, постоенного на проходном транзистореVT2 (этот каскад работает в режиме с малым рабочим током и имеет малые емкостиp-nпереходов); выходного каскада (VT4,VT3). ТранзисторVT3 рассчитан на большой рабочий ток и имеет малое время выхода из режима насыщения при переключении схемы. Через этот транзистор стекают на общую шину входные токи ключей-нагрузок.

Рис 2.6. Схема базового логического элемента серии К155

Высокое быстродействие микросхем ТТЛ при большой емкостной нагрузке объясняется тем, что как заряд, так и разряд нагрузочной емкости происходит через низкоомную выходную цепь. Однако при переключении выходных транзисторов есть момент, когда они оба открыты. Из-за этого в цепи питания схемы возникают кратковременные, но мощные импульсы тока, которые могут привести к появлению импульсов помехи. Во избежание этого в аппаратуре, построенной с применением микросхем ТТЛ, необходимо создавать цепи питания цифровых микросхем с малой индуктивностью проводников и предусматривать развязку между соседними платами устройства.

При Uвх1=0 (на один из эмиттеров транзистора VT1 подан потенциал «общий») переход база–эмиттер транзистораVT1 открыт, но образующийся при этом потенциалUбVT1= 0,8 В не может открыть триp-nперехода: база–коллектор транзистораVT1, база–эмиттер транзистораVT2 иVT3 (для отрывания этой цепи необходим потенциал примерно 3∙0,6 = 1,8 В). Потенциал на базе транзистораVT3 близок к нулю, и транзисторVT3 закрыт. Потенциал на коллектореVT2 и базеVT4, близкий к напряжению источника питания +5В, открывает переход база–эмиттер транзистораVT4, вызывая токI1вых.

При увеличении Uвх (на всех эмиттерных входах транзистораVT1) до значения порогового напряженияUпор1=0,8 В транзисторVT2 начинает открываться, но транзисторVT3 ещё закрыт, при дальнейшем увеличенииUвхдоUпор2=1,25 В транзисторVT2 открывается, а транзисторVT3 только начинает открывается.

Дальнейшее увеличение Uвхприводит к увеличению потенциала на базе транзистораVT1 до 1,2 В. Этого вполне достаточно, чтобы открыть два перехода: база–коллектор транзистораVT1 и база–эмиттер транзистораVT2. ТранзисторVT2 открывается, ток через резисторR2 увеличивается, что вызывает уменьшение напряженияUкVT2. В базу выходного транзистора включена корректирующая цепочка, состоящая из резисторов из резисторовR3 иR6 и транзистораVT6. Эта цепочка позволяет получить передаточную характеристику, по форме близкую к прямоугольной, и тем самым повысить помехозащищенность схемы в состоянии «1».

Сопротивление корректирующей цепочки имеет малую зависимость от температуры, что обеспечивает ряд особых свойств схемы. При повышенной температуре (125 оС) время рассасывания для транзистораVT6 мало, что способствует быстрому выключению схемы. Это, в свою очередь, уменьшает импульсный ток короткого замыкания (когда транзисторыVT4 иVT3 открыты одновременно), а значит и динамическую мощность потребления. При пониженной температуре (–60оС) сопротивление корректирующей цепочки высоко, что увеличивает ток включения транзистораVT3 и приводит к уменьшению времени включения схемы.

В выходном каскаде применена схема Дарлингтона (транзисторы VT5 иVT4), позволяющая повысить коэффициент усиления выходного транзистора по току и поэтому обеспечить примерно равные значения выходных сопротивлений схемы при её включении (определяется верхним эмиттерным повторителемVT4) и выключении (определяется насыщенным транзисторомVT3).Это дает почти одинаковые задержки распространения сигнала при включении и выключении схемы.