- •Вводная лекция

- •В.1 Определение, задачи и проблемы

- •В.2 Телемеханические устройства, комплексы и системы

- •В.3 Краткая историческая справка развития телемеханики

- •Часть 1. Сообщения и сигналы

- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •1. ОБЩИЕ СВЕДЕНИЯ О СИГНАЛАХ

- •1.1. Основные типы сигналов

- •1.2. Периодические сигналы

- •1.4. Спектр одиночного прямоугольного импульса

- •2. МОДУЛЯЦИЯ ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ

- •2.1. Амплитудная модуляция

- •2.2. Частотная модуляция (ЧМ)

- •2.3. Фазовая модуляция (ФМ)

- •2.4. Одновременная модуляция по амплитуде и по частоте

- •3. ИМПУЛЬСНАЯ МОДУЛЯЦИЯ

- •3.2. Фазоимпульсная модуляция (ФИМ)

- •3.3. Широтно-импульсная модуляция (ШИМ)

- •4. МАНИПУЛИРОВАННЫЕ СИГНАЛЫ

- •4.1. Амплитудная манипуляция (АМП)

- •4.2. Фазовая манипуляция (ФМП)

- •4.3. Частотная манипуляция (ЧМП)

- •4.4. Двукратная модуляция

- •4.5. Спектры радиоимпульсов

- •5. МОДУЛЯТОРЫ И ДЕМОДУЛЯТОРЫ

- •5.1. Амплитудные модуляторы

- •5.2. Детекторы АМ-сигналов

- •5.3. Модуляторы однополосного сигнала

- •5.4. Детекторы ОАМ-сигнала

- •5.5. Частотные модуляторы

- •5.6. Детекторы ЧМ-сигналов

- •5.7. Фазовые модуляторы

- •5.8. Фазовые детекторы (ФД)

- •5.9. Амплитудно-импульсные модуляторы

- •5.11. Широтно-импульсный модулятор

- •5.12. Демодуляторы ШИМ-сигналов

- •5.13. Фазоимпульсные модуляторы

- •5.14. Детекторы ФИМ-сигналов

- •5.15. Дискретный амплитудный модулятор

- •5.17. Модуляторы ЧМП-сигналов

- •5.19. Модуляторы ФМП-сигналов

- •5.20. Детекторы ФМП-сигнала

- •ЛИТЕРАТУРА

- •Часть 2. Коды и кодирование

- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •1. КОДЫ И КОДИРОВАНИЕ

- •1.1. Основные понятия

- •1.2. Цифровые коды

- •1.3. Простые двоичные коды

- •1.4. Оптимальные коды

- •2. КОРРЕКТИРУЮЩИЕ КОДЫ

- •2.1. Основные понятия

- •2.2. Коды с обнаружением ошибок

- •2.3. Коды с обнаружением и исправлением ошибок

- •2.4. Частотные коды

- •3. ТЕХНИЧЕСКИЕ СРЕДСТВА ПРЕОБРАЗОВАНИЯ ДЛЯ НЕПОМЕХОЗАЩИЩЕННЫХ КОДОВ

- •3.2. Дешифратор двоичного кода в десятичный код

- •3.3. Дешифратор двоично–десятичного кода в десятичный

- •3.4. Преобразователи двоичного кода в двоично–десятичный код и обратно

- •3.5. Преобразователь двоичного кода 8–4–2–1 в самодополняющийся двоично–десятичный код 2–4–2–1

- •3.6. Преобразователь самодополняющего двоично–десятичного кода 2–4–2–1 в двоичный код 8–4–2–1

- •3.7. Преобразователь кода Грея в двоичный код и обратно

- •3.8. Технические средства кодирования и декодирования эффективных кодов

- •3.9. Схемы равнозначности кодов

- •4.1. Кодер и декодер кода с защитой на четность

- •4.2. Кодер и декодер кода с постоянным весом

- •4.3. Кодер и декодер кода с двумя проверками на четность

- •4.4. Кодер и декодер кода с повторением

- •4.5. Кодер и декодер кода с числом единиц, кратным трем

- •4.6. Кодер и декодер инверсного кода

- •4.7. Кодер и декодер корреляционного кода

- •4.8. Кодер и декодер кода Бергера

- •4.10. Кодирующее и декодирующее устройство кода Хемминга

- •4.11. Технические средства умножения и деления многочлена на многочлен

- •4.12. Кодер и декодер циклического кода

- •4.13. Кодер и декодер итеративного кода

- •4.14. Кодер и декодер рекуррентного кода

- •5.1. Кодер и декодер кода на перестановки

- •5.2. Кодер и декодер кода на размещения

- •5.3. Кодер и декодер кода на сочетания

- •5.4. Дешифратор одночастотного кода

- •5.5. Кодер и декодер сменно–качественного кода

- •6. КОДЫ ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ПОСЛЕДОВАТЕЛЬНЫМ КАНАЛАМ СВЯЗИ

- •6.1. Методы кодирования

- •6.2. Шифратор и дешифратор кода Манчестер–2

- •ЗАКЛЮЧЕНИЕ

- •ЛИТЕРАТУРА

- •Часть 3. Линии связи и помехоустойчивость информации

- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •1. ЛИНИИ И КАНАЛЫ СВЯЗИ

- •1.1. Понятие о линии и канале связи

- •1.2. Способы разделения каналов

- •1.3. Проводные линии связи

- •1.4. Использование высоковольтных линий электропередачи (ЛЭП) в качестве линий связи

- •1.6. Радиолинии

- •1.7. Оптические линии связи

- •1.9. Структура линий связи

- •1.10. Сети передачи дискретных сообщений

- •1.11. Расчет основных характеристик цифровых линий связи

- •1.12. Расчет волоконно–оптической линии связи

- •2. ПОМЕХИ И ИХ ХАРАКТЕРИСТИКИ

- •2.1. Общие сведения о помехах

- •2.2. Математическое описание помехи

- •2.3. Виды искажений

- •3. ПОМЕХОУСТОЙЧИВОСТЬ ПЕРЕДАЧИ ДИСКРЕТНЫХ СООБЩЕНИЙ

- •3.1. Основные понятия

- •3.2. Помехоустойчивость передачи дискретных элементарных сигналов

- •3.3. Приём с зоной стирания

- •3.4. Помехоустойчивость двоичных неизбыточных кодов

- •3.5. Помехоустойчивость кодов с обнаружением ошибок

- •3.7. Помехоустойчивость систем с дублированием сообщений

- •3.8. Помехоустойчивость систем с обратными каналами связи

- •4. ПОМЕХОУСТОЙЧИВОСТЬ ПЕРЕДАЧИ НЕПРЕРЫВНЫХ СООБЩЕНИЙ

- •4.1. Общие соображения

- •4.2. Помехоустойчивость непрерывных методов модуляции

- •4.3. Помехоустойчивость импульсных методов модуляции

- •4.4. Потенциальная помехоустойчивость сложных видов модуляции

- •5. МЕТОДЫ ПОВЫШЕНИЯ ПОМЕХОУСТОЙЧИВОСТИ

- •5.1. Методы повышения помехоустойчивости передачи дискретных сообщений

- •5.2. Методы повышения помехоустойчивости передачи непрерывных сообщений

- •ЛИТЕРАТУРА

- •ПРИЛОЖЕНИЕ

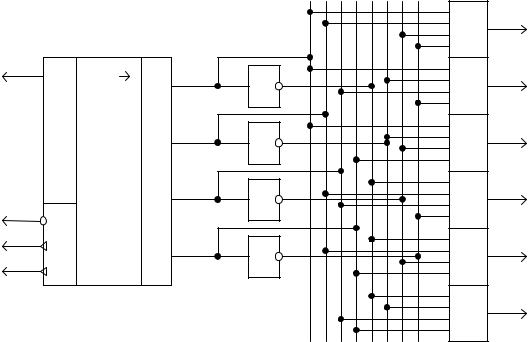

Подлежащие кодированию сообщения заносятся в ОЗУ DD1 и с выходов x1, x2 , x3, x4 , x5 , x6 поступают на кодер, который собран на элементах

DD2…DD5. Входы этих элементов соединены с выходами ОЗУ DD1, в соответствии с выражениями (4.2). Закодированная кодовая комбинация y4 , y3 , y2 , y1 записывается в регистр DD6, а затем последовательно выдвига-

ется в линию связи.

Функциональная схема декодера для кода C42 приведена на рис. 4.6.

С и г н а л ы управления

|

|

|

|

& |

X1 |

|

Вход |

|

|

|

DD6.1 |

|

|

|

|

1 |

& |

X2 |

||

S1 |

RG |

Y1 |

||||

|

|

|

||||

F*(Y) |

|

DD2 |

DD6.2 |

|

||

|

|

|

||||

|

|

Y2 |

1 |

& |

X3 |

|

|

|

DD3 |

DD6.3 |

|

||

|

|

|

|

|||

|

|

Y3 |

1 |

& |

X4 |

|

|

|

DD4 |

DD6.4 |

|

||

PE |

|

|

|

|||

|

|

|

|

X5 |

||

C1 |

DD1 |

Y4 |

1 |

& |

||

C2 |

DD5 |

DD6.5 |

|

|||

|

|

|||||

|

|

|

||||

|

|

|

|

& |

X6 |

|

|

|

|

|

DD6.6 |

|

|

|

|

Рис. 4.6. |

Декодер кода С 2 |

|

|

|

|

|

|

4 |

|

|

Выход

Кодовая комбинация F*(Y) из линии связи поступает в приемный регистр DD1 и далее на собственно сам дешифратор, собранный на элементах И DD6.1…DD6.6, входы которых заведены в соответствии с выражениями (4.1). На выходе схем И DD6.1…DD6.6 получаем сигналы, соответствующие передаваемым сообщениям x1,..., x6 . Нетрудно видеть, что данная схема обладает за-

щитным отказом, т.е. при поступлении на вход кодовых комбинаций, содержащих количество единиц, отличное от двух, ни на одном из выходов x1,..., x6

сигнала не будет.

4.3. Кодер и декодер кода с двумя проверками на четность

Принцип образования кодовых комбинаций в данном коде описан в под-

разд. 2.2.5.

106

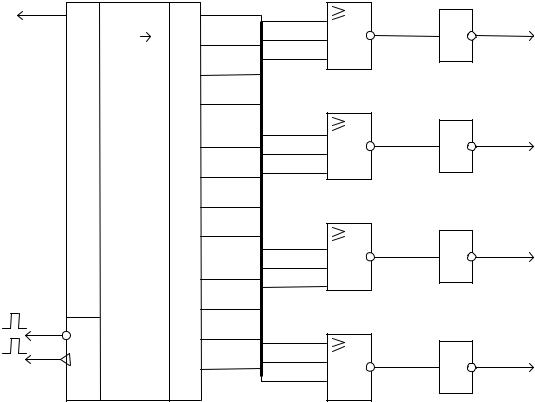

Кодирующее устройство для k = 6 показано на рис. 4.7. Оно состоит из входного регистра DD1, схем контроля четности DD2, DD3 и преобразователя параллельного кода в последовательный DD4.

Схемой DD2 формируется первый контрольный разряд r1, дополняющий до четности всех информационных разрядов, а схемой DD3 формируется второй контрольный разряд r2 , дополняющий до четности всех нечетных инфор-

мационных разрядов, т.е. k1, k3 и. k5

K1

K2

K3

ВходK4

K5

K6 Сигналы управления

D0 |

RG |

K1 |

M2 |

|

|

X1 |

MS |

D1 |

|

|

|

r1 |

|

X2 |

|

|

K2 |

|

|

X3 |

|

||

|

|

|

|

|

|

||

D2 |

|

K3 |

|

|

|

X4 |

|

D3 |

|

DD2 |

|

|

X5 |

Выход |

|

|

K4 |

|

|

X6 |

|||

D4 |

|

|

|

|

X7 |

|

|

|

|

|

|

|

F(X) |

||

D5 |

|

K5 |

|

|

1 |

X8 |

|

|

M2 |

|

S0 |

|

|||

|

|

|

|

|

|||

PE |

|

K6 |

|

2 |

|

||

|

|

|

S1 |

|

|||

|

|

|

3 |

|

|||

C1 |

|

|

|

r2 |

S3 |

|

|

|

|

|

|

|

|||

DD1 |

|

DD3 |

|

_ |

DD4 |

||

C2 |

|

|

|

E |

|||

|

|

|

|

|

2 |

1 |

1 |

|

2 |

|||

СТ |

2 |

||

от |

4 |

3 |

|

|

Рис. 4.7. Кодер кода с двумя проверками на четность

Декодирующее устройство рассматриваемого кода приведено на рис. 4.8. Оно состоит из приемного регистра DD1, двух схем контроля четности DD2 и DD3, определителя синдрома DD4, формирователя сигнала “сброс” DD5 и схем вывода информационных символов DD6…DD11.

Если кодовая комбинация F*(x) поступает в приемник без искажений, то на инверсном выходе схемы контроля четности DD2, осуществляющей проверку k1 k2 k3 k4 k5 k6 r1, появится 1. На инверсном выходе схемы

контроля четности DD3, осуществляющей проверку k1 k3 k5 r2 , тоже бу-

дет 1. Эти оба сигнала поступят на вход определителя синдрома DD4, и единичный сигнал с его выхода дает разрешение на вывод получателю информа-

107

ционных символов через элементы И DD6…DD11. Если F*(x) была искажена, |

|||||||||||

то на инверсном выходе одной или двух схем контроля четности будет сигнал |

|||||||||||

0, что вызовет запрет на выдачу информационных символов получателю ин- |

|||||||||||

формации, а 1 на выходе DD5 вызовет сброс регистра DD1 в исходное положе- |

|||||||||||

ние. Следует отметить, что опрос определителя синдрома DD4 происходит на |

|||||||||||

девятом такте, т.е. после приема всей кодовой комбинации из линии связи. |

|||||||||||

|

|

|

|

|

|

1 |

M2 |

|

|

|

|

|

|

|

|

|

|

2 |

|

1 |

|

|

|

Вход |

|

|

|

K1 |

1 |

3 |

|

|

& |

K1 |

|

|

|

|

4 |

|

|

||||||

|

S1 |

RG |

X1 |

K2 |

2 |

5 |

|

|

9 |

|

|

F*(X) |

6 |

DD2 |

& |

|

DD6 |

|

|||||

|

|

|

X2 |

K3 |

3 |

7 |

2 |

& |

K2 |

||

|

|

|

X3 |

|

|

9 |

|||||

|

|

|

K4 |

4 |

1 |

|

|

9 |

DD7 |

|

|

|

|

|

X4 |

K5 |

5 |

3 |

M2 |

DD4 |

|

|

|

|

|

|

3 |

|

|

||||||

|

|

|

X5 |

K6 |

6 |

5 |

|

|

& |

K3 |

|

|

|

|

X6 |

r1 |

7 |

8 |

DD3 |

F |

9 |

DD8 |

|

|

|

|

|

|

|||||||

|

|

|

X7 |

r2 |

8 |

|

|

|

4 |

& |

K4 |

|

|

|

X8 |

|

|

DD5 |

|||||

|

PE |

|

|

|

9 |

||||||

Сигналы управления |

C1 |

|

|

|

|

|

|

|

|

DD9 |

K5 Выход |

|

|

|

|

|

|

|

5 |

& |

|||

C2 |

DD1 |

|

|

|

9 ТИ |

|

|||||

|

R |

|

|

|

|

9 |

DD10 |

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

6 |

& |

K6 |

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

DD11 |

|

|

|

Рис. 4.8. Декодирующее устройство кода с двумя |

|

||||||||

|

|

|

|

проверками на четность |

|

|

|

||||

4.4. Кодер и декодер кода с повторением

Как известно из подразд. 2.2.6, существуют две разновидности этого кода. Первая – это когда исходная комбинация повторяется m раз и вторая – когда каждый элемент повторяется m раз. Кодирующие устройства для первого и второго вариантов представлены на рис. 4.9 и 4.10 соответственно.

Кодер рис. 4.9 работает следующим образом. Кодовая комбинация, подлежащая кодированию, заносится в регистр DD1. По сигналу “Пуск” триггер DD2 устанавливается в 1, открывается схема И DD4, и тактовые импульсы от генератора DD3 поступают на вход счетчика тактов DD5 и одновременно на вход C2 кольцевого регистра DD1. Исходная кодовая комбинация выдвигается на выход m (в данном случае m = 3) раз. Число повторений устанавливается счетчиком тактов DD5. После того как счетчиком DD5 будет зафиксировано 3k

108

тактов, на выходе счетчика DD5 появляется сигнал, который устанавливает триггер DD2 в исходное положение и схема готова к кодированию следующего сообщения.

|

|

|

|

|

|

S1 |

RG |

K1 |

|

|

|

K1 |

|||||

|

|

|

|

|

||||

|

|

|

D0 |

|

||||

|

|

|

|

|

||||

|

|

|

K2 |

|

|

|||

Вход |

|

D1 |

|

K2 |

||||

|

K3 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

K4 |

D2 |

|

|

||

|

|

|

D3 |

|

|

|||

|

|

|

|

|

|

|

K3 |

|

|

|

|

|

упр |

_ |

|

||

|

|

|

|

|

|

|||

|

|

|

|

зап |

PE |

|

Выход |

|

|

|

|

|

|

||||

|

|

|

|

C1 |

|

|||

|

|

|

|

такт |

DD1 |

K4 |

||

|

|

|

|

|||||

|

|

|

|

|

|

C2 |

F(X) |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

"Пуск" |

|

|

|

|

|

|

|

|

|

|

|

||

S |

T |

|

|

|

|

& |

|

|

C |

CT |

|

||

"Cтоп" |

|

|

|

|

|

|

|

|

|

3K |

|

||

R |

|

|

|

|

|

DD4 |

|

|

|

DD5 |

|

||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD2 |

|

|

|

|

|

|

|

|

||

|

|

|

G |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD3 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.9. Кодер кода с трехкратным повторением исходной комбинации

|

|

|

|

|

|

D0 |

|

K1 |

|

|

|

K1 |

RG |

|

|||||

|

|

D1 |

K1 |

|

|||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

D2 |

|

K1 |

|

|

|

K2 |

D3 |

|

K2 |

|

|||

|

|

D4 |

|

|

|||||

Вход |

|

|

|||||||

|

K2 |

|

|||||||

D5 |

|

|

|||||||

|

|

K3 |

D6 |

|

K2 |

|

|||

|

|

|

|

|

|||||

|

|

D7 |

|

|

|

||||

|

|

|

|

|

|

|

K3 |

|

|

|

|

|

|

|

|

D8 |

|

|

|

|

|

|

|

|

|

|

K3 |

|

|

|

|

|

|

|

|

D9 |

|

|

|

|

|

K4 |

|

K3 |

|

||||

|

|

D10 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D11 |

|

K4 |

|

|

|

|

|

упр |

_ |

|

K4 |

Выход |

|

|

|

|

|

зап |

PE |

|

K4 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

C1 |

DD1 |

|

F(X) |

||

|

|

|

|

||||||

|

|

|

|

такт |

|

||||

|

|

|

|

C2 |

|

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Рис. 4.10. Кодер кода с трех кратным повторением каждого элемента исходной комбинации

Например, если на вход поступило сообщение G(x) = 1101 = k4k3k2k1, то в

результате трехкратной передачи в линию связи поступит кодовая комбинация

F(x) = 110111011101.

Вкодере рис. 4.10 каждый символ ki исходной комбинации записывается

втри рядом стоящих ячейки. Таким образом, после подачи 3k импульсов на

вход С2 регистра DD1 на выход поступит кодовая комбинация k4k4k4k3k3k3k2k2k2k1k1k1 . Например, если подлежала кодированию сообщение

G(x) = k4k3k2k1 = 1001, то в линию связи поступит кодовая комбинация

F(x) =111 000 000 111.

Декодирование заключается в обнаружении и исправлении ошибок. Для исправления ошибок применяется мажоритарный принцип, т.е. за истинное значение информационного символа принимается то, которое большее число

109

раз встречается в этом информационном и соответствующих ему контрольных символах. При трехкратном повторении решение принимается по двум символам из трех.

Как указано в подразд. 2.2.6 наибольшее применение нашел код с повторением комбинаций, как обеспечивающий более высокую помехоустойчивость. Поэтому декодирующее устройство рассмотрим для этого случая, схема которого приведена на рис. 4.11 для k = 4, m = 3 и n = 12.

Кодовая комбинация F * (x) из линии связи в последовательном коде заносится в регистр DD1. С выхода DD1 каждый информационный символ ki ,

поступает на один из входов трехвходового мажоритарного элемента, на остальные два входа подаются соответствующие ему контрольные символы.

Вход |

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

S1 |

|

K1 |

2 |

0 |

1 |

1 |

|

|

||||

F*(X) |

|

RG |

K2 |

0 |

2 |

5 |

0 |

DD2 |

|

DD6 |

|

K1 |

|

|

|

|

1 |

3 |

9 |

1 |

|

|

|

|

|||

|

|

|

K3 |

|

|

|

|

|

|

|

|

||

|

|

|

K4 |

1 |

4 |

|

|

2 |

|

|

|

|

В |

|

|

|

|

0 |

5 |

2 |

0 |

1 |

1 |

0 |

|

||

|

|

|

K1 |

6 |

0 |

|

|

|

|

K2 |

ы |

||

|

|

|

0 |

6 |

10 |

0 |

DD3 |

|

DD7 |

|

х |

||

|

|

|

K2 |

1 |

7 |

|

|

|

|

|

|

|

о |

|

|

|

K3 |

|

|

|

|

|

|

|

д |

||

|

|

|

1 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

K4 |

3 |

1 |

2 |

0 |

1 |

1 |

K3 |

|

||

|

|

|

|

1 |

9 |

7 |

1 |

DD4 |

|

DD8 |

|

|

|

|

|

|

K1 |

11 |

1 |

|

|

|

|

||||

упр |

|

|

K2 |

0 |

10 |

|

|

|

|

|

|

|

|

PE |

|

K3 |

1 |

11 |

4 |

1 |

|

|

|

|

|

|

|

такт |

|

2 |

0 |

& |

1 |

|

|

||||||

C2 |

DD1 K4 |

0 |

12 |

8 |

1 |

K4 |

|

||||||

|

12 |

0 |

DD5 |

|

DD9 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||

DD1 K155ИР1 - 3 шт, DD2...DD5 K533ЛП3 (K1533ЛП3),

DD6...DD9 K155ЛН1

Рис. 4.11. Функциональная схема декодера кода с 3–кратным повторением исходной комбинации

110