- •Вводная лекция

- •В.1 Определение, задачи и проблемы

- •В.2 Телемеханические устройства, комплексы и системы

- •В.3 Краткая историческая справка развития телемеханики

- •Часть 1. Сообщения и сигналы

- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •1. ОБЩИЕ СВЕДЕНИЯ О СИГНАЛАХ

- •1.1. Основные типы сигналов

- •1.2. Периодические сигналы

- •1.4. Спектр одиночного прямоугольного импульса

- •2. МОДУЛЯЦИЯ ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ

- •2.1. Амплитудная модуляция

- •2.2. Частотная модуляция (ЧМ)

- •2.3. Фазовая модуляция (ФМ)

- •2.4. Одновременная модуляция по амплитуде и по частоте

- •3. ИМПУЛЬСНАЯ МОДУЛЯЦИЯ

- •3.2. Фазоимпульсная модуляция (ФИМ)

- •3.3. Широтно-импульсная модуляция (ШИМ)

- •4. МАНИПУЛИРОВАННЫЕ СИГНАЛЫ

- •4.1. Амплитудная манипуляция (АМП)

- •4.2. Фазовая манипуляция (ФМП)

- •4.3. Частотная манипуляция (ЧМП)

- •4.4. Двукратная модуляция

- •4.5. Спектры радиоимпульсов

- •5. МОДУЛЯТОРЫ И ДЕМОДУЛЯТОРЫ

- •5.1. Амплитудные модуляторы

- •5.2. Детекторы АМ-сигналов

- •5.3. Модуляторы однополосного сигнала

- •5.4. Детекторы ОАМ-сигнала

- •5.5. Частотные модуляторы

- •5.6. Детекторы ЧМ-сигналов

- •5.7. Фазовые модуляторы

- •5.8. Фазовые детекторы (ФД)

- •5.9. Амплитудно-импульсные модуляторы

- •5.11. Широтно-импульсный модулятор

- •5.12. Демодуляторы ШИМ-сигналов

- •5.13. Фазоимпульсные модуляторы

- •5.14. Детекторы ФИМ-сигналов

- •5.15. Дискретный амплитудный модулятор

- •5.17. Модуляторы ЧМП-сигналов

- •5.19. Модуляторы ФМП-сигналов

- •5.20. Детекторы ФМП-сигнала

- •ЛИТЕРАТУРА

- •Часть 2. Коды и кодирование

- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •1. КОДЫ И КОДИРОВАНИЕ

- •1.1. Основные понятия

- •1.2. Цифровые коды

- •1.3. Простые двоичные коды

- •1.4. Оптимальные коды

- •2. КОРРЕКТИРУЮЩИЕ КОДЫ

- •2.1. Основные понятия

- •2.2. Коды с обнаружением ошибок

- •2.3. Коды с обнаружением и исправлением ошибок

- •2.4. Частотные коды

- •3. ТЕХНИЧЕСКИЕ СРЕДСТВА ПРЕОБРАЗОВАНИЯ ДЛЯ НЕПОМЕХОЗАЩИЩЕННЫХ КОДОВ

- •3.2. Дешифратор двоичного кода в десятичный код

- •3.3. Дешифратор двоично–десятичного кода в десятичный

- •3.4. Преобразователи двоичного кода в двоично–десятичный код и обратно

- •3.5. Преобразователь двоичного кода 8–4–2–1 в самодополняющийся двоично–десятичный код 2–4–2–1

- •3.6. Преобразователь самодополняющего двоично–десятичного кода 2–4–2–1 в двоичный код 8–4–2–1

- •3.7. Преобразователь кода Грея в двоичный код и обратно

- •3.8. Технические средства кодирования и декодирования эффективных кодов

- •3.9. Схемы равнозначности кодов

- •4.1. Кодер и декодер кода с защитой на четность

- •4.2. Кодер и декодер кода с постоянным весом

- •4.3. Кодер и декодер кода с двумя проверками на четность

- •4.4. Кодер и декодер кода с повторением

- •4.5. Кодер и декодер кода с числом единиц, кратным трем

- •4.6. Кодер и декодер инверсного кода

- •4.7. Кодер и декодер корреляционного кода

- •4.8. Кодер и декодер кода Бергера

- •4.10. Кодирующее и декодирующее устройство кода Хемминга

- •4.11. Технические средства умножения и деления многочлена на многочлен

- •4.12. Кодер и декодер циклического кода

- •4.13. Кодер и декодер итеративного кода

- •4.14. Кодер и декодер рекуррентного кода

- •5.1. Кодер и декодер кода на перестановки

- •5.2. Кодер и декодер кода на размещения

- •5.3. Кодер и декодер кода на сочетания

- •5.4. Дешифратор одночастотного кода

- •5.5. Кодер и декодер сменно–качественного кода

- •6. КОДЫ ДЛЯ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ПОСЛЕДОВАТЕЛЬНЫМ КАНАЛАМ СВЯЗИ

- •6.1. Методы кодирования

- •6.2. Шифратор и дешифратор кода Манчестер–2

- •ЗАКЛЮЧЕНИЕ

- •ЛИТЕРАТУРА

- •Часть 3. Линии связи и помехоустойчивость информации

- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •1. ЛИНИИ И КАНАЛЫ СВЯЗИ

- •1.1. Понятие о линии и канале связи

- •1.2. Способы разделения каналов

- •1.3. Проводные линии связи

- •1.4. Использование высоковольтных линий электропередачи (ЛЭП) в качестве линий связи

- •1.6. Радиолинии

- •1.7. Оптические линии связи

- •1.9. Структура линий связи

- •1.10. Сети передачи дискретных сообщений

- •1.11. Расчет основных характеристик цифровых линий связи

- •1.12. Расчет волоконно–оптической линии связи

- •2. ПОМЕХИ И ИХ ХАРАКТЕРИСТИКИ

- •2.1. Общие сведения о помехах

- •2.2. Математическое описание помехи

- •2.3. Виды искажений

- •3. ПОМЕХОУСТОЙЧИВОСТЬ ПЕРЕДАЧИ ДИСКРЕТНЫХ СООБЩЕНИЙ

- •3.1. Основные понятия

- •3.2. Помехоустойчивость передачи дискретных элементарных сигналов

- •3.3. Приём с зоной стирания

- •3.4. Помехоустойчивость двоичных неизбыточных кодов

- •3.5. Помехоустойчивость кодов с обнаружением ошибок

- •3.7. Помехоустойчивость систем с дублированием сообщений

- •3.8. Помехоустойчивость систем с обратными каналами связи

- •4. ПОМЕХОУСТОЙЧИВОСТЬ ПЕРЕДАЧИ НЕПРЕРЫВНЫХ СООБЩЕНИЙ

- •4.1. Общие соображения

- •4.2. Помехоустойчивость непрерывных методов модуляции

- •4.3. Помехоустойчивость импульсных методов модуляции

- •4.4. Потенциальная помехоустойчивость сложных видов модуляции

- •5. МЕТОДЫ ПОВЫШЕНИЯ ПОМЕХОУСТОЙЧИВОСТИ

- •5.1. Методы повышения помехоустойчивости передачи дискретных сообщений

- •5.2. Методы повышения помехоустойчивости передачи непрерывных сообщений

- •ЛИТЕРАТУРА

- •ПРИЛОЖЕНИЕ

Таблица 3.2

Состояния шифратора ИВ1

Входы |

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 |

|

I1 |

|

I 2 |

|

|

I3 |

I 4 |

I5 |

I 6 |

I 7 |

I8 GS |

|

|

A0 |

|

|

A1 |

|

|

A2 |

|

|

E0 |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

1 |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

1 |

|

1 |

|

1 |

|

|

1 |

|

|

1 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

|

1 |

|

|

0 |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

0 |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

0 |

|

0 |

|

0 |

|

0 |

|

|

0 |

|

|

1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

0 |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

0 |

|

1 |

|

0 |

|

1 |

|

0 |

|

|

0 |

|

|

1 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

0 |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

0 |

|

1 |

|

1 |

|

0 |

|

0 |

|

1 |

|

|

0 |

|

|

1 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

0 |

|

|

x |

|

|

x |

|

|

x |

|

|

x |

|

0 |

|

1 |

|

1 |

|

1 |

|

0 |

|

1 |

|

1 |

|

|

0 |

|

|

1 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

0 |

|

|

x |

|

|

x |

|

|

x |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

0 |

|

0 |

|

0 |

|

|

1 |

|

|

1 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

0 |

|

|

x |

|

|

x |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

0 |

|

1 |

|

0 |

|

|

1 |

|

|

1 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

0 |

|

|

x |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

0 |

|

0 |

|

1 |

|

|

1 |

|

|

1 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

0 |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

0 |

|

1 |

|

1 |

|

|

1 |

|

|

1 |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Приоритет в том случае, если несколько входов получили активные уровни, будет иметь «старший» среди них по номеру. Высший приоритет у

входа I8 .

Используя совместно выход E0 и разрешающий вход E1, можно строить многоразрядные приоритетные шифраторы.

3.2. Дешифратор двоичного кода в десятичный код

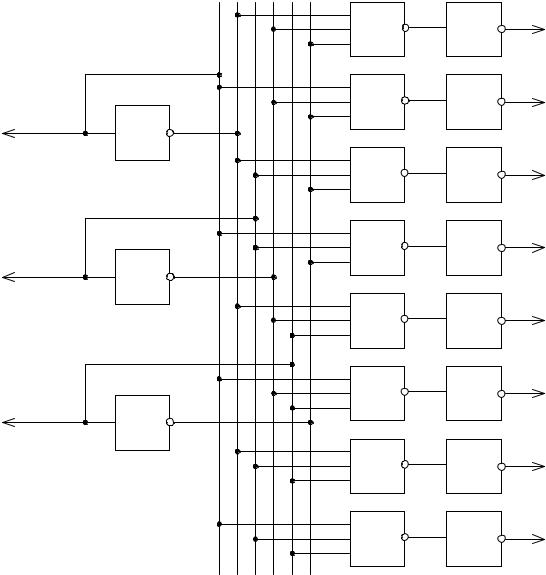

Простейший дешифратор, выполненный на элементах И–НЕ, НЕ (рис. 3.5), называется линейным. Когда на входы подается комбинация 000, с выхода элемента DD1.4 должен быть снят сигнал 1, а с остальных выходов – сигналы 0. Для этого на элемент 3И–НЕ DD3.1 сигналы поступают не непосредственно со входов, а через инверторы DD1.1…DD1.3, в которых нули преобразуются в единицы.

Три сигнала “1” на входе DD3.1 дают на его выходе сигнал 0, который инвертируется элементом DD1.4, и в результате получаем сигнал на выходе

73

DD1.4, равный “1”. На выходах всех остальных элементов будут нули, так как на один из входов элементов DD3.2…DD5.2 подаются сигналы 0, минуя инверторы. Порядок формирования сигналов на выходе при других сигналах на входе приведен в табл. 3.3.

Таблица 3.3

Состояние дешифратора кода 4–2–1 в десятичный код

|

Входы |

|

|

|

|

Выходы |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

21 |

|

22 |

DD1.4 |

DD1.5 |

DD1.6 |

DD2.1 |

DD2.2 |

DD2.3 |

DD2.4 |

DD2.5 |

0 |

|

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

В интегральном исполнении разработана большая гамма двоично– десятичных дешифраторов, допускающих параллельное соединение. Рассмотрим параллельную работу двоично–десятичных дешифраторов на базе микросхемы ИД7.

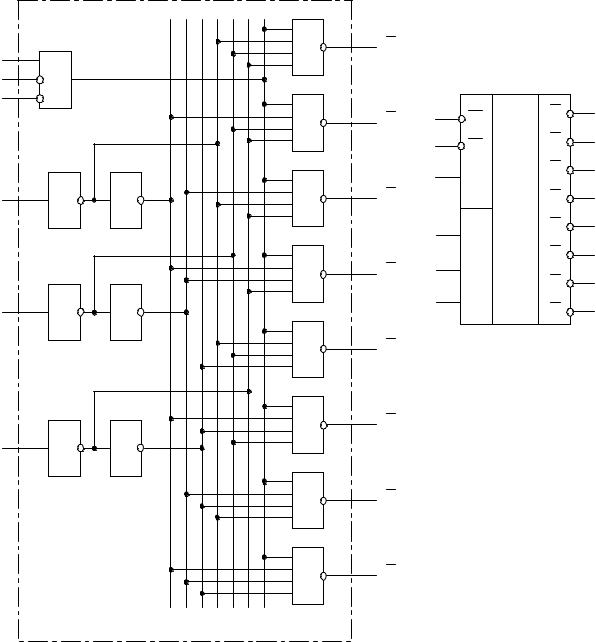

Логическая структура, цоколевка и условное обозначение дешифратора представлены на рис. 3.6.

Дешифрация происходит тогда, когда на входах E1 и E2 действует напряжение низкого уровня, а на входе Е3 – высокого. При других сочетаниях уровней на входах разрешения Еi на всех выходах будет напряжение высокого уровня.

74

Вход |

1 |

2 0 |

DD1.1 |

Вход |

1 |

2 1 |

DD1.2 |

Вход |

1 |

2 2 |

DD1.3 |

& |

1 |

DD3.1 |

DD1.4 |

& |

1 |

DD3.2 |

DD1.5 |

& |

1 |

DD3.3 |

DD1.6 |

& |

1 |

DD4.1 |

DD2.1 |

& |

1 |

DD4.2 |

DD2.2 |

& |

1 |

DD4.3 |

DD2.3 |

& |

1 |

DD5.1 |

DD2.4 |

& |

1 |

DD5.2 |

DD2.5 |

Вых. 0

Вых. 1

Вых. 2

Вых. 3

Вых. 4

Вых. 5

Вых. 6

Вых. 7

Рис. 3.5. Функциональная схема дешифратора двоичного кода в десятичный код

75

|

6 |

|

|

& |

15 |

0 |

|

|

|

|

|

E3 |

& |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

E2 |

5 |

|

|

|

|

|

|

|

|

|

|

E1 |

4 |

|

|

& |

14 |

1 |

4 |

E1 |

DC |

0 |

15 |

|

|

|

|

|

14 |

||||||

|

|

|

|

|

|

|

5 |

E2 |

|

1 |

|

A01 |

1 |

1 |

& |

13 |

|

6 |

E3 |

|

2 |

13 |

|

2 |

|

|

3 |

12 |

|||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

1 |

A0 |

|

4 |

11 |

|

|

|

|

& |

12 |

3 |

2 |

A1 |

|

5 |

10 |

|

|

|

|

|

|

6 |

9 |

||||

|

2 |

1 |

1 |

|

|

|

3 |

A2 |

|

7 |

|

A1 |

|

|

|

|

7 |

||||||

|

|

|

& |

|

|

|

|

|

|

||

|

|

|

|

11 |

4 |

|

16 - питание |

|

|||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

8 - общий |

|

||

|

|

1 |

1 |

& |

10 |

5 |

|

|

|

|

|

A23 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

& |

9 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

& |

7 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рис. 3.6. Структура, условное обозначение и цоколевка микросхемы ИД7 |

|||||||||||

Состояния ИД7 приведены в табл. 3.4.

76

Таблица 3.4

Состояния дешифратора ИД7

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

E3 |

A0 |

A1 |

A2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E1 |

|

E2 |

|

|

0 |

|

|

1 |

|

2 |

|

|

3 |

|

|

4 |

|

|

5 |

|

|

6 |

|

7 |

||||||||

|

1 |

|

|

x |

x |

x |

x |

x |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|||||||||||||||||

|

x |

|

1 |

|

x |

x |

x |

x |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|||||||||||||||||

|

x |

|

x |

0 |

x |

x |

x |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||||||||||||||||||

|

0 |

|

|

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

||||||||||||||||

|

0 |

|

|

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

||||||||||||||||

Наличие трехвходового логического элемента разрешения позволяет соединить параллельно несколько дешифраторов с целью увеличения количества выходов.

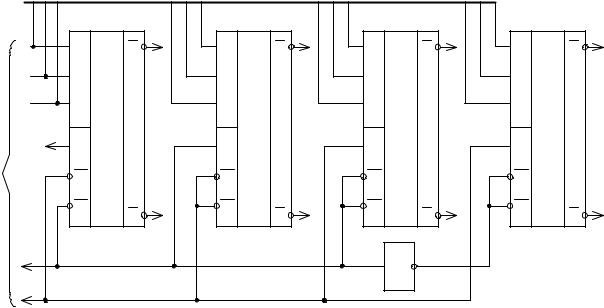

На рис. 3.7 показан дешифратор на 32 выхода. Для его реализации потребовалось 4 дешифратора ИД7 и дополнительный инвертор DD5.

|

1 2 3 |

|

|

3 2 1 |

|

3 2 1 |

|

3 2 1 |

|

|

1 |

A0 DC |

0 |

A0 DC |

8 |

A0 DC 16 |

A0 DC |

24 |

|

|

2 |

A1 |

|

A1 |

|

A1 |

|

A1 |

|

|

4 |

A2 |

|

A2 |

|

A2 |

|

A2 |

|

В |

"1" |

E3 DD1 |

|

E3 DD2 |

|

E3 DD3 |

|

E3 DD4 |

|

х |

|

E2 |

|

E2 |

|

E2 |

|

E2 |

|

о |

|

|

|

|

|

||||

д |

|

E1 |

7 |

E1 |

15 |

E1 |

23 |

E1 |

31 |

|

|

||||||||

|

|

|

|

|

|

||||

|

8 |

|

|

|

|

1 |

DD5 |

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.7. Параллельное соединение ИД7 |

|

|

|||

77