- •Министерство образования и науки, молодёжи и спорта украины

- •Одесский национальный политехнический университет

- •Институт компьютерных систем

- •Кафедра информационных систем

- •Министерство образования и науки, молодёжи и спорта украины

- •Одесский национальный политехнический университет

- •Институт компьютерных систем

- •Кафедра информационных систем

- •Содержание

- •Тема1. Формы представления информации 10

- •Тема 2. Логические основы построения элементов 16

- •Тема 3. Схемотехника комбинационных узлов 29

- •Тема 4. Схемотехника цифровых элементов 70

- •Тема 5. Схемотехника цифровых узлов 108

- •Тема 6. Интегрированные системы элементов 138

- •Тема 7. Схемотехника аналоговых узлов 179

- •Тема 8. Схемотехника обслуживающих элементов 208

- •Тема 14. Структуры микропроцессорных систем 293

- •Тема 15. Схемы поддержки мп на системных платах 340

- •Тема 16. Некоторые вопросы развития архитектуры эвм 357

- •Тема 17. Risk – процессоры 387

- •Тема 18. Суперкомпьютеры. Параллельные вычислительные системы 399

- •Список литературы 450 Тема1. Формы представления информации Лекция 1. Основные понятия

- •Тема 2. Логические основы построения элементов Лекция 2.

- •2.1. Основные понятия, определения и законы Булевой алгебры

- •Формы задания Булевой функции

- •2.2. Простейшие модели логических элементов и система их параметров

- •2.3. Типы выходных каскадов цифровых элементов

- •2.4. Системы (серии) логических элементов и их основные характеристики

- •2.5 Контрольные вопросы

- •Тема 3. Схемотехника комбинационных узлов Лекция 3

- •3.1 Общие сведения

- •3.2. Шифраторы, дешифраторы и преобразователи кодов: назначения, виды, функционирование, принципы построения

- •3.3. Синтез кс на основе дешифраторов

- •3.4. Мультиплексоры и демультиплексоры

- •3.5. Шинные формирователи

- •3.6 Синтез кс на основе мультиплексоров

- •3.7. Компараторы

- •3.8 Сумматоры

- •3.9. Арифметико-логические устройства

- •3.10. Матричные умножители

- •3.11 Постановка и методы решения задач синтеза комбинационных узлов

- •3.11.1 Синтез комбинационных узлов

- •3.11.2 Основные факторы, которые должны быть учтены при построении принципиальных схем

- •3.11.2.1 Питающие напряжения ис

- •3.11.2.2 Уровни логических сигналов

- •3.11.2.3 Нагрузочная способность

- •3.11.2.4 Коэффициент объединения по входу

- •3.11.2.5 Быстродействие

- •3.11.2.6 Помехоустойчивость

- •3.11.2.7 Рассеиваемая мощность

- •3.11.2.8. Использование элементов, имеющих выходы с третьим состоянием или с открытым коллектором

- •3.12 Критерии оценки качества технической реализации кс

- •3.13 Контрольные вопросы

- •Тема 4. Схемотехника цифровых элементов Лекция 4

- •4.1 Последовательностные цифровые схемы

- •4.2. Схемотехника триггерных устройств

- •4.3. Асинхронные триггеры

- •4.4. Синхронные триггеры

- •Rs триггер с синхронизацией по уровню

- •Синхронный rs триггер с синхронизацией по фронту

- •4.5 Методы построения триггеров одного типа на базе триггеров другого типа

- •Проектирование триггеров на основе rs-триггера

- •Метод преобразования характеристических уравнений

- •Метод сравнения характеристических уравнений

- •Использование jk-триггера

- •4.6 Регистры и регистровые файлы

- •4.6.1 Регистры памяти

- •4.6.2 Сдвигающие регистры

- •4.6.3 Универсальные регистры

- •4.7 Счётчики

- •4.7.1 Счетчики с непосредственными связями и последовательным переносом

- •4.7.2 Счетчики с параллельным переносом

- •4.7.3 Реверсивный счетчик с последовательным переносом

- •4.7.4 Двоично-кодированные счётчики с произвольным модулем

- •Построение счетчика методом модификации межразрядных связей

- •Построение счетчика методом управления сбросом

- •4.8 Распределители тактов

- •4.8.1 Распределители импульсов и распределители уровней

- •4.8.2 Кольцевой регистр сдвига

- •4.8.3 Счётчик Джонсона

- •4.9 Контрольные вопросы

- •Тема 5. Схемотехника цифровых узлов Лекция 5

- •5.1 Цифровые автоматы и их разновидности

- •5.2 Абстрактный и структурный автоматы

- •5.3. Способы описания и задания автоматов

- •5.4. Связь между моделями Мура и Мили

- •5.5. Минимизация числа внутренних состояний полностью определенных автоматов

- •5.6. Принцип микропрограммного управления. Понятия об операционном и управляющем автоматах

- •Операционные элементы

- •5.7. Граф - схемы алгоритмов (гса) и их разновидности. Способы задания гса, требования к ним

- •5.8. Абстрактный синтез микропрограммных управляющих автоматов Мили и Мура

- •5.8.1. Синтез автомата Мили

- •5.8.2. Синтез автомата Мура

- •5.9. Структурный синтез микропрограммных управляющих автоматов Мили и Мура

- •5.9.1. Структурный синтез автомата Мили

- •5.9.2. Структурный синтез автомата Мура

- •5.10. Синтез автомата Мура на базе регистра сдвига

- •5.11. Контрольные вопросы

- •Тема 6. Интегрированные системы элементов Лекция 6. Программируемые логические устройства

- •6.1 Основные физические принципы программирования плм и плис

- •6.1.1 Метод плавких перемычек

- •6.1.2 Метод наращиваемых перемычек

- •6.1.3 Устройства, программируемые фотошаблоном

- •6.1.4 Стираемые программируемые постоянные запоминающие устройства

- •6.1.5. Электрически стираемые программируемые постоянные запоминающие устройства

- •6.1.6. Flash - технология

- •6.1.7. Статическое оперативное запоминающее устройство

- •6.1.8. Сравнительная таблица технологий программирования

- •6.2 Простые и сложные плу

- •6.2.1 Ппзу

- •6.2.2 Программируемые логические матрицы

- •6.2.3. Программируемые матрицы pal и gal

- •6.2.4 Дополнительные программируемые опции

- •6.2.5 Сложные плу

- •6.3. Контрольные вопросы

- •Лекция 7. Программируемые логические интегральные схемы

- •7.1 Мелко-, средне- и крупномодульные архитектуры

- •7.2 Логические блоки на мультиплексорах и таблицах соответствия

- •7.3 Таблицы соответствия, распределённое озу, сдвиговые регистры

- •7.4 Конфигурируемые логические блоки, блоки логических символов, секции

- •7.5 Секции и логические ячейки

- •7.6 Конфигурируемые логические блоки clb и блоки логических массивов lab

- •7.7. Контрольные вопросы

- •Лекция 8

- •8.1 Дополнительные встроенные функции

- •8.1.1 Схемы ускоренного переноса

- •8.1.2 Встроенные блоки озу

- •8.1.3 Встроенные умножители, сумматоры и блоки умножения с накоплением

- •8.1.4 Аппаратные и программные встроенные микропроцессорные ядра

- •8.2 Дерево синхронизации и диспетчеры синхронизации

- •8.2.1 Дерево синхронизации

- •8.2.2 Диспетчер синхронизации

- •8.3. Системы с перестраиваемой архитектурой

- •8.4. Программируемый пользователем массив узлов

- •8.4.1. Технология picoArray компании picoChip

- •8.4.2 Технология адаптивных вычислительных машин компании QuickSilver

- •8.5. Контрольные вопросы

- •Тема 7. Схемотехника аналоговых узлов Лекция 9. Операционные усилители

- •9.1. Идеальный операционный усилитель

- •9.2. Основные схемы включения операционного усилителя

- •9.2.1. Дифференциальное включение

- •9.2.2. Инвертирующее включение

- •9.2.3 Неинвертирующее включение

- •9.3 Функциональные устройства на операционных усилителях

- •9.3.1 Схема масштабирования

- •9.3.2 Схема суммирования

- •9.3.3 Схема интегрирования

- •9.3.4 Схема дифференцирования

- •9.3.5 Источники напряжения, управляемые током

- •9.3.6 Источники тока, управляемые напряжением

- •9.4 Активные электрические фильтры на оу

- •9.5 Схемы нелинейного преобразования на оу

- •9.6 Генераторы сигналов на оу

- •9.7. Контрольные вопросы

- •Лекция 10

- •10.1. Изолирующие усилители

- •10.2. Аналоговые компараторы

- •10.3. Источники опорного напряжения

- •10.4. Аналоговые коммутаторы

- •10.5. Оптореле

- •10.6. Устройства выборки-хранения

- •10.7. Цифроаналоговые преобразователи

- •10.8. Аналого-цифровые преобразователи

- •10.9. Контрольные вопросы

- •Тема 8. Схемотехника обслуживающих элементов Лекция 11

- •11.1 Сопряжение цифровых микросхем, изготовленных по разным технологиям, и сопряжение с интерфейсами

- •11.2 Управление входами ттл и кмоп

- •11.3 Дискретное управление нагрузкой от элементов ттл и кмоп

- •11.4 Передача цифровых сигналов на небольшие расстояния

- •11.5 Контрольные вопросы

- •Тема 9. Источники питания. Схемотехника комбинаторных узлов Лекция 12

- •12.1. Схемотехника линейных стабилизаторов напряжения

- •12.2 Импульсные стабилизаторы напряжения

- •12.3 Инверторные схемы

- •12.4 Контрольные вопросы

- •Тема10. Цифровые компьютеры Лекция 13

- •13.1. Принципы действия цифровых компьютеров

- •13.2. Понятие о системе программного (математического) обеспечения эвм

- •13.3. Большие эвм общего назначения

- •13.3.1. Каналы

- •13.3.2. Интерфейс

- •13.4. Малые эвм

- •13.5. Контрольные вопросы

- •Тема 11. Запоминающие устройства Лекция 14

- •14.1 Структура памяти эвм

- •14.2 Способы организации памяти

- •14.2.1 Адресная память

- •14.2.2 Ассоциативная память

- •14.2.3 Стековая память (магазинная)

- •14.3. Структуры адресных зу

- •14.3.1. Зу типа 2d

- •14.3.2. Зу типа 3d

- •14.3.3. Зу типа 2d-m

- •14.4 Постоянные зу (пзу, ппзу)

- •14.5. Флэш-память

- •14.6. Контрольные вопросы

- •Тема 12. Процессоры Лекция 15

- •15.1 Операционные устройства (алу)

- •15.2 Управляющие устройства

- •15.2.1. Уу с жёсткой логикой

- •15.2.2 Уу с хранимой в памяти логикой

- •15.2.2.1. Выборка и выполнение мк

- •15.2.2.2. Кодирование мк

- •15.2.2.3. Синхронизация мк

- •15.3. Контрольные вопросы

- •Тема 13. Универсальные микропроцессоры Лекция 16. Архитектура процессора кр580вм80

- •16.1. Регистры данных

- •16.2. Арифметико-логическое устройство

- •16.3. Регистр признаков

- •16.4. Блок управления

- •16.5. Буферы

- •16.6. Мп с точки зрения программиста

- •16.7. Форматы данных в кр580вм80

- •16.8. Форматы команд в кр580вм80

- •16.9. Способы адресации

- •16.10. Контрольные вопросы

- •Лекция 17. Система команд кр580вм80

- •17.1. Пересылки однобайтовые

- •17.2. Пересылки двухбайтовые

- •17.3. Операции в аккумуляторе

- •17.4. Операции в рон и памяти

- •17.5. Команды управления

- •17.6. Контрольные вопросы

- •Тема 14. Структуры микропроцессорных систем Лекция 18. Общие принципы

- •18.1. Системный интерфейс микро-эвм. Цикл шины

- •18.2. Промежуточный интерфейс

- •18.3. Принципы организации ввода/вывода информации в микропроцессорную систему

- •18.4. Контрольные вопросы

- •Лекция 19. Принципы организации систем прерывания программ

- •19.1. Характеристики систем прерывания

- •19.2. Возможные структуры систем прерывания

- •19.3. Организация перехода к прерывающей программе

- •19.3.1. Реализация фиксированных приоритетов

- •19.3.2. Реализация программно-управляемых приоритетов

- •19.4. Контрольные вопросы

- •Лекция 20. Принципы организации систем прямого доступа в память

- •20.1. Способы организации доступа к системной магистрали

- •20.2. Возможные структуры систем пдп

- •20.3. Организация обмена в режиме пдп

- •20.3.1. Инициализация средств пдп

- •20.3.2. Радиальная структура ( Slave dma)

- •20.3.3. Радиальная структура (Bus master dma)

- •20.3.4. Цепочечная структура ( Bus master dma)

- •20.3.5. Принципы организации арбитража магистрали

- •20.4. Микропроцессорная система на основе мп кр580вм80а

- •20.5. Контрольные вопросы

- •Тема 15. Схемы поддержки мп на системных платах Лекция 21

- •21.1. Эволюция шинной архитектуры ibm pc

- •21.1.1. Локальная системная шина

- •21.1.2. Шина расширения

- •21.1.2.1. Шина расширения isa

- •21.1.2.2. Шина расширения mca

- •21.1.2.3. Шина расширения eisa

- •21.1.3. Локальные шины расширения

- •21.1.3.1. Локальная шина vesa (vlb)

- •21.1.3.2. Локальная шина pci

- •21.2. Современные схемы поддержки мп на системных платах

- •21.2.1. Чипсет GeForce 9300/9400 фирмы nvidia

- •21.2.3. Чипсет Intel z68 для платформы Socket 1155

- •21.3. Контрольные вопросы

- •Тема 16. Некоторые вопросы развития архитектуры эвм Лекция 22

- •22.1. Теги и дескрипторы. Самоопределяемые данные

- •22.2. Методы оптимизации обмена процессор-память

- •22.2.1. Конвейер команд

- •22.2.2. Расслоение памяти

- •22.2.3. Буферизация памяти

- •22.3. Динамическое распределение памяти. Виртуальная память

- •22.3.1. Виртуальная память

- •22.3.2. Сегментно-страничная организация памяти

- •22.4. Контрольные вопросы

- •Лекция 23. Защита памяти

- •23.1. Защита отдельных ячеек памяти

- •23.2. Метод граничных регистров

- •23.3. Метод ключей защиты

- •23.4. Алгоритмы управления многоуровневой памятью

- •23.5. Контрольные вопросы

- •Тема 17. Risk – процессоры Лекция 24

- •24.1. Общая характеристика risk - процессоров

- •24.2. Arm архитектура

- •24.2.1. Дополнительные технологии

- •24.2.2. Ядро arm7tdmi

- •24.2.3. Семейство arm10 Tumb

- •24.3. Контрольные вопросы

- •Тема 18. Суперкомпьютеры. Параллельные вычислительные системы Лекция 25

- •25.1. Смена приоритетов в области высокопроизводительных вычислений

- •25.2. Сферы применения многоядерных процессоров и многопроцессорных вычислительных систем

- •25.3. Классификация архитектур вычислительных систем по степени параллелизма обработки данных

- •25.4. Архитектуры smp, mpp и numa

- •25.5. Организация когерентности многоуровневой иерархической памяти

- •25.6. Pvp архитектура

- •25.7. Контрольные вопросы

- •Лекция 26. Кластерная архитектура

- •26.1. Архитектура связи в кластерных системах

- •26.2. Коммутаторы для многопроцессорных вычислительных систем.

- •26.2.1. Простые коммутаторы

- •26.2.2. Составные коммутаторы

- •26.2.2.1. Коммутатор Клоза

- •26.3. Контрольные вопросы

- •Лекция 27. Высокопроизводительные многоядерные процессоры для встраиваемых приложений

- •27.1. Процессоры Tile-64/64Pro компании Tilera

- •27.4. Мультипроцессор Cell

- •27.4.1. Общая структура процессора Cell

- •27.4.2. Структура процессорного элемента Power (ppe)

- •27.4.3. Структура spe — "синергичного" процессорного элемента

- •27.5. Альтернативная технология построения многоядерных систем на кристалле — atac

- •27.5.1. Основные идеи архитектуры atac

- •27.5.2. Ключевые элементы технологии атас

- •27.5.3. Структура межъядерных связей

- •27.5.4. Передача данных и согласование кэш-памяти

- •27.6. Контрольные вопросы

- •Список литературы

26.2.2. Составные коммутаторы

Простые коммутаторы имеют ограничения на число входов и выходов, а также могут требовать большого количества оборудования при увеличении этого числа (в случае пространственных коммутаторов). Поэтому для построения коммутаторов с большим количеством входов и выходов используют совокупность простых коммутаторов, объединенных с помощью линий "точка-точка".

Составные коммутаторы имеют задержку, пропорциональную количеству простых коммутаторов, через которые проходит сигнал от входа до выхода, т.е. числу каскадов. Однако объем оборудования составного коммутатора меньше, чем простого с тем же количеством входов и выходов.

Чаще всего составные коммутаторы строятся из прямоугольных коммутаторов 2 х 2 с двумя входами и выходами. Они имеют два состояния: прямое пропускание входов на соответствующие выходы и перекрестное пропускание. Коммутатор 2 х 2 состоит из собственно блока коммутации данных и блока управления. Блок управления в зависимости от поступающих на него управляющих сигналов определяет, какой тип соединения следует осуществить в блоке коммутации - прямой или перекрестный. При этом если оба входа хотят соединиться с одним выходом, то коммутатор разрешает конфликт и связывает с данным выходом только один вход, а запрос на соединение со стороны второго блокируется или отвергается.

26.2.2.1. Коммутатор Клоза

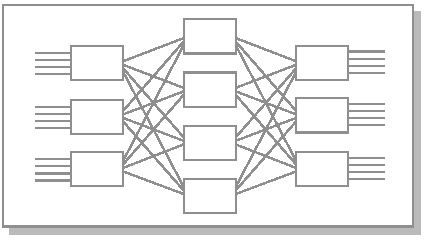

Коммутатор Клоза может быть построен в качестве альтернативы для прямоугольного коммутатора с (m x d) входами и (m x d) выходами. Он формируется из трех каскадов коммутаторов: m коммутаторов (d x d) во входном каскаде, m коммутаторов (d x d) в выходном и d промежуточных коммутаторов (m x m) (рис.26.9).

Рис.26.9. Коммутатор Клоза 3х4

Соединения внутри коммутатора устроены следующим образом:

j-й выход i-ого коммутатора входного каскада соединен с i-ым входом j-ого промежуточного коммутатора;

j-й вход k-ого коммутатора выходного каскада соединен с k-ым выходом j-ого промежуточного коммутатора.

Данный тип составных коммутаторов позволяет соединять любой вход с любым выходом, однако при установленных соединениях добавление нового соединения может потребовать разрыва и переустановления всех соединений.

Баньян-сети.

Коммутаторы этого типа строятся на базе прямоугольных коммутаторов таким образом, что существует только один путь от каждого входа к каждому выходу.

Наиболее важной разновидностью баньян-сетей является дельта-сеть. Она формируется из прямоугольных коммутаторов (a x b) и представляет собой n-каскадный коммутатор с an входами и bn выходами. Составляющие коммутаторы соединены так, что для соединения любого входа и выхода образуется единственный путь одинаковой для всех пар входов и выходов длины.

Распределенные составные коммутаторы

В распределенных вычислительных системах ресурсы разделяются между задачами, каждая из которых исполняется на своем подмножестве процессоров. В связи с этим возникает понятие близости процессоров, которая является важной для активно взаимодействующих процессоров. Обычно близость процессоров выражается в различной каскадности соединений, различных расстояниях между ними.

Один из вариантов создания составных коммутаторов заключается в объединении прямоугольных коммутаторов (v+1 x v+1), v > 1 таким образом, что один вход и один выход каждого составляющего коммутатора служат входом и выходом составного коммутатора. К каждому внутреннему коммутатору подсоединяются процессор и память, образуя вычислительный модуль с v-каналами для соединения с другими вычислительными модулями. Свободные v-входов и v-выходов каждого вычислительного модуля соединяются линиями "точка-точка" с входами и выходами других коммутаторов, образуя граф межмодульных связей.

Наиболее эффективным графом межмодульных связей с точки зрения организации обмена данными между вычислительными модулями является полный граф. В этом случае между каждой парой вычислительных модулей существует прямое соединение. При этом возможны одновременные соединения между произвольными вычислительными модулями.

Однако обычно создать полный граф межмодульных связей невозможно по ряду причин. Обмен данными приходится производить через цепочки транзитных модулей. Из-за этого увеличиваются задержки, и ограничивается возможность установления одновременных соединений. Таким образом, эффективный граф межмодульных связей должен минимизировать время межмодульных обменов и максимально увеличить количество одновременно активизированных соединений. Кроме того, на выбор графа межмодульных связей влияет учет отказов и восстановлений вычислительных модулей и линий связи.

Граф межмодульных связей Convex Exemplar SPP1000

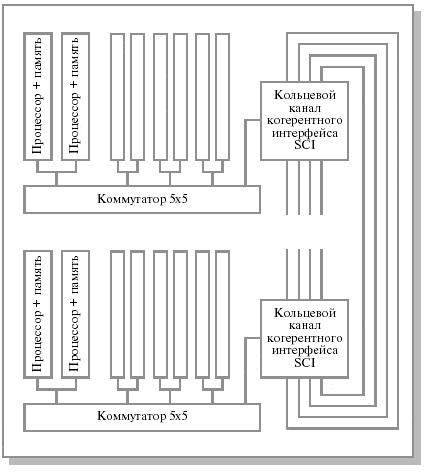

В качестве примера реального графа межмодульных связей рассмотрим структуру системы Convex Exemplar SPP1000. В основе каждого составного блока системы лежит прямоугольный коммутатор (5 х 5), до 16 подобных блоков объединяются каналами "точка-точка" в кольцо (одномерный тор), состоящее из четырех независимых подканалов (рис.26.10).

Рис.26.10. Граф межмодульных связей Convex Exemplar SPP1000

Внутри каждого блока четыре входа и выхода прямоугольного коммутатора (5 х 5) используются для взаимодействия устройств внутри блока (при этом в каждом блоке располагается по два процессора), пятые вход и выход используются для объединения блоков в кольцо. При этом каждый из четырех кольцевых каналов рассматривается как независимый ресурс, и система сохраняет работоспособность до тех пор, пока существует хотя бы один функционирующий кольцевой канал.

Граф межмодульных связей МВС-100

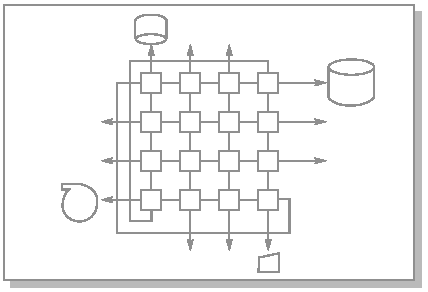

Система МВС-100 предлагает блочный подход к построению архитектуры параллельной вычислительной системы. Структурный модуль системы состоит из 16 вычислительных узлов, образующих матрицу 4х4 (рис.26.11). Угловые узлы соединяются попарно по диагонали, таким образом, максимальная длина пути между любой парой элементов равна трем. В исходной же матрице 4 х 4 эта длина равна шести. Каждый блок имеет 12 выходов, что позволяет объединять их в более сложные структуры.

Рис.26.11. Структурный модуль МВС-100

Для МВС-100 базовый вычислительный блок содержит 32 узла. Такой блок строится из двух структурных модулей в соответствии со схемой, приведенной на рис.26.12. В этом случае максимальная длина пути между любой парой вычислительных узлов равна пяти. При этом остается 16 свободных связей, что позволяет продолжить объединение. При объединении двух базовых блоков по схеме, приведенной на рис.26.12 (64 вычислительных узла) максимальная длина пути составит 6, как и в гиперкубе, а количество свободных связей будет равно 16.

Рис.26.12. Варианты объединения структурных модулей МВС-100

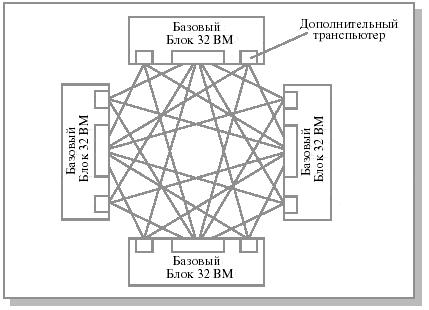

Граф межмодульных связей МВС-1000

Архитектура системы МВС-1000 аналогична архитектуре МВС-100. Основой системы является масштабируемый массив процессорных узлов. Каждый узел содержит вычислительный микропроцессор Alpha 21164 с производительностью 2 GFLOPS при тактовой частоте 500 MHz и оперативную память объемом 128 MB, с возможностью расширения. Процессорные узлы взаимодействуют через коммуникационные процессоры TMS320C44 производства Texas Instruments, имеющие по 4 внешних канала (линка) с общей пропускной способностью 80 Мбайт/с (20 Мбайт/с каждый). Также разрабатывается вариант системы с использованием коммуникационных процессоров SHARC (ADSP 21060) компании Analog Devices, имеющих по 6 каналов с общей пропускной способностью до 240 Мбайт/с (40 Мбайт/с каждый).

Процессорные узлы связаны между собой по оригинальной схеме, сходной с топологией двухмерного тора (для 4-линковых узлов). Аналогично МВС-100, структурный модуль МВС-1000 состоит из 16 вычислительных модулей, образующих матрицу 4 x 4, в которой четыре угловых элемента соединяются через транспьютерные линки по диагонали попарно. Оставшиеся 12 линков предназначаются для подсоединения внешних устройств (4 линка угловых ВМ) и соединений с подобными ВМ.

Конструктивным образованием МВС-1000 является базовый вычислительный блок, содержащий 32 вычислительных модуля. Максимальная длина пути между любыми из 32 вычислительных модулей равна пяти, при этом число свободных линков после комплектации блока составляет 16, что позволяет продолжить процедуру объединения. Возможная схема объединения четырех базовых блоков в 128-процессорную систему приведена на рис.26.13.

Рис.26.13. Структура 128-процессорной системы МВС-1000, 4 базовых блока