- •Министерство образования и науки, молодёжи и спорта украины

- •Одесский национальный политехнический университет

- •Институт компьютерных систем

- •Кафедра информационных систем

- •Министерство образования и науки, молодёжи и спорта украины

- •Одесский национальный политехнический университет

- •Институт компьютерных систем

- •Кафедра информационных систем

- •Содержание

- •Тема1. Формы представления информации 10

- •Тема 2. Логические основы построения элементов 16

- •Тема 3. Схемотехника комбинационных узлов 29

- •Тема 4. Схемотехника цифровых элементов 70

- •Тема 5. Схемотехника цифровых узлов 108

- •Тема 6. Интегрированные системы элементов 138

- •Тема 7. Схемотехника аналоговых узлов 179

- •Тема 8. Схемотехника обслуживающих элементов 208

- •Тема 14. Структуры микропроцессорных систем 293

- •Тема 15. Схемы поддержки мп на системных платах 340

- •Тема 16. Некоторые вопросы развития архитектуры эвм 357

- •Тема 17. Risk – процессоры 387

- •Тема 18. Суперкомпьютеры. Параллельные вычислительные системы 399

- •Список литературы 450 Тема1. Формы представления информации Лекция 1. Основные понятия

- •Тема 2. Логические основы построения элементов Лекция 2.

- •2.1. Основные понятия, определения и законы Булевой алгебры

- •Формы задания Булевой функции

- •2.2. Простейшие модели логических элементов и система их параметров

- •2.3. Типы выходных каскадов цифровых элементов

- •2.4. Системы (серии) логических элементов и их основные характеристики

- •2.5 Контрольные вопросы

- •Тема 3. Схемотехника комбинационных узлов Лекция 3

- •3.1 Общие сведения

- •3.2. Шифраторы, дешифраторы и преобразователи кодов: назначения, виды, функционирование, принципы построения

- •3.3. Синтез кс на основе дешифраторов

- •3.4. Мультиплексоры и демультиплексоры

- •3.5. Шинные формирователи

- •3.6 Синтез кс на основе мультиплексоров

- •3.7. Компараторы

- •3.8 Сумматоры

- •3.9. Арифметико-логические устройства

- •3.10. Матричные умножители

- •3.11 Постановка и методы решения задач синтеза комбинационных узлов

- •3.11.1 Синтез комбинационных узлов

- •3.11.2 Основные факторы, которые должны быть учтены при построении принципиальных схем

- •3.11.2.1 Питающие напряжения ис

- •3.11.2.2 Уровни логических сигналов

- •3.11.2.3 Нагрузочная способность

- •3.11.2.4 Коэффициент объединения по входу

- •3.11.2.5 Быстродействие

- •3.11.2.6 Помехоустойчивость

- •3.11.2.7 Рассеиваемая мощность

- •3.11.2.8. Использование элементов, имеющих выходы с третьим состоянием или с открытым коллектором

- •3.12 Критерии оценки качества технической реализации кс

- •3.13 Контрольные вопросы

- •Тема 4. Схемотехника цифровых элементов Лекция 4

- •4.1 Последовательностные цифровые схемы

- •4.2. Схемотехника триггерных устройств

- •4.3. Асинхронные триггеры

- •4.4. Синхронные триггеры

- •Rs триггер с синхронизацией по уровню

- •Синхронный rs триггер с синхронизацией по фронту

- •4.5 Методы построения триггеров одного типа на базе триггеров другого типа

- •Проектирование триггеров на основе rs-триггера

- •Метод преобразования характеристических уравнений

- •Метод сравнения характеристических уравнений

- •Использование jk-триггера

- •4.6 Регистры и регистровые файлы

- •4.6.1 Регистры памяти

- •4.6.2 Сдвигающие регистры

- •4.6.3 Универсальные регистры

- •4.7 Счётчики

- •4.7.1 Счетчики с непосредственными связями и последовательным переносом

- •4.7.2 Счетчики с параллельным переносом

- •4.7.3 Реверсивный счетчик с последовательным переносом

- •4.7.4 Двоично-кодированные счётчики с произвольным модулем

- •Построение счетчика методом модификации межразрядных связей

- •Построение счетчика методом управления сбросом

- •4.8 Распределители тактов

- •4.8.1 Распределители импульсов и распределители уровней

- •4.8.2 Кольцевой регистр сдвига

- •4.8.3 Счётчик Джонсона

- •4.9 Контрольные вопросы

- •Тема 5. Схемотехника цифровых узлов Лекция 5

- •5.1 Цифровые автоматы и их разновидности

- •5.2 Абстрактный и структурный автоматы

- •5.3. Способы описания и задания автоматов

- •5.4. Связь между моделями Мура и Мили

- •5.5. Минимизация числа внутренних состояний полностью определенных автоматов

- •5.6. Принцип микропрограммного управления. Понятия об операционном и управляющем автоматах

- •Операционные элементы

- •5.7. Граф - схемы алгоритмов (гса) и их разновидности. Способы задания гса, требования к ним

- •5.8. Абстрактный синтез микропрограммных управляющих автоматов Мили и Мура

- •5.8.1. Синтез автомата Мили

- •5.8.2. Синтез автомата Мура

- •5.9. Структурный синтез микропрограммных управляющих автоматов Мили и Мура

- •5.9.1. Структурный синтез автомата Мили

- •5.9.2. Структурный синтез автомата Мура

- •5.10. Синтез автомата Мура на базе регистра сдвига

- •5.11. Контрольные вопросы

- •Тема 6. Интегрированные системы элементов Лекция 6. Программируемые логические устройства

- •6.1 Основные физические принципы программирования плм и плис

- •6.1.1 Метод плавких перемычек

- •6.1.2 Метод наращиваемых перемычек

- •6.1.3 Устройства, программируемые фотошаблоном

- •6.1.4 Стираемые программируемые постоянные запоминающие устройства

- •6.1.5. Электрически стираемые программируемые постоянные запоминающие устройства

- •6.1.6. Flash - технология

- •6.1.7. Статическое оперативное запоминающее устройство

- •6.1.8. Сравнительная таблица технологий программирования

- •6.2 Простые и сложные плу

- •6.2.1 Ппзу

- •6.2.2 Программируемые логические матрицы

- •6.2.3. Программируемые матрицы pal и gal

- •6.2.4 Дополнительные программируемые опции

- •6.2.5 Сложные плу

- •6.3. Контрольные вопросы

- •Лекция 7. Программируемые логические интегральные схемы

- •7.1 Мелко-, средне- и крупномодульные архитектуры

- •7.2 Логические блоки на мультиплексорах и таблицах соответствия

- •7.3 Таблицы соответствия, распределённое озу, сдвиговые регистры

- •7.4 Конфигурируемые логические блоки, блоки логических символов, секции

- •7.5 Секции и логические ячейки

- •7.6 Конфигурируемые логические блоки clb и блоки логических массивов lab

- •7.7. Контрольные вопросы

- •Лекция 8

- •8.1 Дополнительные встроенные функции

- •8.1.1 Схемы ускоренного переноса

- •8.1.2 Встроенные блоки озу

- •8.1.3 Встроенные умножители, сумматоры и блоки умножения с накоплением

- •8.1.4 Аппаратные и программные встроенные микропроцессорные ядра

- •8.2 Дерево синхронизации и диспетчеры синхронизации

- •8.2.1 Дерево синхронизации

- •8.2.2 Диспетчер синхронизации

- •8.3. Системы с перестраиваемой архитектурой

- •8.4. Программируемый пользователем массив узлов

- •8.4.1. Технология picoArray компании picoChip

- •8.4.2 Технология адаптивных вычислительных машин компании QuickSilver

- •8.5. Контрольные вопросы

- •Тема 7. Схемотехника аналоговых узлов Лекция 9. Операционные усилители

- •9.1. Идеальный операционный усилитель

- •9.2. Основные схемы включения операционного усилителя

- •9.2.1. Дифференциальное включение

- •9.2.2. Инвертирующее включение

- •9.2.3 Неинвертирующее включение

- •9.3 Функциональные устройства на операционных усилителях

- •9.3.1 Схема масштабирования

- •9.3.2 Схема суммирования

- •9.3.3 Схема интегрирования

- •9.3.4 Схема дифференцирования

- •9.3.5 Источники напряжения, управляемые током

- •9.3.6 Источники тока, управляемые напряжением

- •9.4 Активные электрические фильтры на оу

- •9.5 Схемы нелинейного преобразования на оу

- •9.6 Генераторы сигналов на оу

- •9.7. Контрольные вопросы

- •Лекция 10

- •10.1. Изолирующие усилители

- •10.2. Аналоговые компараторы

- •10.3. Источники опорного напряжения

- •10.4. Аналоговые коммутаторы

- •10.5. Оптореле

- •10.6. Устройства выборки-хранения

- •10.7. Цифроаналоговые преобразователи

- •10.8. Аналого-цифровые преобразователи

- •10.9. Контрольные вопросы

- •Тема 8. Схемотехника обслуживающих элементов Лекция 11

- •11.1 Сопряжение цифровых микросхем, изготовленных по разным технологиям, и сопряжение с интерфейсами

- •11.2 Управление входами ттл и кмоп

- •11.3 Дискретное управление нагрузкой от элементов ттл и кмоп

- •11.4 Передача цифровых сигналов на небольшие расстояния

- •11.5 Контрольные вопросы

- •Тема 9. Источники питания. Схемотехника комбинаторных узлов Лекция 12

- •12.1. Схемотехника линейных стабилизаторов напряжения

- •12.2 Импульсные стабилизаторы напряжения

- •12.3 Инверторные схемы

- •12.4 Контрольные вопросы

- •Тема10. Цифровые компьютеры Лекция 13

- •13.1. Принципы действия цифровых компьютеров

- •13.2. Понятие о системе программного (математического) обеспечения эвм

- •13.3. Большие эвм общего назначения

- •13.3.1. Каналы

- •13.3.2. Интерфейс

- •13.4. Малые эвм

- •13.5. Контрольные вопросы

- •Тема 11. Запоминающие устройства Лекция 14

- •14.1 Структура памяти эвм

- •14.2 Способы организации памяти

- •14.2.1 Адресная память

- •14.2.2 Ассоциативная память

- •14.2.3 Стековая память (магазинная)

- •14.3. Структуры адресных зу

- •14.3.1. Зу типа 2d

- •14.3.2. Зу типа 3d

- •14.3.3. Зу типа 2d-m

- •14.4 Постоянные зу (пзу, ппзу)

- •14.5. Флэш-память

- •14.6. Контрольные вопросы

- •Тема 12. Процессоры Лекция 15

- •15.1 Операционные устройства (алу)

- •15.2 Управляющие устройства

- •15.2.1. Уу с жёсткой логикой

- •15.2.2 Уу с хранимой в памяти логикой

- •15.2.2.1. Выборка и выполнение мк

- •15.2.2.2. Кодирование мк

- •15.2.2.3. Синхронизация мк

- •15.3. Контрольные вопросы

- •Тема 13. Универсальные микропроцессоры Лекция 16. Архитектура процессора кр580вм80

- •16.1. Регистры данных

- •16.2. Арифметико-логическое устройство

- •16.3. Регистр признаков

- •16.4. Блок управления

- •16.5. Буферы

- •16.6. Мп с точки зрения программиста

- •16.7. Форматы данных в кр580вм80

- •16.8. Форматы команд в кр580вм80

- •16.9. Способы адресации

- •16.10. Контрольные вопросы

- •Лекция 17. Система команд кр580вм80

- •17.1. Пересылки однобайтовые

- •17.2. Пересылки двухбайтовые

- •17.3. Операции в аккумуляторе

- •17.4. Операции в рон и памяти

- •17.5. Команды управления

- •17.6. Контрольные вопросы

- •Тема 14. Структуры микропроцессорных систем Лекция 18. Общие принципы

- •18.1. Системный интерфейс микро-эвм. Цикл шины

- •18.2. Промежуточный интерфейс

- •18.3. Принципы организации ввода/вывода информации в микропроцессорную систему

- •18.4. Контрольные вопросы

- •Лекция 19. Принципы организации систем прерывания программ

- •19.1. Характеристики систем прерывания

- •19.2. Возможные структуры систем прерывания

- •19.3. Организация перехода к прерывающей программе

- •19.3.1. Реализация фиксированных приоритетов

- •19.3.2. Реализация программно-управляемых приоритетов

- •19.4. Контрольные вопросы

- •Лекция 20. Принципы организации систем прямого доступа в память

- •20.1. Способы организации доступа к системной магистрали

- •20.2. Возможные структуры систем пдп

- •20.3. Организация обмена в режиме пдп

- •20.3.1. Инициализация средств пдп

- •20.3.2. Радиальная структура ( Slave dma)

- •20.3.3. Радиальная структура (Bus master dma)

- •20.3.4. Цепочечная структура ( Bus master dma)

- •20.3.5. Принципы организации арбитража магистрали

- •20.4. Микропроцессорная система на основе мп кр580вм80а

- •20.5. Контрольные вопросы

- •Тема 15. Схемы поддержки мп на системных платах Лекция 21

- •21.1. Эволюция шинной архитектуры ibm pc

- •21.1.1. Локальная системная шина

- •21.1.2. Шина расширения

- •21.1.2.1. Шина расширения isa

- •21.1.2.2. Шина расширения mca

- •21.1.2.3. Шина расширения eisa

- •21.1.3. Локальные шины расширения

- •21.1.3.1. Локальная шина vesa (vlb)

- •21.1.3.2. Локальная шина pci

- •21.2. Современные схемы поддержки мп на системных платах

- •21.2.1. Чипсет GeForce 9300/9400 фирмы nvidia

- •21.2.3. Чипсет Intel z68 для платформы Socket 1155

- •21.3. Контрольные вопросы

- •Тема 16. Некоторые вопросы развития архитектуры эвм Лекция 22

- •22.1. Теги и дескрипторы. Самоопределяемые данные

- •22.2. Методы оптимизации обмена процессор-память

- •22.2.1. Конвейер команд

- •22.2.2. Расслоение памяти

- •22.2.3. Буферизация памяти

- •22.3. Динамическое распределение памяти. Виртуальная память

- •22.3.1. Виртуальная память

- •22.3.2. Сегментно-страничная организация памяти

- •22.4. Контрольные вопросы

- •Лекция 23. Защита памяти

- •23.1. Защита отдельных ячеек памяти

- •23.2. Метод граничных регистров

- •23.3. Метод ключей защиты

- •23.4. Алгоритмы управления многоуровневой памятью

- •23.5. Контрольные вопросы

- •Тема 17. Risk – процессоры Лекция 24

- •24.1. Общая характеристика risk - процессоров

- •24.2. Arm архитектура

- •24.2.1. Дополнительные технологии

- •24.2.2. Ядро arm7tdmi

- •24.2.3. Семейство arm10 Tumb

- •24.3. Контрольные вопросы

- •Тема 18. Суперкомпьютеры. Параллельные вычислительные системы Лекция 25

- •25.1. Смена приоритетов в области высокопроизводительных вычислений

- •25.2. Сферы применения многоядерных процессоров и многопроцессорных вычислительных систем

- •25.3. Классификация архитектур вычислительных систем по степени параллелизма обработки данных

- •25.4. Архитектуры smp, mpp и numa

- •25.5. Организация когерентности многоуровневой иерархической памяти

- •25.6. Pvp архитектура

- •25.7. Контрольные вопросы

- •Лекция 26. Кластерная архитектура

- •26.1. Архитектура связи в кластерных системах

- •26.2. Коммутаторы для многопроцессорных вычислительных систем.

- •26.2.1. Простые коммутаторы

- •26.2.2. Составные коммутаторы

- •26.2.2.1. Коммутатор Клоза

- •26.3. Контрольные вопросы

- •Лекция 27. Высокопроизводительные многоядерные процессоры для встраиваемых приложений

- •27.1. Процессоры Tile-64/64Pro компании Tilera

- •27.4. Мультипроцессор Cell

- •27.4.1. Общая структура процессора Cell

- •27.4.2. Структура процессорного элемента Power (ppe)

- •27.4.3. Структура spe — "синергичного" процессорного элемента

- •27.5. Альтернативная технология построения многоядерных систем на кристалле — atac

- •27.5.1. Основные идеи архитектуры atac

- •27.5.2. Ключевые элементы технологии атас

- •27.5.3. Структура межъядерных связей

- •27.5.4. Передача данных и согласование кэш-памяти

- •27.6. Контрольные вопросы

- •Список литературы

23.5. Контрольные вопросы

1. Варианты дифференцированной защиты при различных операциях с памятью.

2. Защита отдельных ячеек памяти.

3. Метод граничных регистров.

4. Метод ключей защиты.

5. Система защиты памяти ЭВМ на процессоре I80386.

6. Алгоритмы управления многоуровневой памятью.

7. Физически реализуемые (эвристические) алгоритмы замещения.

Тема 17. Risk – процессоры Лекция 24

24.1. Общая характеристика risk - процессоров

Развитие архитектуры ЭВМ, направленное на повышение их производительности, в последние десятилетия шло по пути усложнения процессоров путем расширения системы команд, введения сложных команд, выполняющих процедуры, приближающиеся к примитивам языков высокого уровня, увеличения числа используемых способов адресации и т.д.

Однако расширение и усложнение набора команд порождает и ряд нежелательных побочных эффектов. Расширение набора команд, числа способов адресации, введение сложных команд сопровождается увеличением длины команды и, в первую очередь, кода операции, что ведет к увеличению числа форматов команд. Это вызывает усложнение и замедление процесса дешифрации кода операции и других процедур обработки команд в процессоре. Возрастающая сложность процедур обработки команд заставляет использовать микропрограммные управляющие устройства с управляющей памятью (микропрограммные УУ) вместо более быстродействующих УУ с жесткой логикой. Усложнение процессора делает более трудным и даже невыполнимым реализацию его на одном кристалле БИС. А размещение процессора в одном кристалле за счет сокращения длин межсоединений облегчает достижение высокой производительности.

Сказанное выше объясняет, почему в начале 80-х гг. сформировалось альтернативное по отношению к усложнению архитектуры процессоров направление. При создании относительно дешевых высокопроизводительных ЭВМ оно использует архитектуру с сокращенным набором команд (СНК-архитектура), называемую в зарубежной литературе RISC-архитектурой. Ниже рассматриваются только основные принципы, заложенные в основу классической RISC-архитектуры.

RISC-архитектура предполагает реализацию в ЭВМ сокращенного набора простейших, но часто употребляемых команд. Это позволяет упростить аппаратные средства процессора и получить возможность повысить его быстродействие. При использовании RISC-архитектуры выбор набора команд и структуры процессора направлены на то, чтобы команды набора выполнялись за один машинный цикл процессора. Выполнение более сложных, но редко встречаемых операций обеспечивают подпрограммы.

В RISC-ЭВМ машинным циклом называется время, в течение которого производится выборка двух операндов из регистров, выполнение операции в АЛУ и запоминание результатов в регистре. Большинство команд в RISC являются быстрыми командами типа "регистр-регистр" и выполняются без обращения к ОП. Для того, чтобы это было возможно, процессор должен содержать достаточно большое число общих регистров.

Таким образом, ЭВМ RISC-архитектуры имеют ряд характерных особенностей:

сокращенный набор команд (обычно не более 50-100);

небольшое число (обычно 2-3) простых способов адресации;

небольшое число простых форматов команд с фиксированными размерами и функциональным назначением полей.

Все это упрощает УУ процессора и позволяет обходиться без микропрограммного уровня управления и управляющей памяти, т.е. УУ может быть выполнено на быстродействующей жесткой логике.

Рассмотренные выше особенности, присущие ЭВМ RISC-архитектуры, приводят к столь значительному упрощению процессора, что возникает возможность размещения в одном кристалле не только процессора, но и большого количества общих регистров. В современных БИС МП RISC-архитектуры число общих и специализированных регистров достигает десятков и сотен при существенном сокращении общего числа транзисторов процессора. Так, например, для реализации 32-разрядных процессоров RISC-архитектуры, соответствующих производительности процессоров класса I80386, требуется менее 50 000 транзисторов, в то время как для процессоров традиционной архитектуры (CISC) – более 150 000.

Большое число РОН, особенно при наличии обеспечивающего их эффективное использование "оптимизирующего компилятора", позволяет до предела сократить обращение к ОП. Это достигается:

за счет того, что промежуточный результат вычисления сохраняется на регистрах;

передача операндов из одних программ в другие или подпрограммы осуществляется через регистры;

не требуется передачи на сохранение в ОП содержимого регистров при прерываниях.

Одной из характерных особенностей RISC-архитектуры является широкое использование механизма перекрывающихся регистровых окон. Он предназначен для уменьшения числа обращений к ОП и межрегистровых передач, что способствует повышению производительности ЭВМ.

Процедурам динамически выделяются небольшие группы регистров фиксированной длины (регистровые окна). Окна последовательно выполняемых процедур перекрываются, благодаря чему возможна передача параметров от одной процедуры к другой. При вызове процедуры процессор переключается на работу с другим регистровым окном. При этом не возникает необходимость в передаче содержимого регистров в память.

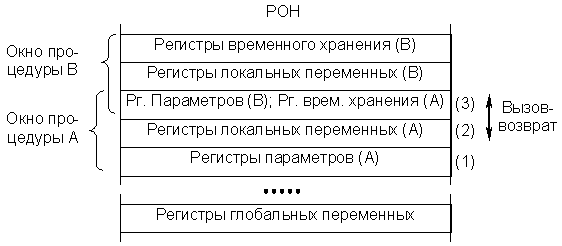

Окно состоит из трёх подгрупп регистров (рис. 24.1).

Рис.24.1. RISK – архитектура ЭВМ. Перекрывающиеся регистровые окна

Полагаем, что вызов процедур идет снизу вверх, т.е. процедура A вызывает процедуру B, причем сама была вызвана некоторой предшествующей процедурой. Первая подгруппа содержит параметры, переданные данной процедуре (A) от ее вызвавшей, и результаты для вызывающей процедуры при возврате в нее. Вторая подгруппа содержит локальные переменные процедуры A. Третья является буфером для двухстороннего обмена между процедурой A и вызываемой ею процедурой B. Процедура A передает B параметры при вызове. При возврате из процедуры B в процедуру A последняя получает через этот буфер результаты работы процедуры B. Таким образом, одна и та же подгруппа для процедуры A является регистрами временного хранения, а для следующей (процедуры B) – регистрами параметров. Отдельное окно, доступное всем процедурам программы, выделяется для ее глобальных переменных.

Следует отметить, что компьютеров, полностью удовлетворяющих определению RISC-архитектуры, относительно немного. В большинстве случаев это компьютеры, близкие к RISC-архитектуре. Например, одним из первых компьютеров такого типа являлся высокопроизводительный РС фирмы IBM PC-RT. Он имел 118 команд, всего два способа адресации и два формата команд, 16 РОН, среднее число циклов на команду – три. К чисто RISC-архитектуре принято относить процессоры серии "Alpha" фирмы DEC, серию процессоров "Power PC" совместной разработки фирм Motorola, EPL, IBM, серию процессоров "Rxxxx" (R4000, R5000, R10000) фирмы Mips, серию процессоров "РА" фирмы Hewlett Packard, серию процессоров "SPARC" фирмы Sun Microsystems и др.

Несмотря на широкое использование в литературе терминов "RISC" и "CISC", архитектуры современных мощных процессоров трудно поддаются однозначной классификации. Это связано со стремительным усложнением кристаллов процессоров обоих типов архитектур (RISC и CISC), а также с тем, что в целях повышения производительности разработчики объединяют конструктивные решения, характерные для обоих типов архитектур, в одном устройстве. Так, в мощных CISC-процессорах стало обычным использование RISC-ядра, которое позволяет выполнять сложные команды процессора как наборы элементарных команд, реализуемых по принципам RISC-архитектуры.

Следует отметить также, что принципы RISC-архитектуры заложены в идеологию построения транспьютеров, составляющих основу современных матричных процессоров, используемых в суперЭВМ, а также в платах-"ускорителях" для персональных компьютеров.

Несмотря на интенсивное использование RISC-архитектуры в серийных образцах ЭВМ, продолжаются споры вокруг достоинств и недостатков этой архитектуры. К последним, в частности, относят большую длину кода программы после компиляции (объектного кода) по сравнению с длиной кода машин обычной архитектуры. Так, при эмуляции команд ЭВМ типа VAX в среднем на каждую его команду требуется 5-6 команд машин RISC-архитектуры. Однако, как показали исследования, выигрыш в скорости выполнения команд перекрывает проигрыш от удлинения объектного кода (в общих показателях качества ЭВМ).