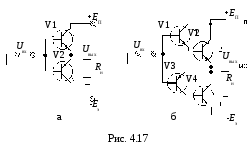

каскад управляется однофазным сигналом Uвх.Удовлетворительная симметрия входных и выходных сопротивлений обоих плеч в этой схеме достигается при нестрогом согласовании коэффициентовp-n-pиn-p-n (интегральныеp-n-p-транзисторы, как правило, имеют худшие параметры). Для точного выравнивания свойств обоих плеч двухтактного каскада в современных схемах применяется так называемый композитныйp-n-p-транзистор, состоящий из двух транзисторов, включенных особым способом (V3 и V4на рис.4.17,б).Интегральный композитныйp-n-p-транзистор позволяет с помощью низкокачественногоp-n-p-транзистора V3и обычногоn-p-n-транзистораV4 получить эквивалент высококачественногоp-n-p-транзистора с большим коэффициентом усиления, равным произведению коэффициентов усиленияp-n-p-иn-p-n-транзисторов. В верхнем плече (см. рис.4.17,б)может применяться составной транзистор V1,V2 (как на рис.3.9) или одиночныйn-p-n-транзистор. Кроме основных усилительных элементов, указанных на рис. 4.17,в выходные каскады для стабилизации режима включают дополнительные элементы, например ГСТ. Нередко применяется токовое управление выходным каскадом, например в ОУ К140УД7, который будет описан далее.

4.4.4. Операционный усилитель к140уд1

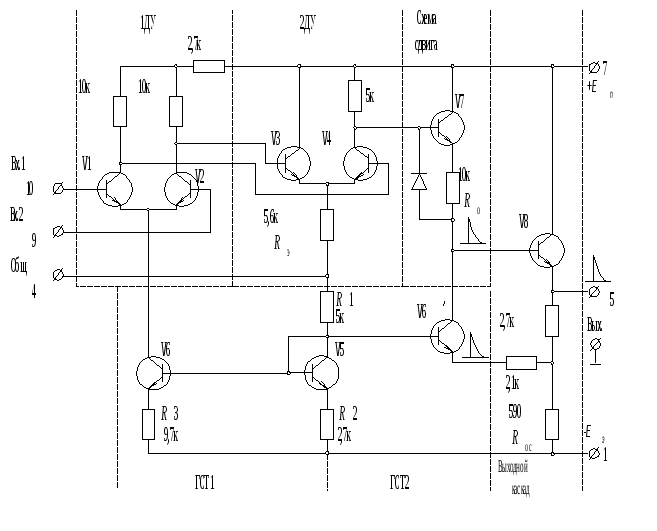

На рис. 4.18 приведена принципиальная схема многоцелевого ОУ типа К140УД1. Две разновидности этой схемы А и Б отличаются только величиной напряжения источников питания Еп, Еэ. Аналогичную схему имеет и ОУ новой разработки К140УД5 (А, Б). На рис. 4.18 пунктиром выделены все узлы ОУ, рассмотренные ранее по отдельности.

Так, схема 1ДУ соответствует схеме, показанной на рис. 4.7, схема 2ДУ совместно с устройством перехода от дифференциального сигнала к

Р ис.

4.18

ис.

4.18

одиночному – схеме на рис 4.16. Схемы генераторов стабильного тока ГСТ 1, ГСТ 2 аналогичны схемам, изображенным на рис. 4.7. Ведущим для обоих ГСТ является общий транзистор V5, через который протекает суммарный эмиттерный ток транзисторов V3, V4 второго каскада (2ДУ). При таком включении имеет место обратная связь по синфазному сигналу, еще сильнее уменьшается ООСС, определяемое равенством (4.21). На резисторе Rэ образуется напряжение сдвига вверх потенциала эмиттеров, что позволяет увеличить потенциал баз V3, V4 и коллекторов V1, V2. Схема сдвига уровня, выполненная на резисторе R0 и ГСТ 2 (соответствующая рис. 4.2), сдвигает выходное напряжение 2ДУ (Uк4) вниз на величину покоя UкА4 транзистора V4. При отсутствии сигналов на входах ОУ (9 и 10, см. рис. 4.18) сигнал на выходе схемы сдвига (коллектор V6'), а значит, и на выходе ОУ равен нулю. Для уменьшения нагрузки 2ДУ сигнал с него снимается через эмиттерный повторитель (V7). В качестве выходного каскада используется эмиттерный повторитель (V8). Особенностью выходного каскада является наличие положительной обратной связи, увеличивающей коэффициент усиления по напряжению в несколько раз. Сигнал обратной связи с резистора RОС вводится в цепь эмиттера V6'. Фазировка сигналов на схеме показана условно импульсами. Например, при положительном сигнале на выходе повышается напряжение на RОС (уменьшается отрицательное падение напряжения на RОС) и потенциал эмиттера V6', что ведет к уменьшению тока через R0 и повышению напряжения на базе транзистора V8. Таким образом, транзисторы V8, V6' образуют третью ступень усиления напряжения (амплитуды) сигнала, коэффициент усиления напряжения KU этой ступени не превышает 5 (по условиям устойчивости) [7]. Параметры ОУ приведены в табл.4.1.

4.4.5. Операционный усилитель к140уд7

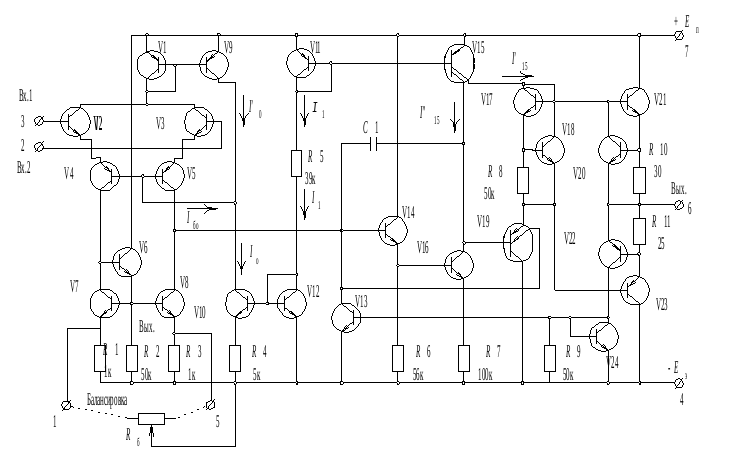

На рис. 4.19 приведена принципиальная схема двухкаскадного усилителя второго поколения типа К140УД7, в которой использованы новые схемотехнические решения и достижения технологии линейных ИС, в частности ИС-транзисторы р-n-р-типа высокого качества. Первый каскад этого ОУ выполнен по сложной схеме, приведенной на рис.4.13 (обозначения элементов входного ДУ такие же, как на рис. 4.13). Стабилизация токов в схеме осуществляется стабилизатором (ГСТ) сложной формы (транзисторы V1, V9, V10, V11, V12, V15 и резистор R5). Ведущий ток ГСТ I1, задается цепью из двух ведущих транзисторов (в режиме диода) V10, V11 и резистора R5. Пара идентичных транзисторов V10, V12, транзистор V11 и резистор R5 стабилизируют ток I0 входного ДУ (ток I0 отражает в масштабе ток I1). Ток I0 представляет сумму токов баз Iб0 транзисторов V4,V5 и токов коллекторов I0' транзисторов V2,V3 , т.е. I0 является суммой токов эмиттеров транзисторов V4,V5 (или V2,V3) , как и в схеме на рис 4.18:

![]() .

(

4.28)

.

(

4.28)

Ток I0' – это ток коллектора транзистора V9, а V9 является ведомым в ГСТ, состоящем из пары идентичных транзисторов V1, V9. Через ведущий в этой паре транзистор V1, работающий в режиме диода, протекает сумма токов коллекторов транзисторов V2, V3:

![]() . (

4.29)

. (

4.29)

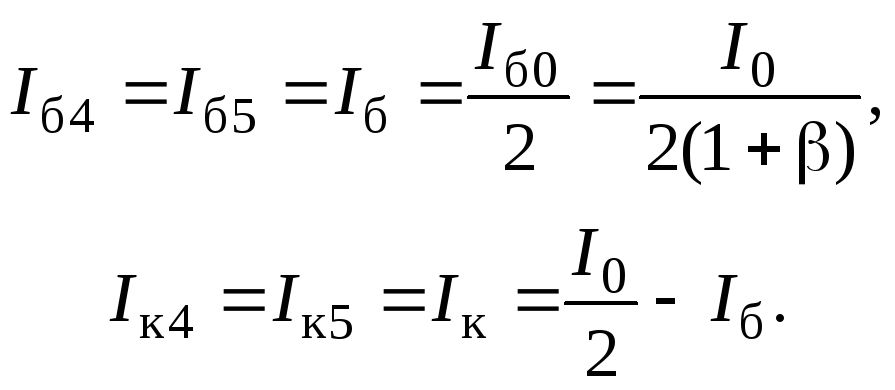

Токи баз Iб4, Iб5 (Iб2, Iб3) и токи коллекторов Iк4, Iк5 (Iк2, Iк3) автоматически (как и в схеме на рис. 4.7 , 4.18) устанавливаются на уровне

ГСТ, образованный парой идентичных транзисторов V11, V15, стабилизирует ток коллектора Iк15 транзистора V15. Транзистор V15 является ведомым в этой паре и его ток Iк15 повторяет (отражает) ток I1:

Р ис.

4.19.

ис.

4.19.

![]() . (4.30)

. (4.30)

В двухколлекторном

транзисторе V15 полный ток коллектора

Iк15

(Iк15

= 15

Iэ15)

распределяется между коллекторами 1, 2

на токи

![]() ,

,![]() ,

пропорционально площадям коллекторныхp-n-переходов.

И это распределение остается постоянным.

Ток

,

пропорционально площадям коллекторныхp-n-переходов.

И это распределение остается постоянным.

Ток

![]() участвует в токовом управлении выходным

каскадом. Второй каскад выполнен на

транзисторе V16 (по схеме ОЭ). Этот каскад

является генератором тока, пропорционального

входному дифференциальному сигналуUд

на входах ДУ (выводы 2, 3). Уже выходной

сигнал ДУ является токовым - ∆Iн

(см. рис. 4.13). Этот сигнал (∆Iн)

усиливается эмиттерным повторителем

на V14 и подается в базу V16 (∆Iб16

= ∆Iн

(1 + 14)).

Ток ∆Iб16

усиливается транзистором V16 (∆Iк16

= ∆Iн

(1 + 14)

16).

участвует в токовом управлении выходным

каскадом. Второй каскад выполнен на

транзисторе V16 (по схеме ОЭ). Этот каскад

является генератором тока, пропорционального

входному дифференциальному сигналуUд

на входах ДУ (выводы 2, 3). Уже выходной

сигнал ДУ является токовым - ∆Iн

(см. рис. 4.13). Этот сигнал (∆Iн)

усиливается эмиттерным повторителем

на V14 и подается в базу V16 (∆Iб16

= ∆Iн

(1 + 14)).

Ток ∆Iб16

усиливается транзистором V16 (∆Iк16

= ∆Iн

(1 + 14)

16).

Токовое управление выходным каскадом. Выходной каскад на транзисторах V21, V23 аналогичен каскаду на рис.4.17,а, показанному и описанному в подразделе 4.4.3. Для уменьшения искажений (задания режима АВ) постоянный потенциал баз V21, V23 разнесен на величину 2UбэА, стабилизированную источником малого опорного напряжения (транзисторы V17, V18), включенного между базами точно так же, как диод D на рис.3.9. К цепям баз выходных транзисторов V21, V23 подключены два генератора тока:

1. Часть тока Iк15

(![]() ):

):

![]() .

(4.31)

.

(4.31)

2. Часть тока Iк16

(за вычетом

тока

![]() ),

усиленная эмиттерным повторителем на

V19:

),

усиленная эмиттерным повторителем на

V19:

![]() .

(4.32)

.

(4.32)

Величина токов

баз Iб21,

Iб23

выходных

транзисторов определяется разностью

токов генераторов тока (4.31), (4.32), а не

напряжением предоконечного каскада,

как на рис. 3.9. При этом ток

![]() (4.31) не изменяется, а только перераспределяется

(под управлением V16) между цепями базы

V21 и коллектора V16 (через транзистор

V19).

(4.31) не изменяется, а только перераспределяется

(под управлением V16) между цепями базы

V21 и коллектора V16 (через транзистор

V19).

В режиме покоя

токи (4.31) и (4.32) равны. Токи эмиттеров

транзисторов V21,V23 также равны, Uвых

= 0. При этом

ток

![]() полностью протекает в коллектор V16

(через V19). При увеличении отрицательного

сигнала выхода ДУ (∆Iн

< 0)

уменьшается ток Iк16

. Ток

полностью протекает в коллектор V16

(через V19). При увеличении отрицательного

сигнала выхода ДУ (∆Iн

< 0)

уменьшается ток Iк16

. Ток

![]() переходит (вытесняется) в базу VT21 на

величину, равную уменьшениюIк16,

умноженную на (1+19):

переходит (вытесняется) в базу VT21 на

величину, равную уменьшениюIк16,

умноженную на (1+19):

![]() .

.

Повышается ток

коллектора (эмиттера) V21 и на выходе

увеличивается положительный сигнал.

Для получения максимального положительного

сигнала на выходе (+Uвых.мах)

ток

![]() должен быть не менееIб21

мах:

должен быть не менееIб21

мах:

![]() .

.

В режиме покоя ток Iк16А должен быть не менее следующей величины:

![]() .

(4.33)

.

(4.33)

При увеличении

положительного сигнала выхода ДУ (∆Iн

> 0)

увеличивается ток Iк16

сверх тока

покоя (4.33) (сверх тока

![]() ).

Разница

).

Разница![]() втекает в коллектор V16 из базы V23.

Повышается ток коллектора (эмиттера)

V23. На выходе увеличивается отрицательный

сигнал. Для получения максимального

отрицательного сигнала токIк16

должен увеличиваться сверх тока (4.33) на

величину, не менее Iб23

max:

втекает в коллектор V16 из базы V23.

Повышается ток коллектора (эмиттера)

V23. На выходе увеличивается отрицательный

сигнал. Для получения максимального

отрицательного сигнала токIк16

должен увеличиваться сверх тока (4.33) на

величину, не менее Iб23

max:

![]() .

.

Защита выхода ОУ от перегрузки. Элементы V20, R10 осуществляют защиту выхода ОУ от короткого замыкания (от перегрузки) при положительном сигнале. При большом положительном токе выхода в результате падения напряжения на R10 открывается транзистор V20, который шунтирует вход транзистора V21, предотвращая дальнейшее нарастание тока выхода. Защита выхода от короткого замыкания при отрицательном сигнале выполняется элементами V22, R11, V24, R9, VI3. При большом отрицательном выходном токе в результате падения напряжения на R11 открывается транзистор V22. Ток транзистора V22 усиливается транзистором VI3, производится шунтирование входа эмиттерного повторителя V14 и второго эмиттера транзистора VI9, что предотвращает дальнейшее увеличение сигнала на входе транзистора V23, а значит, и увеличение выходного тока. Параметры ОУ типа К140УД7 приведены в табл. 4.1.