dsd13-gos / dsd-17=dacs and adcs / 08. АЦП с временным перемежением. Параллельные АЦП. Интерполирующий АЦП. АЦП сложенного сигнала

.docЛекция 8. АЦП с временным перемежением. Параллельные АЦП. Интерполирующий АЦП. АЦП сложенного сигнала

АЦП с временным перемежением

Пример АЦП с временным перемежением приведен на рис. 8.1.

Рис. 8.1. 4–х канальный N – разрядный АЦП с временным перемежением

Тактовая

частота

![]() в четыре раза больше тактовых частот

в четыре раза больше тактовых частот

![]() ,

,![]() ,

,![]() ,

,![]() (рис.

8.1.) Частоты

сдвинуты относительно друг друга на

равный период. Внутренние АЦП должны

быть идеально согласованы друг с другом.

В противном случае в выходном сигнале

неизбежно появление паразитных частот.

(рис.

8.1.) Частоты

сдвинуты относительно друг друга на

равный период. Внутренние АЦП должны

быть идеально согласованы друг с другом.

В противном случае в выходном сигнале

неизбежно появление паразитных частот.

Параллельный АЦП

Параллельный АЦП – один из наиболее быстродействующих АЦП (рис. 8.2, а). Его реализация требует большую площадь кристалла и расходует большую мощность.

а)

б)

Рис. 8.2. Параллельный 3–х разрядный АЦП

Основными факторами, ухудшающими характеристики АЦП, являются:

– большая входная емкость, вызванная большим количеством компараторов подсоединенных ко входу; неравномерность последовательности напряжений на резистивном делителе, вызванная втекающим в компараторы током смещения или необходимостью перераспределения заряда в процессе преобразования;

– неопределенность времени стробирования входного сигнала, вызванная сдвигом сигналов стробирования, различием уровней входного аналогового сигнала, задержками прохождения сигнала во внутренних цепях;

– шумами в цепях питания и по подложке;

– помехами, вызванными прохождением тактовых сигналов в ключах и других элементах схемы;

– зависимостью сопротивления входных ключей от уровня аналогового сигнала.

Для исключения одиночных помех в последовательности выходных кодов компараторов используется строка элементов И–НЕ (рис. 8.2, б) или других логических элементов, а так же код Грея в качестве промежуточного от единичного кода до двоичного выходного кода.

1,5 – шаговый параллельный АЦП

Структурная схема 1,5-шагового параллельного АЦП приведена на рис. 8.3.

Рис. 8.3. 1,5 – шаговый параллельный АЦП

1,5-шаговый параллельный АЦП позволяет увеличить разрядность быстродействующего преобразователя при приемлемых аппаратных затратах. В такой конструкции появляются дополнительные погрешности, вызванные стыковкой различных поддиапазонов. Часть проблем решается путем усложнения конструкции, в частности за счет перекрытия поддиапазонов. По сравнению с одношаговым параллельным АЦП требуется более точная настройка характеристик узлов.

Интерполирующий АЦП

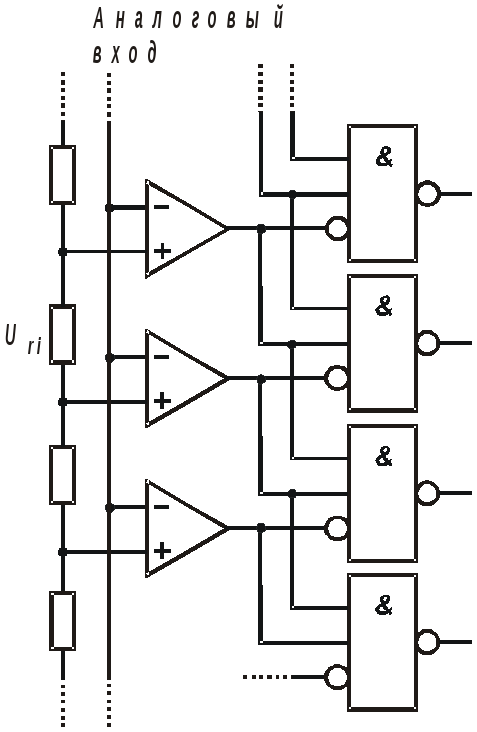

Пример построения интерполирующего АЦП приведен на рис. 8.4.

а)

б)

Рис. 8.4. Интерполирующий 4 – х разрядный АЦП: а — электрическая схема; б — передаточная характеристика

В качестве компараторов в интерполирующем АЦП (рис. 8.4, а) могут быть использованы простые «защелки». Это возможно за счет использования предварительных усилителей, которые линейно усиливают входной сигнал в своем рабочем диапазоне и вне диапазона входят в насыщение. Преимуществом также является существенное уменьшение входной емкости.

Двухшаговый параллельный АЦП

Схема электрическая двухшагового параллельного АЦП приведена на рис. 8.5.

Рис. 8.5. Двухшаговый параллельный АЦП

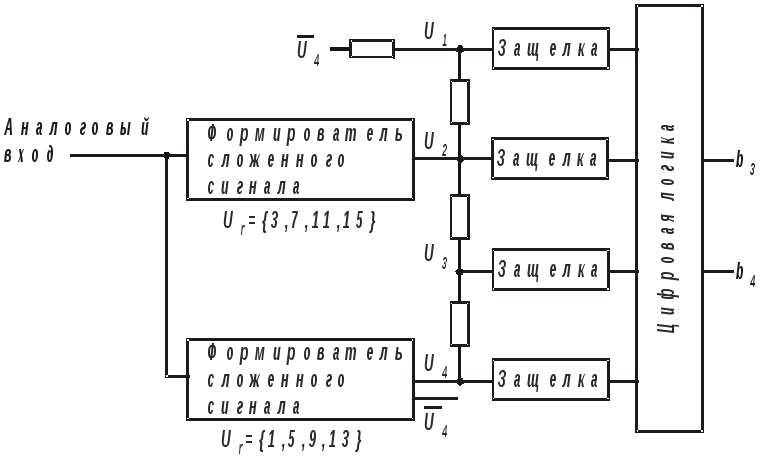

АЦП сложенного сигнала

На рис. 8.6 приведены диаграммы работы и структурная схема АЦП сложенного сигнала.

а)

б)

в)

г)

Рис. 8.6. АЦП сложенного сигнала

В АЦП сложенного сигнала, как и в двух–шаговом АЦП, старшие и младшие разряды определяются раздельно. Младшие разряды определяются на основе пилообразной передаточной характеристики (рис. 8.6, а). Для их определения используются специальные усилители – формирователи сложенного сигнала. Чтобы избежать нелинейности в пиках зубцов передаточной характеристики, используется наложение друг на друга характеристик соседних формирователей (рис. 8.6, б). Так как формирователь сложенного сигнала является усилителем, то компаратором на его выходе может быть простая защелка (рис. 8.6, в).

С целью уменьшения количества формирователей сложенного сигнала, для определения младших разрядов используется комбинированная с интерполирующим АЦП схема (рис. 8.6, г). Этот способ позволяет также уменьшить входную емкость АЦП, которая в противном случае соответствует емкости параллельного АЦП.

К недостаткам АЦП сложенного сигнала следует отнести повышенную частоту сигналов во внутренних узлах (рис. 8.6, в) в узлах U1, U2, U3, U4 по сравнению с частотой входного сигнала.

Архитектура совмещенного АЦП интерполирующего и сложенного сигнала позволяет достичь оптимального соотношения скорости, рассеиваемой мощности и площади кристалла для многих применений.