dsd1-10 / dsd-06=Kruglov+АИС / PDF / 4_SC_Types

.pdf

ЭЛЕМЕНТАРНОЕ ВВЕДЕНИЕ В КОНЦЕПЦИЮ ПЕРЕКЛЮЧАЕМЫХ КОНДЕНСАТОРОВ

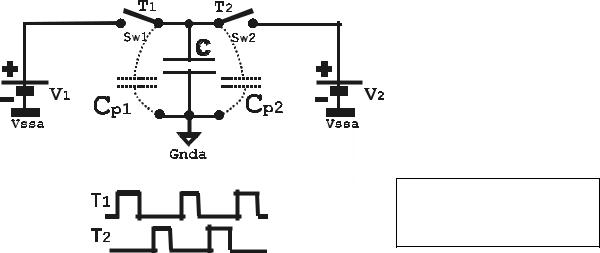

Переключаемый конденсатор, чувствительный к паразитным емкостям.

Рис.3.5. Простейший Переключаемый Кон-

денсатор (ПК)

Примечания.

•Вначале для простоты рассуждений предполагается, что источники напряжений, к которым подключается Переключаемый Конденсатор (ПК) С, яв-

ляются постоянными, т.е. V1 и V2.

•Пусть V1 > V2.

•Такты Т1 и Т2 не перекрываются, так что отсутствует перекрытие во време-

ни замкнутых состояний ключей.

При замыкании ключа Т1 в начале N – го такта, конденсатор С1, а также паразит-

ные емкости СР1 и СР2 заряжаются до V1. Далее ключ Т1 размыкается, через ко-

роткий промежуток времени замыкается ключ Т2, и эти же емкости заряжаются до V2. Результирующий эффект этого процесса – перенос заряда, равного по абсо-

лютной величине (C + CP1 + CP2 )(V1 −V2 ), из источника напряжения V1 в ис-

точник напряжения V2.

За 1 секунду между источниками V1 и V2 проходит заряд, численно равный

среднему току: |

|

|

|

|

|

|

(V1 −V2 ) |

|

|

|||

I = (C + C |

P1 |

+ C |

P2 |

)(V −V ) |

× F = |

, |

(3.10а) |

|||||

|

||||||||||||

|

|

|

1 |

2 |

|

S |

Reff |

|

||||

|

|

|

|

|

|

|

|

|

|

|||

где Reff = |

|

|

|

|

1 |

|

|

- эффективное сопротивление ПК. (3.10в) |

||||

FS × |

(C+ |

CP1+ |

CP2 ) |

|||||||||

|

|

|

|

|

||||||||

Рассчитаем эффективное сопротивление ПК. |

||||||||||||

Пусть: |

(C + CP1 + CP2 )= 1 пФ; Fs = 100 кГц. |

ТогдаReff = 10 Мом - ве- |

||||||||||

личина, достижимая только при использовании усложненного технологического процесса, включающего изготовление на кристалле высокоомных резисторов.

Возможность получать высокоомные сопротивления - первое ос-

новное достоинство метода ПК (о втором основном достоинстве метода ПК –

ниже).

Обращаем, однако, внимание, что параллельно С1 подключены паразитные конденсаторы СР1 и СР2, добавляющие свой заряд к заряду С1. Роль этих конден-

саторов практически невозможно учесть с приемлемой точностью ввиду их нелинейности и недостаточной воспроизводимостью параметров кристалла в обед-

ненных областях P – N переходов. Далее описываются типы ПК, не зависящие от паразитных емкостей.

ПК, изображенный на Рис. 3.5 называется неинвертирующим ПК, посколь-

ку в V2, т.е. коллектор передаваемого заряда, передается заряд со знаком, аналогичным знаку заряда, переходящего из V1 в V2 при простом соединении источ-

ников V1 и V2 резистором.

Описание поведения ПК на Рис. 3.5 в дискретном времени.

Пусть теперь потенциалы источников напряжений, к которым подключается Переключаемый Конденсатор, изменяются во времени.

Пусть момент перехода такта Т1 из логического нуля в логическую единицу, т.е.

T1 1, является началом очередного такта. Пусть в момент T1 0 внутри N -1

– го такта переключаемый конденсатор (C + CP1 + CP2 ) отключается от источ-

ника напряжения V1. Поскольку момент T1 0 очень близок к середине N -1 – го

такта, обозначим его как момент времени N − 12 . Мгновенное значение входно-

го напряжения V |

|

1 |

в моментN − |

1 |

запоминается на конденсаторах |

|

1 N − |

|

|

2 |

|

|

|

2 |

|

|

||||

|

|

|

|

|

|

|

(C + CP1 + CP2 ). |

Чуть позже, практически в этот же момент, T2 1, и накоп- |

|||||

ленный на емкостях заряд (C + CP1 |

+ CP2 )× V |

1 передается в источник |

||||

|

|

|

|

|

1 N − |

|

|

|

|

|

|

|

2 |

напряжения V2. Поскольку реальные ключи имеют ненулевое, т.е. конечное сопротивление канала, перенос заряда от конденсаторов в V2 происходит не мгно-

венно, и время от момента T2 1 до момента T2 0, равное почти половине периода, есть время для разряда конденсаторов до приемлемой точности. Окон-

чание переноса заряда приходится на момент N . Из приведенных рассуждений явствует, что описываемый ПК осуществляет задержку на половину такта, и называется «ПК с задержкой». Отметим, однако, что если величина V1 ме-

няется только на границах тактов, т.е. если предыдущие цепи осуществля-

ют функцию выборки – хранения, то описываемый ПК осуществляет задерж-

ку на целый такт.

Из описания работы ПК следует, что изменение потенциала на выходном

узле ПК происходит с периодичностью один такт, следовательно узлы основе ПК осуществляют функцию выборки – хранения. В большинстве схем на ПК сущест-

вует лишь один ПК, а, именно, на границе ПК – системы и внешним аналоговым миром, у которого входной сигнал непрерывен во времени. У остальных же ПК, которых достаточно много, входной сигнал меняется именно на границах тактов,

поскольку определяется предыдущими ПК. Поскольку именно эти, остальные ПК,

в основном определяют передаточную функцию ПК – системы, принято при ана-

лизе ПК схем считать, что задержка в переключаемом конденсаторе с задержкой равна целому такту, т.е. единице. Учет отличия задержки от едини-

цы в (как правило) единственном ПК проводится отдельно, однако, в большинстве

ПК – систем достаточно высокого порядка такое уточнение несущественно. Суммируя приведенное выше, отметим, что такой ПК называется «неинвертирую-

щий ПК с задержкой».

Можно написать, что заряд, переходящий из V1 |

в V2 удовлетворяет сле- |

дующему выражению: |

|

Q2(N ) = (C + CP1 + CP2 )× V1(N −1) |

(3.11) |

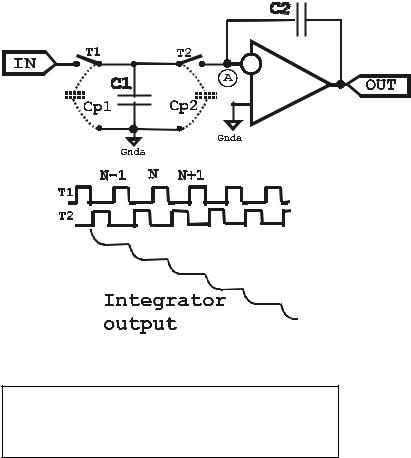

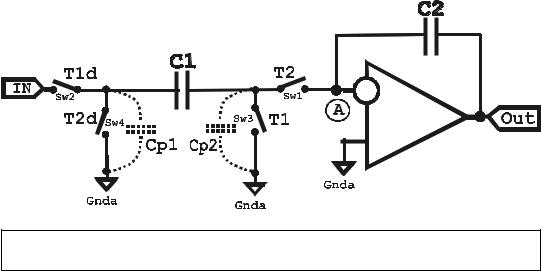

Простейший активный интегратор на ПК

Рис.3.6. Активный интегратор с простейшим ПК, чувствительным к паразитным емкостям

Предположим для простоты, что ОУ в соста-

ве интегратора на ПК имеет неопределенно боль-

шое, т.е. бесконечное, дифференциальное усиление, а потенциал источ-

ника напряжения VIN – положителен.

Передаточная

функция непрерывного

интегратора:

H (s) = − |

1 |

× |

1 |

|

s |

RC2 |

|||

|

|

Формально заменим

резистор его эквивален-

том на ПК (3.10в):

R |

|

|

|

|

1 |

|

|

|

. |

(C + C |

P1 |

+ C |

P2 |

) |

× F |

||||

1 |

|

|

|

S |

|||||

|

|

|

|

|

Тогда: |

|

|

||

H (s) − |

F |

|

× |

(C1 + CP1 + CP2 ) |

|||||

S |

|

|

|

C2 |

|||||

|

|

|

|

||||||

|

|

s |

|

|

|

|

|

||

При замыкании ключа Т2, в первый момент суммарный заряд на С1, СР1 и

СР2 распределяется между этими емкостями и входной емкостью инвертирующего входа ОУ, в результате чего изменяется его потенциал. Знак изменения выходно-

го напряжения VOUT – противоположный, и заряд, приходящий на правую обкладку С2 противоположен знаку потенциала на инвертирующем входе. Для сохранения суммарной электронейтральности обеих обкладок конденсатора С2, из левой об-

кладки С2 в цепь инвертирующего входа «выталкивается» заряд со знаком, аналогичном знаку заряда, добавляемому на правую обкладку С2, но противоположному знаку заряда, пришедшему от ПК на инвертирующий вход ОУ. В результате за-

ряд, пришедший от ПК на инвертирующий вход ОУ, компенсируется. Процесс

компенсации продолжается до тех пор, пока потенциал инвертирующего входа не станет нулевым.

При достижении этого результата весь заряд, пришедший от ПК в цепь инвертирующего входа ОУ, компенсируется. При этом оказывается, что из левой об-

кладки С2 «вытолкнут» заряд, противоположный по знаку, но одинаковый по абсолютной величине заряду, пришедшему от ПК на инвертирующий вход ОУ. Ре-

зультат аналогичен переходу всего заряда, пришедшего на инвертирующий вход ОУ, на интегрирующий конденсатор С2. Именно это умозаключение всегда имеется в виду при анализе активного интегратора на ПК.

Итак, заряд, задержанный на такт и равный по абсолютной величине |

|||||

VIN (N −1) × (C1+ CP1+ CP2 ), перейдя на конденсатор С2, изменяет напряжение |

|||||

на нем и, следовательно, на выходе ПК интегратора, на |

|

||||

∆ V |

= − V |

IN (N −1) |

C1 + CP1 + CP2 |

. |

(3.12) |

|

|||||

OUT (N ) |

C2 |

|

|||

|

|

|

|

||

В результате, если, например, VIN = const , напряжение на выходе ПК ин-

тегратора изменяется (в сторону, противоположную знаку VIN) скачками (см. Рис.

3.6), причем огибающая этих скачков является прямой, как в непрерывном интеграторе.

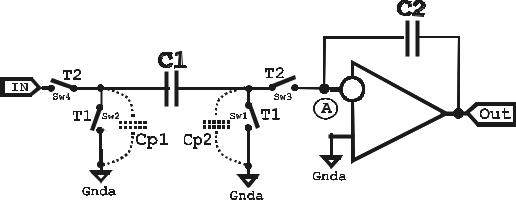

Неинвертирующий переключаемый конденсатор, нечувствительный к паразитным емкостям.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Для устранения влия- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ния паразитных кон- |

|

Рис. 3-7. Неинвертирующий ПК без задержки, нечув- |

|||||||||||||||

денсаторов предло- |

|||||||||||||||

ствительный к паразитным ёмкостям. |

|||||||||||||||

жена другая схема |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

коммутации переключаемого конденсатора (см. рис. 3-7). Здесь Сp1 и Сp2 - пара-

зитные ёмкости ключей. Пусть требуется передать заряд из источника напряже-

ния V1 в другой источник V2. Имеется также третий источник постоянного напряжения V3, одинаковый с V2.

Пусть будут справедливы примечания, приведенные выше при анализе ПК на Рис. 3.5.

Ключи, Sw1 и Sw2, управляемые тактовым сигналом Т1, замкнуты, ключи Sw3 и Sw4 - разомкнуты: T1 1.

Конденсатор С разряжен, обе обкладки имеют потенциалы V3= V2; паразитные

конденсаторы Сp1 и Сp2 также заряжены до напряжения V3= V2. Заряды, бывшие

на обеих обкладках конденсатора, уходят в источник V3, и в результате заряд, хранимый на конденсаторе, равен нулю.

Ключи, Sw3 и Sw4, управляемые тактовым сигналом Т2, замкнуты, ключи Sw1 и Sw2 - разомкнуты: T2 1.

Паразитный конденсатор Сp2 не перезаряжается; левая обкладка конденсатора С

заряжается до V1, а правая – до V2. Заряды на обкладках, равные по абсолютной величине С(V1-V2) и противоположные по знаку, берутся из источников V1 и V2. Из источника V1 берется положительный заряд, а из V2 – такой же по величине,

но отрицательный. Можно рассуждать по – другому: для сохранения электронейтральности конденсатора из правой обкладки ПК «выталкивается» положи-

тельный заряд, равный С(V1-V2) и непосредственно попадает в V2. При любом методе рассуждения результирующий эффект – перенос в каждом такте в V2 положительного заряда величины С(V1-V2). Как видно, паразитные конденсаторы не

переносят в V2 никакого заряда. Конечно, паразитный конденсатор Сp1 при этом перезаряжается, но это не должно беспокоить, т.к. он связан с источником вход-

ного напряжения V1, т.е. с источником заряда.

Так же, как и ПК на Рис. 3.5, анализируемый ПК на Рис. 3.7 является неин-

вертирующим ПК, поскольку в V2, т.е. коллектор передаваемого заряда, пере-

дается заряд со знаком, аналогичным знаку заряда, переходящего из V1 в V2 при простом соединении источников V1 и V2 резистором.

Описание поведения ПК на Рис. 3.7 в дискретном времени.

Пусть теперь на Рис. 3.7, как в одноименном анализе для ПК на Рис. 3.5, слева – источник изменяющегося во времени напряжения V1, а справа – источник постоянного напряжения V2. Как явствует из описания работы ПК на Рис. 3.7, отрицательный заряд переносится из источника V2 на правую обкладку ПК в

моменты времени, совпадающие с моментами времени подключения ПК к V1, т.е.

переноса положительного заряда из источника V1 на левую обкладку ПК. В этом случае отсутствует задержка в передаче заряда от V1 к V2. Такие ПК назы-

ваются «неинвертирующие ПК без задержки». Заряд, поступаемый из V1 в V2:

Q2(N ) = C × V1(N ) |

(3.13) |

Если этот процесс повторяется в каждом такте с частотой FS, то средний ток I ,

текущий от V1 в V2 : |

I = C × V1× |

FS , а эквивалентное сопротивление: |

|

R = |

1 |

|

(3.14) |

C × F |

|

||

|

S |

|

|

Инвертирующий активный интегратор без задержки

Рис.3.8. Инвертирующий активный интегратор без задержки

Предположим для простоты, что ОУ в составе интегратора на ПК имеет неопределенно большое, т.е. бесконечное, дифференциальное усиление, а потен-

циал источника напряжения VIN – положителен.

Ключи, управляемые тактовым сигналом Т2 - замкнуты: T2 1.

Сравнивая неинвертирующий ПК на Рис. 3.7 с активным интегратором на его основе на Рис. 3.8, очевидно, что V3 = 0, поскольку неинвертирующий вход ОУ (узел

А) является виртуальной землей.

Следуем рассуждениям предыдущих глав.

При T2 1из правой обкладки ПК «выталкивается» заряд С1VIN, из - за чего по-

тенциал инвертирующего входа ОУ (узел А) становится положительным, а знак изменения потенциала VOUT выхода интегратора – отрицательным. В результате

из левой обкладки интегрирующего конденсатора С2 «выталкивается» отрицательный заряд, компенсирующий положительный заряд узла А. Движение VOUT в

отрицательную сторону происходит до тех пор, пока весь положительный заряд СVIN в узле А не скомпенсируется. Если учесть, что ПК, используемый в рассмат-

риваемом ПК интеграторе – без задержки, то результирующий эффект – изменение без задержки выходного напряжения в сторону, противоположную знаку входного напряжения:

∆ VOUT (N )= − |

VIN (N )× |

C1 |

(3.15) |

C2 |

Разумеется, как ключи, так и ОУ – инерционные элементы, поэтому выражение «без задержки» означает то, что начало изменения VOUT происходит без задерж-

ки относительно момента времени, при котором T2 1. Окончание переходного

процесса – начало следующего такта.

Если в ARC интеграторе формально заменить резистор его эквивалентом (3.14),

то передаточная функция такого интегратора: H (s) |

1 |

|

FS |

× |

C1 |

. От- |

s (RC2 ) |

s |

C2 |

сюда следует второе основное достоинство метода ПК: точность по-

стоянной времени ПК интегратора на базе ПК, не чувствительного к паразитным емкостям, зависит не от абсолютных значений сопротивления и емкости (номинал каждого из этих компонентов изменяется от

партии к партии в пределах ±20%), а от отношения емкостей |

C1 |

, равной |

C2 |

||

0.1 – 0.2 % для большинства технологических процессов. |

|

|

Инвертирующий переключаемый конденсатор с задержкой, нечувствительный к паразитным емкостям.

Рис.3.9. Инвертирующий переключаемый кон-

денсатор с задержкой, нечувствительный к паразитным емкостям.

Как и раньше, предположим для простоты, что:

•ОУ в составе интегратора на ПК имеет неопределенно большое, т.е. беско-

нечное, дифференциальное усиление;

•V3 = V2;

• потенциал источника напряжения V1 – положителен относительно V3 и V2.

•Рассматриваемый тип ПК является самым «емким» в части количества учитываемых физических эффектов, и его удобно анализировать, сразу полагая источник напряжения V1, присоединенный к левой обкладке - источни-

ком изменяющегося во времени сигнала. Правая обкладка может быть присоединена к постоянным во времени источникам напряжения V2 и V3 = V2.

Как и раньше, левая и правая обкладки ПК управляются неперекрывающимися

тактовыми сигналами Т1 и (см. Рис. 3.9), т.е. отсутствует возможность одновременного замкнутого состояния ключей, управляемых тактами с нижними индексами 1 и 2. В отличие от Рис. 3.7, тактовые сигналы Т1d и Т2d, управляющие левой

обкладкой, во – первых, поменялись местами и, во – вторых, являются задержанными (индексы в Т1d и Т2d - от «delayed») относительно тактов Т1 и Т2.

Пусть моменты времени, когда T1 1, являются началами (и одновременно – концами) тактов. Пусть также промежутки времени между моментами T1 1, T1d 1, T2 0 и T2d 0 настолько малы в сравнении с периодом тактового сигнала, что все моменты, перечисленные в этом абзаце, являются началами (и одновременно – концами) тактов. А моменты T1 0 , T1d 0, T2 1 и

T2d 1 являются серединами периодов тактового сигнала.

Поведение ПК в дискретные моменты времени.

Ключи, Sw1 и Sw2, управляемые тактовыми сигналами Т1 и Т1d соответственно – замкнуты, ключи Sw3 и Sw4 - разомкнуты:

T1 1, T1d 1.

Левая обкладка ПК заряжена до положительного потенциала V1, правая обкладка заряжена до отрицательного относительно V1 потенциала V3.

Ключ, Sw1, управляемый тактовым сигналом Т1 – размыкается. Затем размыкается ключ Sw2, управляемый тактом Т1d.:

T1 0 , затем T1d 0.

Пусть такт T2 еще равен нулю, а T1d еще равен единице. Правая обкладка ПК

является плавающей с момента T1 0 , |

поэтому на ПК находится заряд, соот- |

||||||||

ветствующий мгновенному напряжению V1 в момент T1 0 . Пусть этот момент |

|||||||||

равен N − |

1 |

, и соответствующий заряд: |

Q |

1 |

= V |

1 |

× C |

(3.16) |

|

|

|||||||||

2 |

|

1 N − |

|

|

1 N − |

|

|

|

|

|

|

2 |

|

||||||

|

|

|

|

2 |

|

|

|

||

При любом порядковом номере момента T1 0 правая обкладка ПК имеет оди-

наковый потенциал, равный V3, т.е. не зависящий от значения V1. По этой причи-

не величина заряда, инжектированного в правую обкладку при размыкании ключа

Sw1 в момент T1 0 , не зависит от V1 и, следовательно, не порождает нели-

нейных искажений. В момент T1 0 левая обкладка ПК должна быть соединена

с источником напряжения (в данном случае – с V1), чтобы не препятствовать приходу на эту обкладку из источника напряжения заряда, равного по абсолютной ве-

личине заряду, инжектированному в левую обкладку. Если гипотетически предпо-

ложить, что такт Т1 размыкает не Sw1, a Sw2, соединяющий левую обкладку с V1,

то заряд, инжектированный в левую обкладку, будет зависеть от значения V1 в этот момент и, как следствие, возникнут нелинейные искажения. Отсоединение

же левой обкладки от V1 позже отсоединения правой от земли, т.е. в момент

T1d 0, не привносит никакого дополнительного заряда в левую обкладку, по-

скольку правая обкладка в этот момент является плавающей и не может обмениваться зарядом с источником напряжения.

ИТАК, ОЧЕРЕДНОСТЬ РАЗМЫКАНИЯ КЛЮЧЕЙ ПК, ПРИ КОТОРОЙ СНАЧАЛА РАЗМЫКАЕТСЯ КЛЮЧ, СОЕДИНЯЮЩИЙ ОБКЛАДКУ ПК С ИСТОЧНИКОМ ПОСТОЯННОГО НАПРЯЖЕНИЯ, НЕ ПРИВНОСИТ НЕЛИНЕЙНЫХ ИСКАЖЕНИЙ.

Ключи Sw3 и Sw4 поочередно замыкаются, ключи Sw1 и Sw2 - разомкну-

ты: T2 1, затем T2d 1.

Первым, в N – й такт, в момент T2 1, замыкается ключ Sw3, соединяю-

щий правую обкладку ПК с источником постоянного напряжения V2. Поскольку V3 = V2, зарядовое состояние ПК не изменяется.

Далее, при T2d 1, потенциал левой обкладки стал более отрицательным

на величину |

V |

= V |

1 |

|

−V . |

(3.17) |

|

1(N ) |

1 N − |

|

3 |

|

|

|

|

2 |

|

|

||

|

|

|

|

|

|

Для сохранения нулевого суммарного заряда ПК, отрицательный заряд

такой же величины «выталкивается» из правой обкладки в источник V2. Разумеется, учитывая эффект инжекции заряда при размыкании Sw1, этот заряд отличается от (3.17) на постоянную величину, но это не создает нелинейных искажений.

Имея в виду доводы, изложенные выше при описании простейшего ПК с за-

держкой, можно написать: |

|

Q1(N ) = (V1(N −1) −V3 )× C |

(3.18) |

ИЗ ИЗЛОЖЕННОГО В ПОСЛЕДНЕМ РАЗДЕЛЕ ОЧЕВИДНО, ЧТО НЕСМОТРЯ НА ПОЛОЖИТЕЛЬНЫЙ ЗНАК V1 ОТНОСИТЕЛЬНО V2, В V2 ИЗ V1 ПЕРЕХОДИТ ОТРИЦАТЕЛЬНЫЙ ЗАРЯД!!! ИЗ – ЗА ЭТОГО СВОЙСТВА, ПК НА РИС. 3.9 НАЗЫВАЮТ ИНВЕРТИРУЮЩИМ ПК С ЗАДЕРЖКОЙ.

Ненвертирующий активный интегратор с задержкой

Рис. 3.10. Ненвертирующий активный интегратор с задержкой

Как следует из приведенного выше описания инвертирующего ПК с задержкой, в выходной узел приходит заряд с полярностью, противоположной полярно-

сти заряда, протекающего между V1 и V2 при соединении их резистором. Например, при положительном знаке V1 относительно V2, в V2 из V1 поступает от-

рицательный заряд. В интеграторе на базе такого ПК роль V2 выполняет инвертирующий вход ОУ. Базируясь на рассуждениях, приведенных выше при анализе ПК интеграторов, следует вывод, что интегратор является неинвертирую-

щим, а скачок потенциала на выходе ОУ (т.е. на выходе ПК интегратора) в конце N – го такта равен:

∆ VOUT (N )= VIN (N −1)× |

C1 |

(3.19) |

C2 |