- •1 Синтез комбінаційних схем.

- •1.1 Синтез комбінаційних схем в базисі.

- •1.2. Синтез комбінаційних схем на мультиплексорах.

- •1.3 Індикація буквених повідомлень

- •2.1 Ап-2 чотирьох розрядний регістр зсуву ліворуч.

- •2.2 Ап-3 4-х разрядний реверсивний двійковий лічильник, працюючий в коді Грея з модулем 10

- •2.3 Ап-1 Прилад розпізнавання послідовності імпульсів 1101;0110;0011;1100. Без перекриття.

- •3.Структурна схема розроблювального пристрою

1.3 Індикація буквених повідомлень

У даній курсовій роботі необхідно індиціювати такі повідомлення

Таблиця 2

|

Адрес |

Сообщен. |

№ инд |

d |

c |

b |

a |

g |

f |

e |

|

1101 |

Б |

I |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

А |

II |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

Н |

III |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

А |

IV |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

Н |

V |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

|

0110 |

Р |

I |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

Е |

II |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

Б |

III |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

Р |

IV |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

О |

V |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0011 |

В |

I |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

Р |

II |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

А |

III |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

Г |

IV |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1100 |

2 |

I |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

|

3 |

II |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

|

4 |

III |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

|

5 |

IV |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Рис 1.4

На

схемі індикації (додаток 1) присутні два

декодера, які перетворюють двійковий

код в унарний.

На

схемі індикації (додаток 1) присутні два

декодера, які перетворюють двійковий

код в унарний.

Унарний код – двійковий, багато розрядний, паралельний код, з сигналом високого рівня тільки в одному розряді.

На стробуючи входи двух декодерів для їх роботи подаємо змінні:

на 1-й DC:

на 2-й DC:

З виходів DC сигнали подаємо на входи шифраторів(CD).Після цього виходи з шифраторів складаємо та подаємо на семисегментний індикатор.Для складання використовуємо мікросхеми типу 1533ЛА3.

2

Автомати з пам'яттю

2

Автомати з пам'яттю

У якості елементів пам'яті автоматів використовують тригери. Тригер – простійший автомат з пам'яттю,у якого два внутрішніх стану – 0 та 1. Тригери поділяються на 5 видів:

1. Т-тригер – суматор.

2. D-тригер – тригер затримки.

3. с – тригер установки-скиду.

![]()

5.JK-тригер – універсальний тригер.

2.1 Ап-2 чотирьох розрядний регістр зсуву ліворуч.

Регістр зсуву є схемою складається із зв'язаних між собою однобітових елементів пам'яті, розташованих в єдиному корпусі, яка називається - Інтегральна схема.

Елементами пам'яті є трігери, сполучені один з одним таким чином, що вхід одного служить виходом іншого.

Використовуються для тимчасового зберігання даних, перетворення даних з паралельної в послідовну і навпаки.

Розрізняють регістри зсуву із зсувом ліворуч, праворуч або реверсивні. Мають стільки розрядів, скільки розрядів має інформація.

Даний автомат є автоматом другого роду (Мура), сигнали якого виходів співпадають з його внутрішнім станом.

Синтез синхронного автомата складається з 4 етапів.

На першому етапі будується граф переходів. Рух по цьому графу буде починатися з початкового стану відповідно до зсуву інформації. Даний автомат з початкового стану перейде в наступне із зсувом ліворуч, тобто під впливом вхідного сигналу х=1 автомат перейде з 0000 стани в 0001 стан.

На другому етапі синтезу автоматів необхідно розробити логічні рівняння схеми. Ураховуючи число станів автомата, необхідно визначити кількість трігерів, що забезпечують реалізацію цих станів. В даному випадку необхідно використати 4 трігера.

Далі будуємо

функціональну таблицю автомата. В лівій

частині розташований стовпець значень

вхідного сигналу автомата х, потім

показані стани автомата на тактах в

моент часу t

і в

момент часу t+1.Сигнал

YS1,YR1,

YS2,

YR2,

YS3,

YR3,

YS4

та YR4

відповідають

чотирьом використовуваним трігерам.

Їхні значення визначаються для кожного

рядка на підставі таблиці збудження

тригерів.

Далі будуємо

функціональну таблицю автомата. В лівій

частині розташований стовпець значень

вхідного сигналу автомата х, потім

показані стани автомата на тактах в

моент часу t

і в

момент часу t+1.Сигнал

YS1,YR1,

YS2,

YR2,

YS3,

YR3,

YS4

та YR4

відповідають

чотирьом використовуваним трігерам.

Їхні значення визначаються для кожного

рядка на підставі таблиці збудження

тригерів.

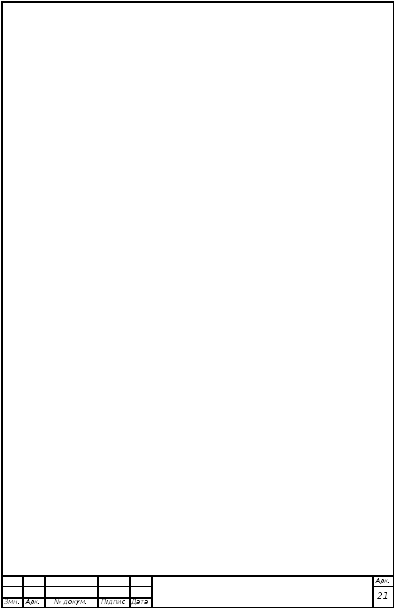

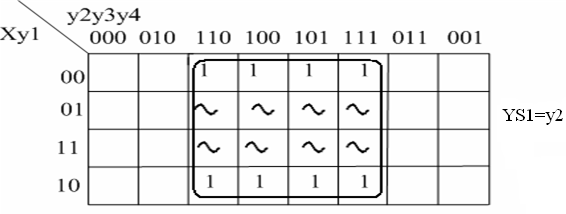

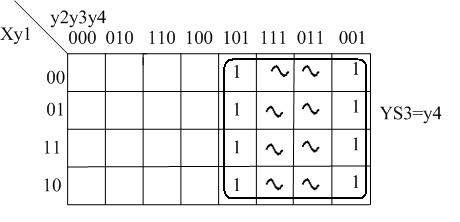

Для отримання виразів алгебри для функцій складемо відповідні карти Карно і проведемо мінімізації функцій.

Таблиця 3

|

|

T+1 |

|

|

|

|

|

|

|

| |||||||

|

X |

y1 |

y2 |

y3 |

y4 |

y1 |

y2 |

y3 |

y4 |

YS1 |

YR1 |

YS2 |

YR2 |

YS3 |

YR3 |

YS4 |

YR4 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

1 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

~ |

0 |

~ |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

~ |

0 |

~ |

1 |

0 |

~ |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

~ |

1 |

0 |

0 |

1 |

0 |

~ |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

~ |

1 |

0 |

~ |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

~ |

1 |

0 |

~ |

0 |

~ |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

~ |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

~ |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

~ |

0 |

0 |

1 |

0 |

~ |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

~ |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

~ |

0 |

~ |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

0 |

~ |

1 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

~ |

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

~ |

1 |

0 |

~ |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

~ |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

~ |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

~ |

0 |

~ |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

~ |

0 |

~ |

|

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

~ |

0 |

0 |

1 |

0 |

~ |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

~ |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

~ |

0 |

0 |

1 |

1 |

0 |

~ |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

~ |

0 |

~ |

0 |

0 |

1 |

0 |

~ |

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

~ |

0 |

~ |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

~ |

0 |

~ |

0 |

~ |

0 |

~ |

0 |

Рис2.1.1 Рис2.1.2

Рис2.1.3. Рис.2.1.4

Рис2.1.5 Рис2.1.6.

Рис.2.1.7 Рис.2.1.8.

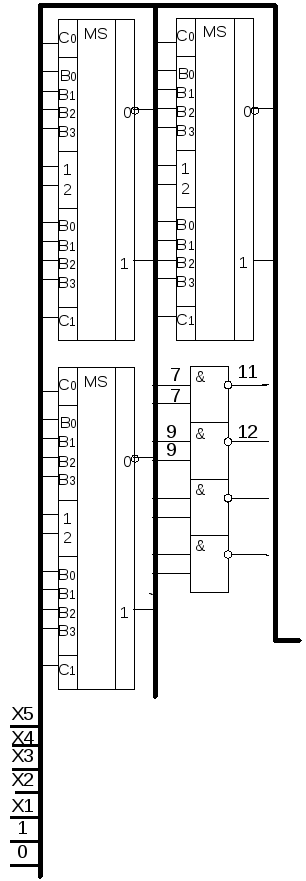

На четвертому етапі синтезу автомата здійснюється реалізація схеми автомата. З використанням елементів І-НЕ і RS – тригерів .

рис.2.1.9.

рис.2.1.9.